Федеральное агентство по образованию

Государственное образовательное учреждение высшего профессионального образования

Новгородский Государственный Университет имени Ярослава Мудрого

Кафедра Информационных технологий и систем

Отчет

Лабораторная работа №1

Вариант ХХ

«Синтез комбинационных схем»

по дисциплине

«Схемотехника ЭВМ»

Выполнил:

Студент группы 9092

______________Киреев Даниил Дмитриевич

«___»__________2012 г.

Проверил:

Преподаватель

_____________

«___»__________2012 г.

Задание

1.Ввести синтезированные схемы по п. 1, 2, 3, 4, 5 в САПР С ПОМОЩЬЮ ГРАФИЧЕСКИХ ПРИМИТИВОВ, А ТАКЖЕ ОПИСАНИЯ НА ЯЗЫКЕ VHDL. Результатом п.2 и п.4 должно стать получение мультиплексора, который необходимо использовать в п.3 и п.5.

Откомпилировать проект для заданной ПЛИС (EP3C10E144I7).

Провести исследование схемы в САПР.

Синтезировать MUX используя MegaWizard Plug-In Manager

В соответствии с п. 6 и 7 провести исследование схемы в САПР.

Сделать соответствующие выводы.

Оформить отчет. Отчёт должен содержать листинг всех программ, все схемы на графических примитивах, все временные диаграммы к каждому пункту задания и ВЫВОДЫ.

2. Решение

Индивидуальное задание –

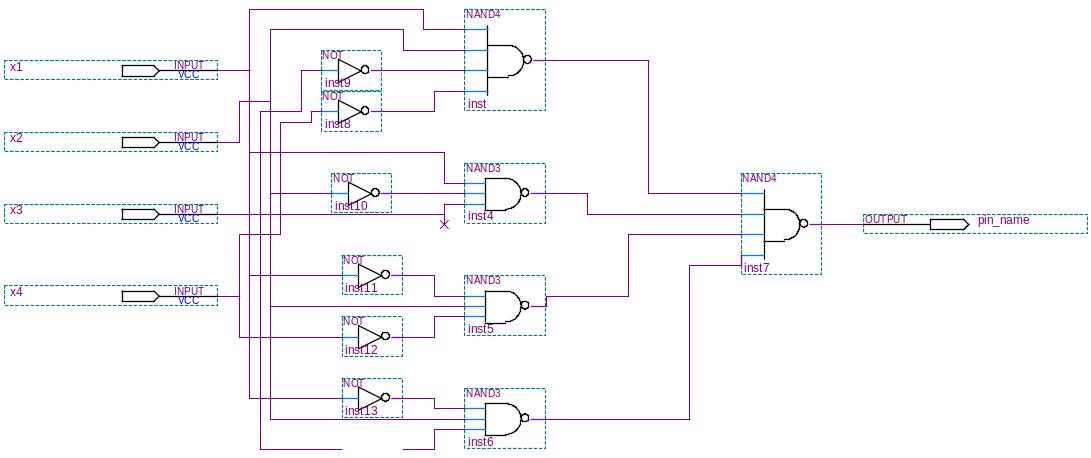

2.1 Схема и-не

Схема, синтезированная при помощи графических примитивов.

![]()

Описание на языке VHDL.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity comb2 is

port

(

x1 : in std_logic;

x2 : in std_logic;

x3 : in std_logic;

x4 : in std_logic;

y : out std_logic

);

end comb2;

architecture rtl of comb2 is

signal sig_x1:std_logic;

signal sig_x2:std_logic;

signal sig_x3:std_logic;

signal sig_x4:std_logic;

signal a:std_logic;

signal b:std_logic;

signal c:std_logic;

signal d:std_logic;

begin

sig_x1<=x1;

sig_x2<=x2;

sig_x3<=x3;

sig_x4<=x4;

a<=not (sig_x1 and sig_x2 and not (sig_x3) and not (sig_x4));

b<=not (sig_x1 and not (sig_x2) and sig_x3);

c<=not (sig_x2 and not (sig_x1) and not (sig_x4));

d<=not (sig_x2 and not (sig_x3) and not (sig_x1));

y<=not(a and b and c and d);

end rtl;

Результаты исследования схемы.

2.2 Схема или-не

![]()

Схема, синтезированная при помощи графических примитивов.

Описание на языке VHDL.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity comb2_2 is

port

(

x1 : in std_logic;

x2 : in std_logic;

x3 : in std_logic;

x4 : in std_logic;

y : out std_logic

);

end comb2_2;

architecture rtl of comb2_2 is

signal sig_x1:std_logic;

signal sig_x2:std_logic;

signal sig_x3:std_logic;

signal sig_x4:std_logic;

signal a:std_logic;

signal b:std_logic;

signal c:std_logic;

signal d:std_logic;

begin

sig_x1<=x1;

sig_x2<=x2;

sig_x3<=x3;

sig_x4<=x4;

a<=not(sig_x2 or not (sig_x1) or not(sig_x3));

b<=not(not(sig_x2) or not(sig_x1) or sig_x4 or sig_x3);

c<=not(sig_x1 or sig_x4 or not(sig_x2));

d<=not(sig_x1 or sig_x3 or not(sig_x2));

y<=not(a or b or c or d);

end rtl;

Результаты исследования схемы.

2.3 Схема 4-х канального мультиплексора

Схема, синтезированная при помощи графических примитивов.

Описание на языке VHDL.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity muxPro is

port (c, d, e, f: in std_logic;

s: in std_logic_vector(1 downto 0);

mux_out: out std_logic);

end muxPro;

architecture mux_impl of muxPro is

component mux4

port

(

x1 : IN STD_LOGIC ;

x2 : IN STD_LOGIC ;

x3 : IN STD_LOGIC ;

x4 : IN STD_LOGIC

);

end component;

begin

m : mux4 port map

(

c <= 0,

d <= x3,

e <= 1,

f <= (not(x3) and not(x4)),

s <= (x1 and x2)

);

process (s, c, d, e, f)

begin

case s is

when "00" => mux_out <= c;

when "01" => mux_out <= d;

when "10" => mux_out <= e;

when others => mux_out <= f;

end case;

end process ;

end mux_impl;

Описание на языке VHDL, создание при помощи MegaWizard Plug-In Manager

-- megafunction wizard: %LPM_MUX%

-- GENERATION: STANDARD

-- VERSION: WM1.0

-- MODULE: lpm_mux

-- ============================================================

-- File Name: mux4.vhd

-- Megafunction Name(s):

-- lpm_mux

--

-- Simulation Library Files(s):

-- lpm

-- ============================================================

-- ************************************************************

-- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

--

-- 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition

-- ************************************************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY lpm;

USE lpm.lpm_components.all;

ENTITY mux4 IS

PORT

(

data0 : IN STD_LOGIC ;

data1 : IN STD_LOGIC ;

data2 : IN STD_LOGIC ;

data3 : IN STD_LOGIC ;

sel : IN STD_LOGIC_VECTOR (1 DOWNTO 0);

result : OUT STD_LOGIC

);

END mux4;

ARCHITECTURE SYN OF mux4 IS

-- type STD_LOGIC_2D is array (NATURAL RANGE <>, NATURAL RANGE <>) of STD_LOGIC;

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (0 DOWNTO 0);

SIGNAL sub_wire1 : STD_LOGIC ;

SIGNAL sub_wire2 : STD_LOGIC ;

SIGNAL sub_wire3 : STD_LOGIC_2D (3 DOWNTO 0, 0 DOWNTO 0);

SIGNAL sub_wire4 : STD_LOGIC ;

SIGNAL sub_wire5 : STD_LOGIC ;

SIGNAL sub_wire6 : STD_LOGIC ;

BEGIN

sub_wire6 <= data0;

sub_wire5 <= data1;

sub_wire4 <= data2;

sub_wire1 <= sub_wire0(0);

result <= sub_wire1;

sub_wire2 <= data3;

sub_wire3(3, 0) <= sub_wire2;

sub_wire3(2, 0) <= sub_wire4;

sub_wire3(1, 0) <= sub_wire5;

sub_wire3(0, 0) <= sub_wire6;

lpm_mux_component : lpm_mux

GENERIC MAP (

lpm_size => 4,

lpm_type => "LPM_MUX",

lpm_width => 1,

lpm_widths => 2

)

PORT MAP (

sel => sel,

data => sub_wire3,

result => sub_wire0

);

END SYN;

-- ============================================================

-- CNX file retrieval info

-- ============================================================

-- Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone III"

-- Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "1"

-- Retrieval info: CONSTANT: LPM_SIZE NUMERIC "4"

-- Retrieval info: CONSTANT: LPM_TYPE STRING "LPM_MUX"

-- Retrieval info: CONSTANT: LPM_WIDTH NUMERIC "1"

-- Retrieval info: CONSTANT: LPM_WIDTHS NUMERIC "2"

-- Retrieval info: USED_PORT: data0 0 0 0 0 INPUT NODEFVAL data0

-- Retrieval info: USED_PORT: data1 0 0 0 0 INPUT NODEFVAL data1

-- Retrieval info: USED_PORT: data2 0 0 0 0 INPUT NODEFVAL data2

-- Retrieval info: USED_PORT: data3 0 0 0 0 INPUT NODEFVAL data3

-- Retrieval info: USED_PORT: result 0 0 0 0 OUTPUT NODEFVAL result

-- Retrieval info: USED_PORT: sel 0 0 2 0 INPUT NODEFVAL sel[1..0]

-- Retrieval info: CONNECT: result 0 0 0 0 @result 0 0 1 0

-- Retrieval info: CONNECT: @data 1 3 1 0 data3 0 0 0 0

-- Retrieval info: CONNECT: @data 1 2 1 0 data2 0 0 0 0

-- Retrieval info: CONNECT: @data 1 1 1 0 data1 0 0 0 0

-- Retrieval info: CONNECT: @data 1 0 1 0 data0 0 0 0 0

-- Retrieval info: CONNECT: @sel 0 0 2 0 sel 0 0 2 0

-- Retrieval info: LIBRARY: lpm lpm.lpm_components.all

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4.vhd TRUE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4.inc FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4.cmp TRUE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4.bsf FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4_inst.vhd FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux4_syn.v TRUE

-- Retrieval info: LIB_FILE: lpm

Результаты исследования схемы.