- •1. Основы логического проектирования.

- •Представление сигналов в цифровой технике и основные логические элементы.

- •1.1.3.Обозначение элементов, реализующих логические функции:

- •1.1.4. Основные параметры логических элементов.

- •Запрещённое значение сигналов:

- •1.2.Элементы логики.

- •1.2.1 Диодный элемент «или».

- •1.2.2 Диодный элемент «и».

- •1.2.3. Транзисторный элемент «не».

- •1.2.4. Логические элементы ттл – логики.

- •1.2.8. Логические элементы на моп – транзисторах.

- •1.2.6. Способы повышения быстродействия логических элементов.

- •1.2.9. Интегральные схемы инжекционной логики.

- •1.2.7. Сравнительная характеристика интегральных элементов

- •1.2.7. Эмиттерно-связанная логика.

- •2. Функциональные устройства цвм.

- •2.1. Шифраторы. Их синтез.

- •2.2. Дешифраторы.

- •2.3. Преобразователи кодов.

- •2.4. Мультиплексоры.

- •2.5. Демультиплексоры.

- •И демультиплексора

- •2.6. Цифровые компараторы.

- •2.7. Сумматоры одноразрядный двоичный сумматор.

- •Многоразрядные двоичные сумматоры.

- •Повышение быстродействия параллельных сумматоров.

- •Десятичные сумматоры.

- •3. Цифровые устройства.

- •3.1. Триггеры их назначение и типы.

- •Триггер выполнен на двух схемах или-не

- •2.3.2. Логическая структура rs – триггера

- •3.3. Двухступенчатый rs – триггер.

- •Синхронный rs – триггер.

- •3.5. Двухтактный rs – триггер.

- •3.7. Универсальный jk – триггер.

- •Условное обозначение d – триггера

- •3.9. Особенности интегральных триггеров.

- •3.10. Триггеры с динамическим управлением.

- •3.11. Асинхронный rs – триггер.

- •3.12. Одноступенчатый синхронный rs – триггер.

- •3.13. Триггер Шмитта.

- •4. Счётчики.

- •3.5.1.Счетчики основные понятия.

- •3.5.2 Счетчики с последовательным переносом.

- •4.3.Счетчики с параллельным переносом.

- •5. Делители частоты импульсной последовательности.

- •6. Запоминающие устройства.

- •6.1. Система памяти.

- •6.2. Основные параметры запоминающих устройств.

- •3.4. Запоминающее устройство с двух - координатной выборкой.

- •6.4. Обозначение сигналов выходов микросхем

- •6.5. Запоминающие элементы памяти.

- •6.6. Динамические элементы памяти.

- •6 .6.1. Постоянные запоминающие устройства.

- •6.6.2. Программируемые логические матрицы.

- •6.6.3. Схема микросхемы памяти с одно-координатной выборкой.

- •4. Цифро-аналоговые и аналого-цифровые преобразователи.

- •4.1.Аналого-цифровые преобразователи (ацп)

- •4.1.1. Ацп времяимпульсного типа.

- •7.3. Ацп последовательного счета.

- •7 .4. Кодоимпульсный ацп.

- •7.5. Цифро-аналоговые преобразователи (цап).

- •7.6. Цап с суммированием напряжения.

- •7.7. Схема преобразователя с суммированием напряжений на резисторной матрице.

- •7.8. Цифро-аналоговый преобразователь с суммированием тока.

- •8. Источники стабильного напряжения и стабильного тока.

- •8.1. Стабилизатор напряжения.

- •8.2. Стабилизатор тока.

- •9. Элементная база схемотехники.

- •9.1. Резисторы.

- •9.1.1. Классификация

- •9.1.2. Параметры резисторов.

- •Номинальное сопротивление по рядам

- •9.1.3. Полупроводниковые нелинейные резисторы.

- •9.2. Конденсаторы.

- •9.3. Система условных обозначений современных типов интегральных микросхем.

- •9.4. Система обозначения интегральных микросхем pro elektron.

- •Для одиночных микросхем:

- •Для семейств (серий) цифровых микросхем:

6.6. Динамические элементы памяти.

В режиме считывания вновь происходит выборка запоминающих элементов ячейки: адресная линия получает высокий потенциал, и ток открытого транзистора протекает по разрядной линии на один из входов усилителя считывания. На его выходе появляется логическая 1, если отперт VT2, и логический 0, если отперт VT1.

Микросхема на динамической памяти функции элементов памяти выполняют встроенные конденсаторы, которые выполнены внутри структуры микросхемы, т.к. информация, которая хранится в виде заряда конденсатора, теряется по мере разряда конденсатора необходимо периодически восстанавливать информацию (регенерация памяти), а сами микросхемы характеризуется временем цикла. Цикл восстановления исчисляется долями секунды.

6 .6.1. Постоянные запоминающие устройства.

Представляет собой матрицу с диодами, который через дешифратор адреса можно обратиться и считать информацию.

Р7 Р6 Р5 Р4 Р3 Р2 Р1 Р0

А0

А1

А2

А3

ПЗУ состоит из диодной матрицы и дешифратора адреса. Горизонтальные линии матрицы – адресные, вертикальные – разрядные, с них снимаются восьмиразрядные двоичные числа, записанные в ПЗУ. Код адреса возбуждает одну из адресных линий матрицы. Диоды в ней расположены так, чтобы обеспечить ее соединение с теми разрядными линиями, на которых нужно получить логические единицы.

Остановимся на перепрограммируемых ПЗУ (ЗПЗУ). Их элементы выполняются на основе МОП - транзисторов определенных структур. Одни из них допускают запись информации при воздействии импульса напряжения и ее стирания при ультрафиолетовом облучении, другие запись и стирание под воздействием только напряжения (разной полярности и величины).

6.6.2. Программируемые логические матрицы.

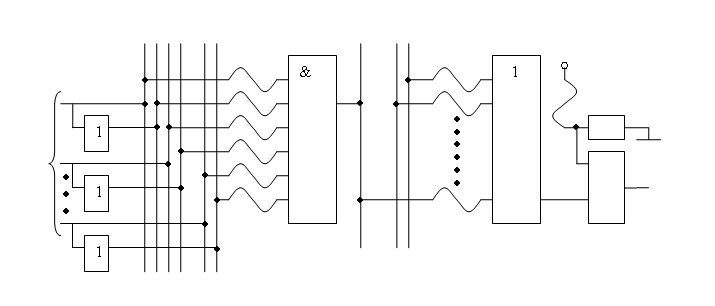

Программируемая логическая матрица при прожигании отдельных перемычек позволяет получить кодированную комбинацию сигналов из n – входных выходной код считывается с блоков сложение по модулю 2 (m2).

“1”

“1”

a1 z

a1 z

a2

m2

m

а3

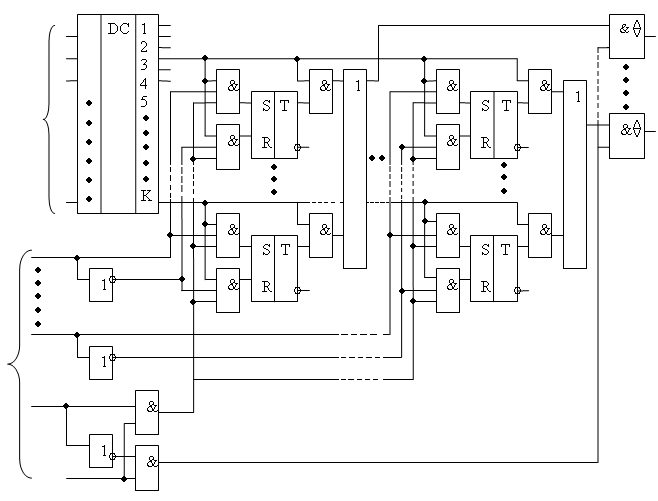

6.6.3. Схема микросхемы памяти с одно-координатной выборкой.

A0

A1 1-ый разряд К-ый разряд

A2

D0

D0

Dk

Внутренняя линия

W/R “Запись” (Зп)

Внутренняя лини

CS “Чтение” (Чт)

Выбор микросхемы памяти осуществляется подачей 1 на вход CS для того, чтобы записать W/R 1 кодированное слово подается на информационные входы D0…Dk адрес, по которому мы запишем слово в двоичном коде, поступает на вход дешифратора, который расшифровывает этот адрес и обращается к одному из выходов (например, к третьему). В этих условиях на внутренней линии запись появляется единичный сигнал, который поступает на вход элемента 3И перед триггерами и если на информационном входе на разрядах 1 эти 1 записываются в триггеры.