- •Методы измерения параметров импульсных сигналов Методы измерения параметров импульсных сигналов

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №1

- •Исследование логических элементов и, или, не

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №2

- •Виртуальная реализация лабораторной работы.

- •Проектирование комбинационных схем для заданной логической функции.

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №3

- •Виртуальная реализация лабораторной работы.

- •Исследование работы шифратора и дешифратора

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стенд №4

- •Исследование работы мультиплексора и демультиплексора.

- •«А» виртуальная реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №5

- •Исследование работы jk-триггера и проектирование на его основе rs-, d- и т- триггеров.

- •Стендовая реализация лабораторной работы.

- •Стенд №6

- •Универсальный регистр.

- •Методика исследования. Работа универсального регистра. «а» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Контрольные вопросы.

- •Стенд №7

- •Стендовая реализация лабораторной работы.

- •Контрольные вопросы.

- •Стенд №8

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №9

- •Исследование работы арифметико-логического устройства.

- •Стендовая реализация лабораторной работы.

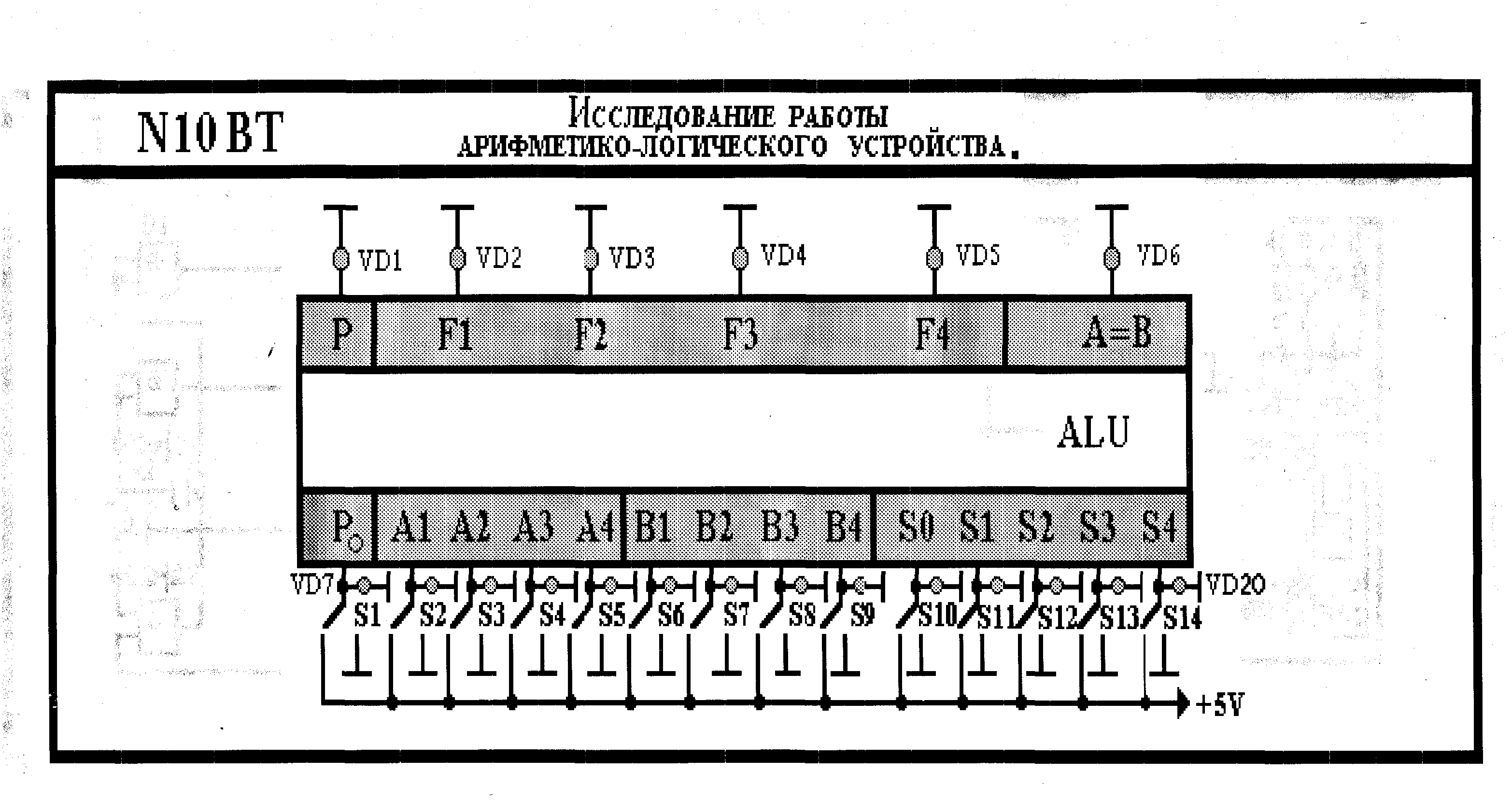

- •Стенд №10

- •Исследование микропроцессора.

- •«А» виртуальная реализация лабораторной работы

- •Стенд №11 Исследование работы микропроцессора

Стендовая реализация лабораторной работы.

Контрольные вопросы.

Каковы функции АЛУ?

Объясните принцип работы АЛУ.

Почему АЛУ является комбинационным устройством?

Зарисовать таблицу основных функций, реализуемых АЛУ.

Разобраться в ней.

Доказать правильность таблицы на основе полученных результатов на примере 3-4 произвольных чисел.

Приложение 1.

Краткое техническое описание стенда.

Стенд №10

Предполагаемый внешний вид:

Внешний вид установки:

Исследуемые схемы монтируются на печатных платах из фольгированного стеклотекстолита, которые укрепляются на алюминиевой (дюралюминиевой) основе размером 430 на 200 мм, закрытой сверху прозрачным пластиком.

Цветное изображение исследуемых схем, название работы, переключатели находится между металлической основой и защитным пластиком. Питание стендов осуществляется от имеющихся источников, встроенных в лабораторные столы.

Исследование микропроцессора.

Цель лабораторной работы:

Исследовать работу микропроцессора.

Теоретическое введение.

Отличительной особенностью комбинационной логики является то, что реализуемая ей функция определяется межэлементными соединениями (связями).

Изменение какой-либо функции сводится к изменению монтажной схемы. В связи с этим возникает вопрос, а нельзя ли создать такую монтажную схему, которая в один момент времени реализовывала бы функцию F(x), а в другой — F(y).

Сейчас имеется схема, которая в принципе может реализовать много функций и выполняет различные операции. Это центральный процессор (ЦП).

На его основе может быть создана вычислительная система, которую мы называем ЭВМ (компьютером). Обработка данных на ЭВМ осуществляется с помощью программ, состоящих из последовательности команд.

Сейчас выделяют три класса компьютеров:

a) большие компьютеры, которые обслуживают значительное число терминалов пользователей и периферийных устройств. Они применяются в больших системах обработки данных;

б) миникомпьютеры, которые обслуживают меньшее число терминалов пользователей (обычно до 40) и применяются в небольших фирмах, а также в промышленных системах управления;

в) микрокомпьютеры, рассчитанные на одного пользователя и широко применяются в бытовой, коммерческой и промышленной сферах.

Особенность микрокомпьютера заключается в том, что его центральный процессор (ЦП) выполнен в виде одной микросхемы, называемой микропроцессором. Центральный процессор занимает центральное место в структуре любой ЭВМ — это устройство, непосредственно осуществляющее обработку цифровой информации в соответствии с заданной программой. Для образования законченного микрокомпьютера к микропроцессору подключаются микросхемы памяти и ввода-вывода.

На рис. 1 показана общая архитектура всех типов компьютеров.

Центральный процессор (в случае микрокомпьютера МП), имеет 3 шины, связывающие все его компоненты. Выполняемая ЦП программа находится в памяти, которая в микрокомпьютерах состоит из 8-битных ячеек. Процессор поочередно считывает каждую команду из памяти, затем ее анализирует и исполняет. Последовательность выполнения каждой команды можно представить следующими тремя действиями:

ЦП выдает адрес следующей команду на шину адреса;

содержимое ячейки по указанному адресу появляется на шине данных; ЦП считывает команду и исполняет ее.

Сигналы, требующиеся для реализации указанных действий, передаются по шине управления.

Помимо команд программы в памяти компьютера хранятся значения переменных. Они могут быть числами (представленными в двоичной системе исчисления) или символами, которые легко вывести на экран дисплея или печатающее устройство.

В модуле ввода-вывода содержатся схемы, через которые происходит программами и данными с периферийными устройствами, например, внешней памятью (обычно дискетными накопителями), принтером и дисплеем (терминалом пользователя).

Начиная с конца 70-х и начала 80-х годов персональные компьютеры (микрокомпьютеры) начали пользоваться большой популярностью. В августе 1981 года фирмой IBM был выпущен персональный компьютер IBM PC, который в дальнейшем занял ведущее место на рынке по ряду причин: невысокой стоимости, простоты использования, высокими техническими возможностями. В первом компьютере фирмы IBM использовался 16-разрядный микропроцессор INTEL-8088 (8086 — его аналог). Это процессор явился родоначальником таких известных микропроцессоров как 80386, 80486, Pentium, используемых в современных компьютерах.

Рассмотрим принципы работы микропроцессора и его архитектуру.

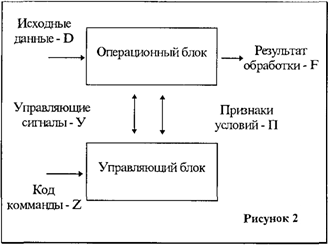

Как и любое устройство переработки информации, микропроцессор, можно разделить на 2 блока: операционный и управляющий (см. рис. 2).

Операционный блок

(ОБ) производит прием и хранение исходных данных, их преобразование и передачу результата обработки следующим устройствам. Кроме того, ОБ проверяет соответствие

результат обработки данных заранее обусловленным признаком и сообщает результаты проверки управляющему блоку.

Управляющий блок (УБ) вырабатывает управляющие сигналы, вид которых зависит от кода текущей операции и признаков результата выполнения предыдущей операции.

Процесс выполнения команды в ЭВМ растянут во времени и происходит за несколько машинных тактов. Например, в первый интервал производится прием и запоминание одного числа, во втором — другого, в третьем такте — нахождения суммы этих чисел и т.д. каждая из элементарных операций, выполняемых за один такт, называется микрооперацией. В один и тот же временной интервал (такт) различными элементами операционного блока может параллельно выполняться несколько микроопераций.

Таким образом, временная последовательность работы процессора определяется программой -> командой -> микрокомандой (микрооперациями). Интервал времени, за который выполняется микрокоманда, называется машинным тактом, а время, необходимое для выполнения команды — машинным циклом.

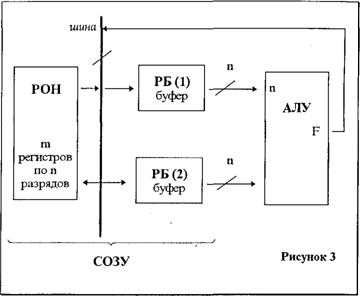

Оба блока (ОБ и УБ) состоят из комбинационных, и запоминающих устройств (ЗУ). ЗУ, входящие в состав процессора, выполнены в виде отдельных быстродействующих регистров и называются местной регистровой памятью. Скорость обращения к этим регистрам значительно больше, чем к основной памяти ЭВМ, поэтому местную память называют также сверхоперативным запоминающим устройством (СОЗУ).

Микропроцессор. Операционный блок.

Основой операционного блока (ОБ) микропроцессора является арифметико-логическое устройство (АЛУ), предназначенное для программируемой обработки информации. Оно имеет 2 группы входов данных (А,В) и 1 группу выходов данных (F) и под действием пяти управляющих сигналов S может выполнять 32 логические и арифметические операции над входными числами. Функции реализуемые АЛУ см. в таблице истинности АЛУ лабораторная работа №10.

Помимо АЛУ в состав ОБ (рис.3) входит часть СОЗУ, представленная группой регистров общего назначения (РОН) и буферными регистрами (РБ). Эти регистры имеют туже разрядность, что и АЛУ, и соединены в одну систему - операционный блок. При помощи общей поразрядной шины данных. В РОН хранятся числа, подлежащие обработке и результаты обработки.

Данный операционный блок может выполнять следующие микрокоманды:

- запись слова, находящегося на шине данных, в любой РОН или РБ;

- выборка слова из любого РОН на шину данных;

- выполнение одной из 32-х арифметико-логических операций над содержимым 2-х РБ и запись результата в любой свободный РОН.

Несмотря на большие функциональные возможности рассмотренного ОБ у него имеется и серьезные недостатки. В этом устройстве отсутствуют сигналы признаков результат (равенство результата нулю, отрицательный результат и тому подобное), что не позволит УБ организовать условные переходы при выполнении программы. Кроме того, в блоке не используется сигнал арифметического переноса Р из АЛУ, который может понадобиться при выполнении операций со словами удвоенной длины. И наконец, в рассмотренном ОБ достаточно трудно организовать часто встречающиеся операции поразрядного сдвига результата влево и вправо.

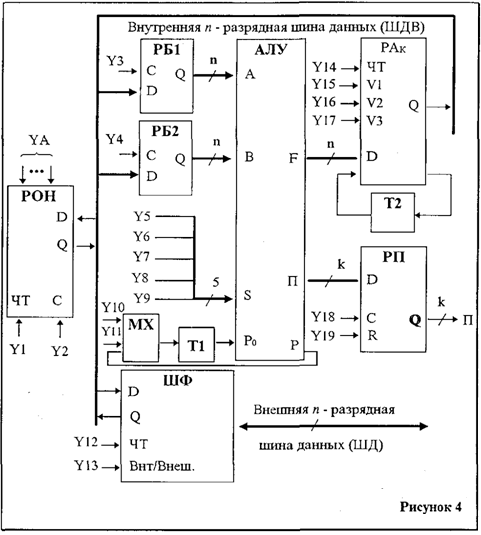

Схема

усовершенствованного с учетом предыдущих

замечаний ОБ представлена

на рисунке 4. В этом блоке реализована

цепь переноса

![]() с

запоминанием сигнала переноса на

триггере Т1. Y10

и Y11

управляют мультиплексором

MX,

подключающим к входу переноса АЛУ

различные сигналы. При У10=1 на вход Т1

подается сигнал переноса Р. При Y10=0

на вход Т1 подается сигнал Y11,

который может принимать значения 0 или

1 в

зависимости от необходимого режима

работы АЛУ.

с

запоминанием сигнала переноса на

триггере Т1. Y10

и Y11

управляют мультиплексором

MX,

подключающим к входу переноса АЛУ

различные сигналы. При У10=1 на вход Т1

подается сигнал переноса Р. При Y10=0

на вход Т1 подается сигнал Y11,

который может принимать значения 0 или

1 в

зависимости от необходимого режима

работы АЛУ.

Кроме того, в схеме применено модифицированное АЛУ которое помимо выполнения 32 операций проводит анализ результата на соответствие условленным логическим признакам (П). Результаты анализа поступают в регистр признаков (РП). Разрядность РП определяется числом логических условий. С увеличением числа логических условий облегчается процесс составления программ, так как у программиста появляются большие возможностей для изменения порядка выполнения команд программы по условному переходу.

Отметим, что включение регистра признаков в состав процессора и отличает подлинную вычислительную машину от простого калькулятора. В этом случае процессор сам принимает решение о том или ином продолжении вычислительного процесса в зависимости от полученного на предыдущем этапе результата, чего калькулятор делать не может.

Анализ результата арифметической операции проводится хотя бы по 3-м логическим условиям:

Нулевой результат. Признак "нулевой результат" принимает единичное значение, если во всех разрядах результата F окажутся нули.

Знак результата. Признак "знак результата" принимает единичное значение, если старший бит результата F становится равным 1.

Перенос — заем. Признак "перенос — заем" принимает единичное значение, если выполненная операция сопровождается появлением единицы на Р выходе АЛУ. Заем (отрицательный перенос) появляется только при вычитании большего числа из меньшего.

Значительно расширяет возможности операционного блока (рис. 4) использование универсального регистра, производящего параллельную запись п-разрядного слова и сдвиг его вправо или влево. Этот регистр называется регистром - аккумулятором (Рак), так как в нем накапливается результат выполнения операции АЛУ. К Рак подключен триггер Т2, который запоминает значение старшего и младшего разряда, "вытесненное" из Рак, при выполнении операции сдвига. Разрядность Рак обычно соответствует разрядности процессора, но в системах ориентированных на выполнение большого числа операций умножения, используют Рак двойной длины

Шинный формирователь (ШР), РОН, Рак — это три устройства, которые могут выставлять данные на общую внутреннюю шину. Все они имеют выходные каскады, позволяющие устройствам отключаться от общей шины при передаче соответствующих сигналов. Если управляющие сигналы Y1, Y12, Y14 = 0, то РОН, ШФ и Рак отключены от внутренней шины. При равенстве одного из этих сигналов единице происходит "чтение" (ЧТ) данных из соответствующего устройства на общую шину, по сигналу Y13 (внутренняя/ внешняя) меняется направление передачи данных ШФ.

При обращении блока управления к РОН выборка регистра с заданным адресом производится по коду адреса YA нужного регистра. Разрядность адресных сигналов YA определяется числом РОН.

Управляющие сигналы Y5... Y9 определяют тип операции АЛУ.

Регистры РОН, РБ1, РБ2 и РП производят параллельную запись многоразрядных слов с информационных входов Д по приходу управляющих сигналов на вход С. Такими сигналами являются Y2, Y3, Y4 и Y18. По сигналу Y19 происходит очистка, то есть заполнение нулями всех разрядов регистра признаков.

Регистр аккумулятора может работать водном из пяти режимов (см. таблицу 1), выбор которых осуществляется сигналами Y15... Y17.

Таблица 1

Управляющий сигнал |

Режим работы |

||

Y15 |

Y16 |

Y17 |

|

1 |

X |

X |

Запись информации с входов D. Значения Y16 и Y17 любые. |

0 |

0 |

0 |

В освобождающуюся ячейку записывается информация вытесняемая из регистра в этом же такте (Т2 не используется) при правом сдвиге. |

0 |

0 |

1 |

В освобождающуюся ячейку записывается информация вытесняемая из регистра в этом же такте (Т2 не используется) при левом сдвиге. |

0 |

1 |

0 |

В освобождающуюся ячейку записывается информация вытесняемая из триггера Т2, то есть вытесняемая из регистра в предыдущем такте при правом сдвиге. |

0 |

1 |

1 |

В освобождающуюся ячейку записывается информация вытесняемая из триггера Т2, то есть вытесняемая из регистра в предыдущем такте припевом сдвиге. |

Рассмотренный операционный блок позволяет выполнять любую логическую или арифметическую обработку данных, поступающих на общую шину. Выполняемые операции будут определяться последовательностью управляющих сигналов, формируемых в управляющем блоке.

Управляющий блок микропроцессора выполняет 2 основные функции:

производит выборку команд программы в необходимом порядке из внешнего ЗУ; дешифрует выбранную команду и управляет выполнением микроопераций и микрокоманд в течении одного машинного цикла.

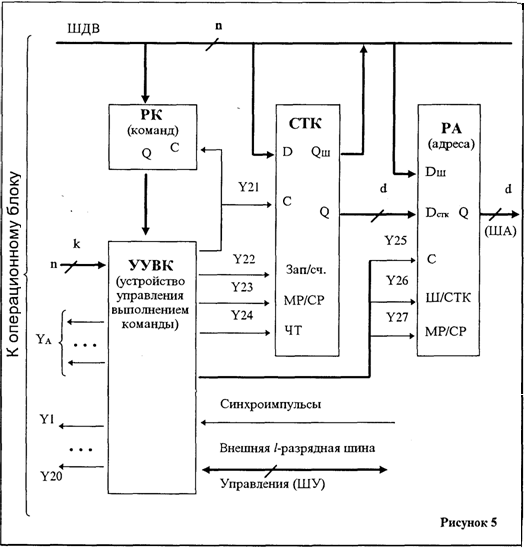

Для выполнения перечисленных функций в состав управляющего блока (рис.5) входят следующие аппаратные средства: счетчик команд (СТК), регистр адреса (РА), регистр команд (РК) и устройство управления выполнением команды (УУВК).

Обрабатываемые данные и программы загружаются пользователем в основную память — ЗУ, которая является внешним по отношению к микропроцессору устройством.

Микропроцессор. Управляющий блок (УБ).

Данные из внешних устройств поступают на внутреннюю шину микропроцессора через ШФ в виде п-разрядных слов. Для выборки необходимы команды, микропроцессор должен обратиться к конкретной ячейке ЗУ, выставив на адресных входах ЗУ код этой ячейки. Эту операцию выполняет РА, к входам которого подключена адресная шина. Так как данные и фрагменты программ могут храниться в любом месте ЗУ, то РА памяти должен иметь разрядность, не меньшую адресной разрядности ЗУ. Поэтому в большинстве микропроцессоров разрядность РА больше длины слова данных. Например, в наиболее распространенных 8-разрядных микропроцессорах используется двухбайтовая адресная шина, позволяющая обращаться к 65536 ячейкам ЗУ.

Номер ячейки памяти, к который требуется обращение, может находиться в различных узлах процессора. Поэтому при выборке данных из ЗУ адрес ячейки выставляется на шину данных и с нее переписывается в РА по управляющему сигналу Y25 (вход С регистра). При этом другой управляющий сигнал — У26 (Ш/СТК) — устанавливает регистр в режим приема информации с шины (Ш), а не со счетчика (СТК). Так как разрядность шины данных меньше разрядности адреса, то запись адреса производится за 2 такта: сначала младшие разряды, затем старшие (по управляющему сигналу Y27 "МП/СР").

Адрес ячейки ЗУ, в которой находится команда, вырабатывается счетчиком команд СТК, многоразрядный вход которого соединен на прямую с входом РА. Поэтому при выборке команд из ЗУ регистр адреса переводит в режим приема информации от счетчика (сигнал Y26) и сигналом У25 переписывает содержимое СТК в РК.

Счетчик команд определяет очередность выборки команд из ЗУ. Команды в программе располагаются одна за другой в определенном порядке. Обычно каждая следующая команда имеет адрес на 1 больший адреса предыдущей команды. Однако в случае ветвления программы или перехода к подпрограмме возникает необходимость обратиться к новому адресу, значительно отличающемуся от предыдущего. Таким образом, СТК должен уметь подсчитывать количество сделанных шагов (выполненных команд) начиная с любого исходного адреса. В начале работы микропроцессора (по сигналу начальной установки) или в процессе работы (по командам условных и безусловных переходов) на внутренней шине данных выставляется некий исходный адрес начала нового фрагмента программы. Этот адрес поступает на входе параллельной записи СТК и по управляющему сигналу Y22 (режим "Запись с входов") записывается в СТК. Так как разрядность шины данных меньше разрядности адреса, то запись исходного адреса происходит за 2 такта (так же как в РА). Затем СТК сигналом У22 переводится в режим "счет импульсов с входа С" (СЧ) и последовательно подсчитывает количество выполненных команд в данном фрагменте программы. Отметим, что СТК имеет возможность передать адрес команды не только в РА, но и в шину данных (режим "чтение ", сигнал У24 и выход Qш), что позволяет использовать некоторые дополнительные способы адресации ЗУ.

Регистр команд (РК) предназначен для хранения кода выполняемой команды. Сменить информацию в этом регистре можно только после выполнения всех микрокоманд, составляющих текущую команду. Разрядность зависит от числа команд, выполняемых МП. Так как обычно число команд не превышает 200, то длина слова регистра команд не превышает байта (28=256 состояний).

Рассмотрим, как протекает процесс выборки из ЗУ адреса команды после включения МП. Первый этап. Исходный адрес устанавливается на шине данных и переписывается в СТК.

Второй этап. С выхода СТК адрес переписывается а РА и по внешней адресной шине поступает на ЗУ.

Третий этап. По заданному адресу из ЗУ считывается необходимая команда и через шинный формирователь ШФ поступает в МП на внутреннюю шину данных.

Четвертый этап. С шины данных команда по сигналу У21

переписывается в РК. Этот же сигнал увеличивает на 1 адрес команды,

формируемой в СТК.

На этом заканчивается процесс выборки команды из ЗУ, называемый подциклом выборки, и МП переходит ко второму подциклу: выполнению команды. В течении второй части машинного цикла операционный блок (под действием сигнала управления) выполняет все необходимые микрокоманды. Если при этом операционному блоку понадобятся какие-либо данные из ЗУ, то ОБ может воспользоваться РА (через шину данных) и выставить на адресной шине код необходимой ячейки ЗУ. Еще раз отметим, что такое обращение к РА не изменило содержимого РК и СТК и, следовательно, не нарушает выполнение текущей команды и порядок следования команд.

После завершения всех операций текущей команды начинается новый цикл. При этом второй и все следующие подциклы выборки будут короче первого, так как они начнутся со второго этапа: записи в РК адреса, подготовленного СТК во время второй части предыдущего цикла.

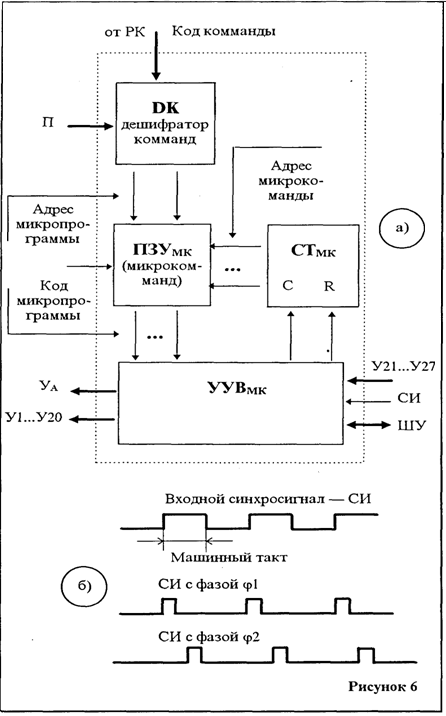

После выборки команды из ЗУ она поступает в устройство управления выполнением команды УУВК (рис. 6а). Устройство управления предназначено для организации необходимой последовательности действий всех остальных узлов МП. УУВК состоит из дешифратора команд DK, устройства памяти микрокоманд ПЗУМК, счетчика микрокоманд СТМК и устройства управления выполнением микрокоманд УУВМК.

Дешифратор команд DK расшифровывает код команды с учетом признаков П выполнения логических условий в предыдущем машинном цикле (при выполнении предыдущей команды).

Преобразованный многоразрядный код команды поступает в ПЗУмк, в котором хранятся микропрограммы выполнения всех команд. Выбор необходимой микропрограммы осуществляется кодом, поступающим от DK, а пошаговая исполнение микропрограммы управляется счетчиком микрокоманд. СТмк получает единичное приращение после выполнения очередной микрооперации и обнуляется при окончании последнего машинного такта, заданного кодом команды.

Устройство управления выполнением микрокоманд УУВмк формирует последовательность сигналов, управляющих микрооперациями, необходимыми для выполнения данной микрокоманды. Эта последовательность формируется в пределах одного машинного такта и обычно является многофазной (2...4 фазы). Временные границы такта и фазы управляющих сигналов задаются синхроимпульсами (СИ), которые или генерируются внутри УУВК, или поступают от внешнего генератора синхросигналов. Пример образования двухфазной последовательности СИ показан на рисунке 66. Благодаря многофазности синхросигналов в одном такте МП может совершаться несколько последовательных групп событий.

Схемотехнически УУВмк представляет собой набор формирователей управляющих сигналов, фазы и длительность которых согласованы с СИ. Количество формирователей определяется числом управляющих сигналов, выходящих из УУВмк. Разрешение на работу того или иного формирователя в данном такте поступает от ПЗУмк в виде кода микрокоманды.

Хранение микропрограмм в специальном ПЗУ позволяет вносить изменения в систему команд МП и на основе одной и той же базовой БИС получать специализированные устройства обработки данных, ориентированные на выполнение различных задач. Чтобы представить такую возможность не только разработчику, но и пользователю МП, устройство памяти можно выполнять в виде перепрограммируемого ПЗУ. Такое ППЗУ выстраивается в БИС МП и дает возможность потребителю записать в него необходимую систему команд. Если же специализация МП не требуется и система команд жестко определена разработчиком, то ПЗУмк можно заменить дешифратором микрокоманд Dмк. Такая замена усложняет структуру УУВмк, но увеличивает быстродействие МП. В современных МП применяются оба способа построения УУВК как с микропрограммным ЗУ, так и с жесткой логикой.

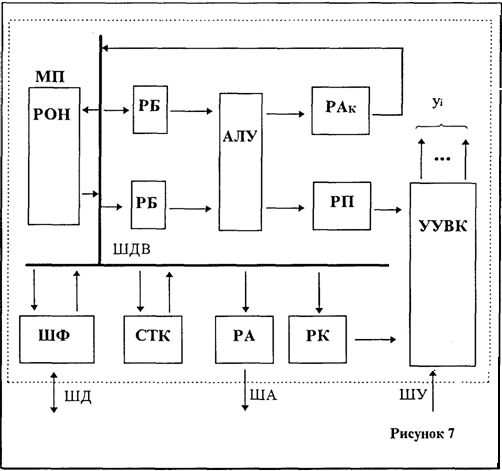

Микропроцессор. Обобщенная структурная схема.

Рассмотренные выше функциональные и структурные особенности

операционного и управляющего блоков МП позволяют составить обобщенную структурную схему, представленную на рисунке 7. Основой ее является общая внутренняя шина данных (ШДВ), соединяющая все элементы операционного блока (на схеме расположены выше ШДВ) и элементы управляющего блока ((на схеме расположены ниже ШДВ). Шинный формирователь (ШФ), связывающий внутреннюю шину данных с

внешней (ШД), является общим элементом как для операционного, так и для управляющего блоков.

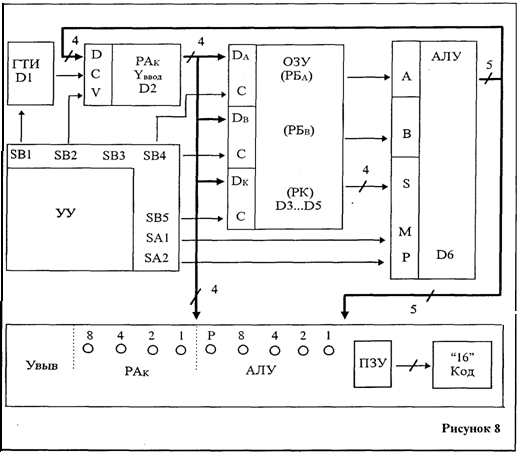

Рассмотрим принцип работы простейшей модели микропроцессора. Она содержит в упрощенном виде основные блоки микропроцессора (см. рис 8):

операционный блок

арифметико-логическое устройство АЛУ (D6);

оперативное запоминающее устройство ОЗУ (D3, D4, D5);

регистр-аккумулятор РАк (D2);

2) управляющий блок

• переключатели SA1, SA2, SB1, SB2, SB3, SB4, SB5.

Для работы микропроцессора необходимо устройство ввода-вывода информации:

1) устройство ввода информации

генератор тактовых импульсов (D1);

счетчик (D2);

блок из 4-х светодиодов;

2) устройство вывода информации

дешифратор (D7);

семисегментный индикатор HL1;

блок из 5-ти светодиодов.

Принцип работы АЛУ был рассмотрен в лабораторной работе №10, напомним лишь, что при подаче на вход М высокого уровня напряжения АЛУ выполняет логические операции, при подаче на вход М низкого уровня — арифметические. Если на вход Р0 подан низкий уровень напряжения, то АЛУ учитывает сигнал переноса, если высокий уровень — то не учитывает сигнал переноса.

ОЗУ состоит из трех четырехразрядных регистров: РБА (D3) — регистр операнда А, РБВ (D4) — регистр операнда В, РК (D5) — регистр

кода команд.

В схеме имеется регистр-аккумулятор РАк, накапливающий результат выполнения операций блоком АЛУ. Этот же регистр аккумулятор (счетчик) используется для ввода информации (операндов и команд) в микропроцессор.

Для уменьшения количества органов управления информация вводится в последовательном коде.

В приложении 2 приведена принципиальная схема модели. При нажатии кнопки SB1 (ввод) разрешается работа генератора тактовых импульсов (D1). Тактовые импульсы поступают на счетный вход четырехразрядного двоичного счетчика (D2), на выходе которого появляется двоичный код (восемь, четыре, два, один) числа введенных импульсов. По четырехразрядной шине эта информация поступает на информационные входы всех регистров ОЗУ и на Увыв (устройство вывода), где преобразуется в оптическую информацию блоком из четырех светодиодов HL1 ... HL4. С помощью SB2 ... SB5 осуществляется запись информации с выхода счетчика D2 в любой из регистров ОЗУ. Таким образом, за три последовательных цикла нажатия на кнопки SB1 и SB2, SB1 и SB4, SB1 и SB5. Мы записываем в ОЗУ коды всех операндов и операции обработки. Заносимая информация каждый раз контролируется по светодиодным индикаторам HL1 — HL4. В зависимости от кода команды, подаваемой с РК и управляющих сигналов М и Р0, АЛУ выполняет одну из 32 логико-арифметических операций. Результат выполнения операции высвечивается в двоичном коде на светодиодном пятиразрядном индикаторе Н15... Н19. Кроме того, этот же результат, преобразованный дешифратором в шестнадцатеричный код, высвечивается в виде стилизованных изображений на семисегментном индикаторе. Результат выполнения первой команды может быть переписан в регистр аккумулятор (по нажатию кнопки SB2) и вновь подан на АЛУ уже в качестве нового операнда для выполнения следующего цикла вычислений.

В качестве РАК используется тот же счетчик D2, что и в устройстве ввода информации. Совмещение функций возможно благодаря управляющему входу V, при V=1 (SB2 отжата) микросхема работает в режиме последовательного счета импульсов, поступающих на вход С. При V=0 (SB2 нажата) ИМС работает как регистр с параллельной записью информации с входов D0 ... D3.

Для перевода чисел из одной системы исчисления в другую приводим следующую таблицу (таблица 2).

Таблица 2.

Число в двоичной системе исчисления |

Число в десятичной системе исчисления |

Число в шестнадца-теричной системе исчисления |

0 |

0 |

0 |

1 |

1 |

1 |

10 |

2 |

2 |

11 |

3 |

3 |

100 |

4 |

4 |

101 |

5 |

5 |

110 |

6 |

6 |

111 |

7 |

7 |

1000 |

8 |

8 |

1001 |

9 |

9 |

1010 |

10 |

A |

1011 |

11 |

B |

1100 |

12 |

C |

1101 |

13 |

D |

1110 |

14 |

E |

1111 |

15 |

F |

Методика исследования.