- •Методы измерения параметров импульсных сигналов Методы измерения параметров импульсных сигналов

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №1

- •Исследование логических элементов и, или, не

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №2

- •Виртуальная реализация лабораторной работы.

- •Проектирование комбинационных схем для заданной логической функции.

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №3

- •Виртуальная реализация лабораторной работы.

- •Исследование работы шифратора и дешифратора

- •«А» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стенд №4

- •Исследование работы мультиплексора и демультиплексора.

- •«А» виртуальная реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №5

- •Исследование работы jk-триггера и проектирование на его основе rs-, d- и т- триггеров.

- •Стендовая реализация лабораторной работы.

- •Стенд №6

- •Универсальный регистр.

- •Методика исследования. Работа универсального регистра. «а» виртуальная реализация лабораторной работы

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Контрольные вопросы.

- •Стенд №7

- •Стендовая реализация лабораторной работы.

- •Контрольные вопросы.

- •Стенд №8

- •«Б» стендовая реализация лабораторной работы

- •Стендовая реализация лабораторной работы.

- •Стенд №9

- •Исследование работы арифметико-логического устройства.

- •Стендовая реализация лабораторной работы.

- •Стенд №10

- •Исследование микропроцессора.

- •«А» виртуальная реализация лабораторной работы

- •Стенд №11 Исследование работы микропроцессора

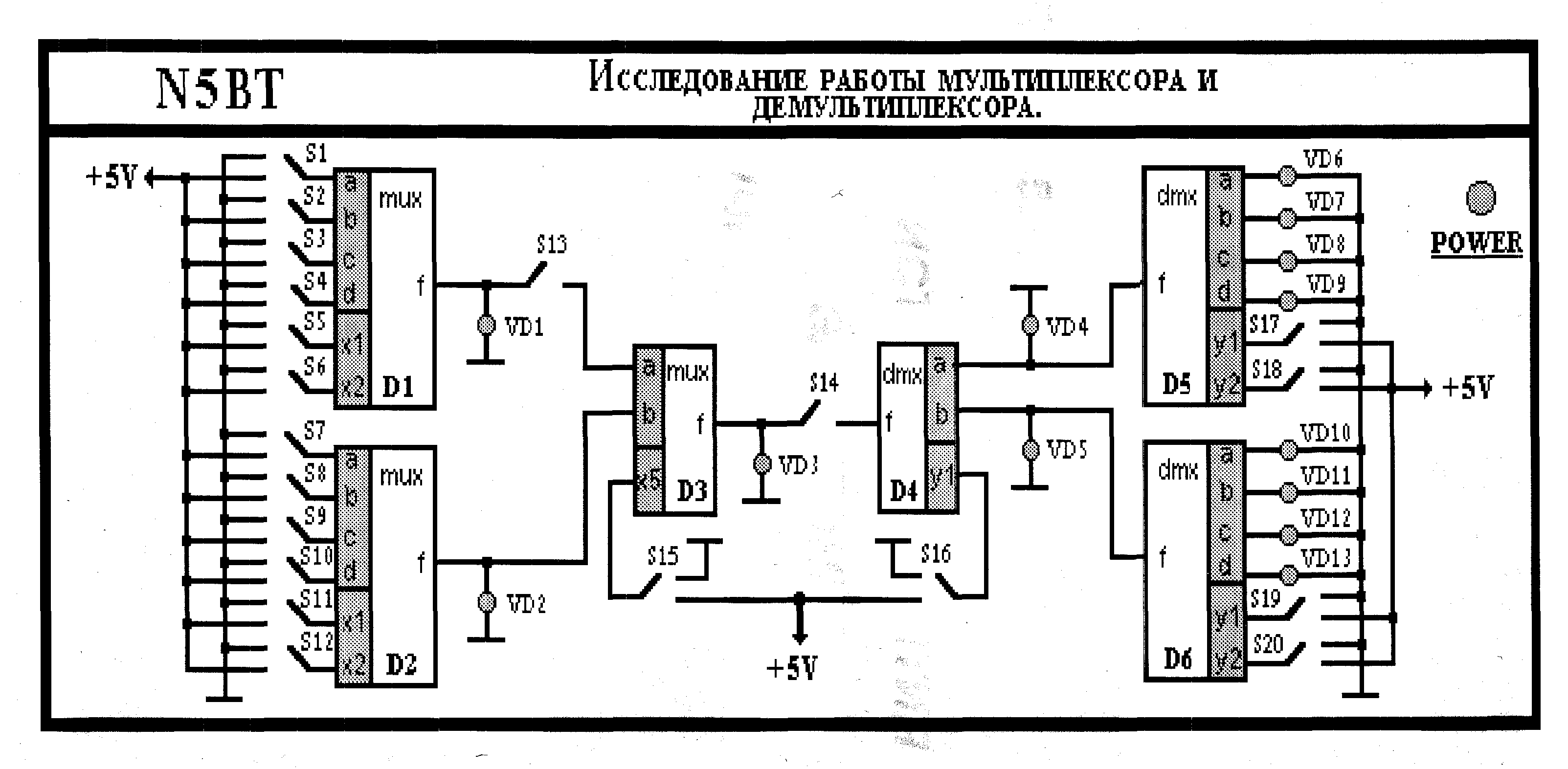

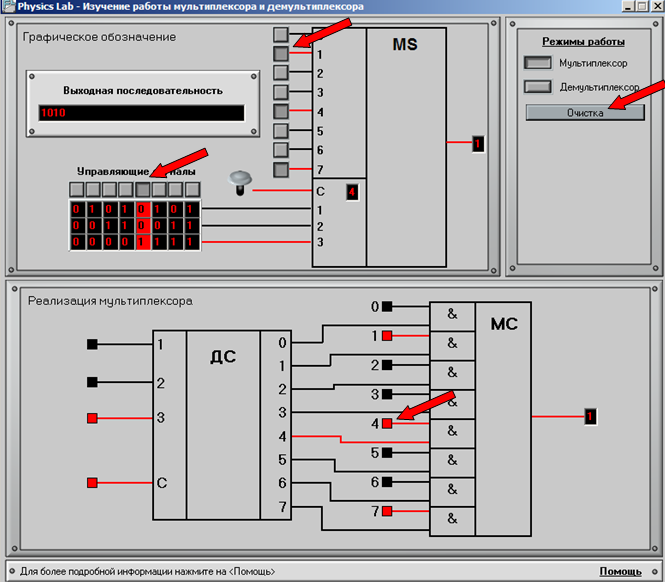

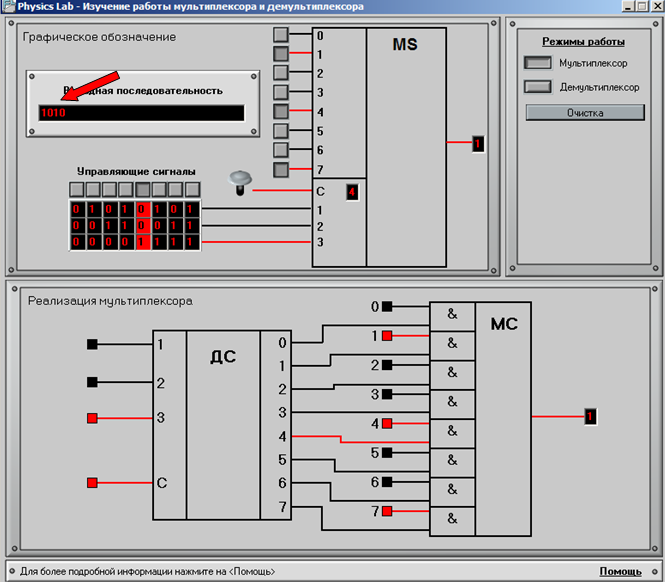

Стенд №5

Предполагаемый внешний вид:

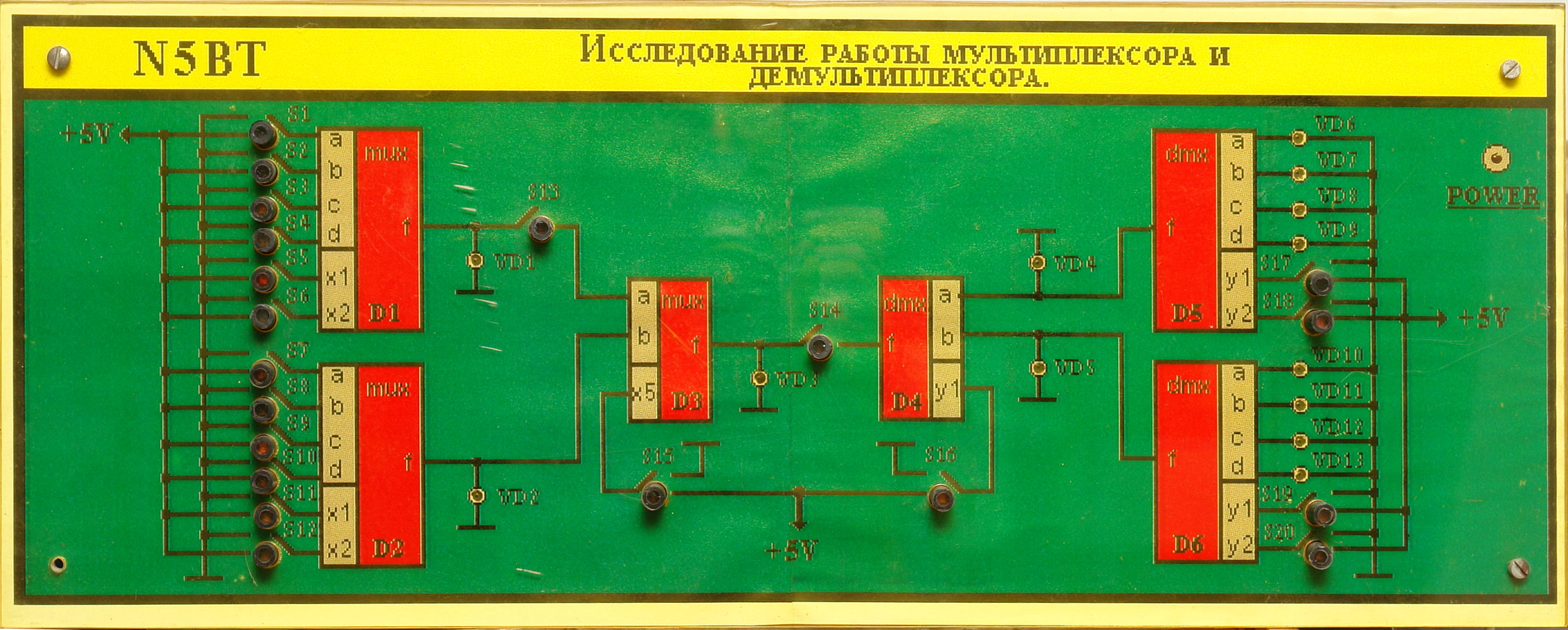

Внешний вид установки:

Исследуемые схемы монтируются на печатных платах из фольгированного стеклотекстолита, которые укрепляются на алюминиевой (дюралюминиевой) основе размером 430 на 200 мм, закрытой сверху прозрачным пластиком.

Цветное изображение исследуемых схем, название работы, переключатели находится между металлической основой и защитным пластиком. Питание стендов осуществляется от имеющихся источников, встроенных в лабораторные столы.

Приложение 2.

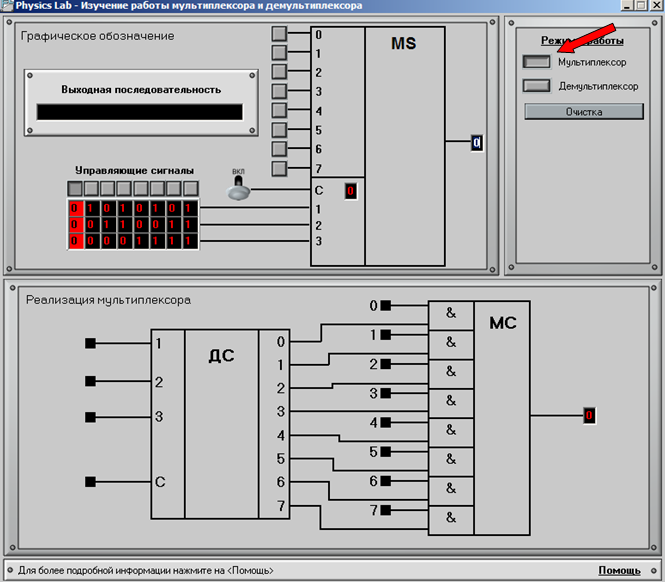

Шаг 1

Необходимо выбрать необходимый режим работы. В программе представлены два режима работы: «мультиплексор и демультиплексор».

Шаг 2

Рабочая область программы представлена двумя частями: Графическое обозначение и реализация. В части «Графическое обозначение» необходимо подать напряжение на вход «С».

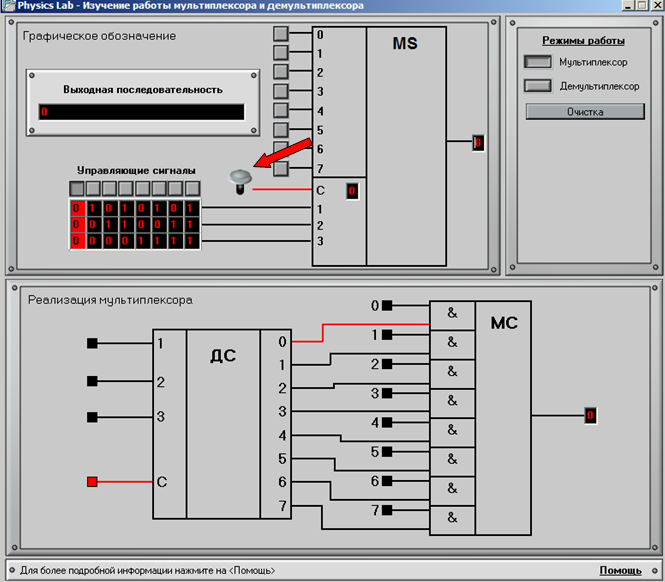

Шаг 3

Подавая напряжение на входы и изменяя управляющие сигналы, наблюдаем работу элемента. Красными линиями отображается прохождение сигнала. Кнопка «Очистить» позволяет привести элемент в исходное состояние.

Шаг 4

Последовательность выходящих сигналов можно наблюдать в окне «Выходная последовательность».

Исследование работы jk-триггера и проектирование на его основе rs-, d- и т- триггеров.

Цель лабораторной работы:

1. установить – как зависит выходное напряжение от напряжений, подаваемых на входа триггера. Для этого подавая на вход JK-триггера (RS, D, и T и т.д. триггеров, собранных на его основе) напряжения соответствующего логическому 0 или логической 1, измерить напряжение на выходе схемы, соответствующее логическому 0 или 1.

Методическая цель состоит в том, чтобы студент в результате выполнения работы:

1. Изучение структуры и алгоритмов работы асинхронных и синхронных триггеров.

2. Исследование функций переходов и возбуждения основных типов триггеров.

3. Изучение взаимозаменяемости триггеров различных типов.

Теоретическое введение.

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики описывающий работу цифровых автоматов обладающих памятью называется последователь-ностной логикой. Основным элементом последовательностной логики является триггерный элемент памяти, или просто триггер.

Триггер — цифровой автомат, имеющий два устойчивых состояния. Одному из этих состояний присваивается значение 1, а другому 0. Триггер длительное время может находиться в одном из двух возможных устойчивых состояний (хранение информации), а под воздействием внешних сигналов скачком переключаться в другое (запись информации). Триггер имеет два выхода прямой Q и инверсный

![]() .

Число входов триггера зависит от

выполняемых им функций. В цифровой

технике приняты следующие обозначения

входов триггеров. S

— раздельный вход установки триггера

в единичное состояние

.

Число входов триггера зависит от

выполняемых им функций. В цифровой

технике приняты следующие обозначения

входов триггеров. S

— раздельный вход установки триггера

в единичное состояние

(Q =1, = 0).

R — раздельный вход установки триггера в нулевое состояние (Q=0, = 1).

D — информационный вход.

С — вход синхронизации.

Т— счетный вход.

E(v)—управляющий вход.

J —раздельный вход установки универсального триггера в единичное состояние (0=1, = 0).

К — раздельный вход установки универсального триггера в нулевое состояние.

Триггеры классифицируются по ряду признаков:

1)по типу входов различают RS -, Т-, D -, JK - триггеры;

2)по способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах изменение его состояния происходит непосредственно с приходом сигнала на информационный вход. В синхронных триггерах кроме информационных входов имеются входы синхронизации (тактовые входы). Такой триггер будет изменять свое состояние лишь при подаче разрешающих сигналов на вход синхронизации. Если же на вход синхронизации (С) разрешающий сигнал не подан, то даже при наличии на входах информационных сигналов триггер не будет изменять свое состояние;

3)по способу управления информации различают триггеры со статическим, динамическим, одноступен-чатым и многоступенчатым управлением.

При статическом управлении переключение триггеров вызывается уровнями сигналов, поступающих на информационные входы, при динамическом управлении — изменением уровней сигналов на информационных входах. Триггеры с одноступенчатым управлением имеют одну ступень, а с двухступенчатым — две ступени запоминания информации. Синхронные триггеры с одноступенчатым запоминанием информации называются однотактовыми, а с двухступенчатым-двухтактными.

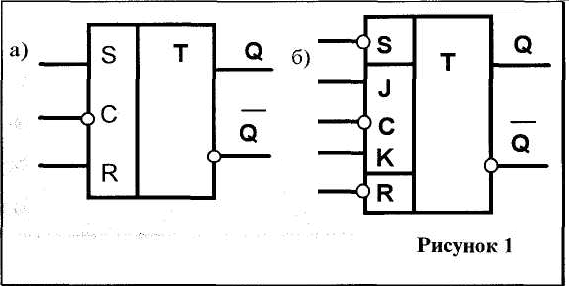

Триггер обозначают в виде прямоугольника, имеющего основное и дополнительное поля. Внутри основного поля пишется буква Т или ТТ, если триггер двухступенчатый. Внутри дополнительных полей записываются буквы, характеризующие входы триггера. Синхронизируемые триггеры a) RS - триггер, б) JK - триггеры.

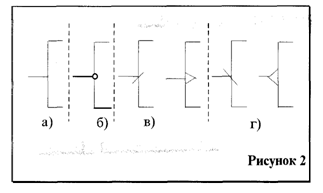

В схемотехнике приняты следующие обозначения входов последовательных элементов.

Обозначение входов последовательных элементов.

Рис 2а — прямой статический вход, т.е. для записи информации в триггер нужно чтобы на входе синхронизации присутствовал уровень 1Т.

Рис. 2б - инверсный статический вход, т, е. для записи информации в триггер нужно, чтобы на входе синхронизации С присутствовал уровень 0.

S |

R |

Qt+1 |

|

ВЫПОЛНЯЕМАЯ |

0 |

0 |

t |

|

хранение |

1 |

0 |

1 |

0 |

запись 1 |

0 |

1 |

0 |

1 |

запись 0 |

1 |

1 |

X |

X |

неопределенное |

Таблица 1.

Рис 2г — инверсный динамический вход, переключение триггера в новое состояние происходит тогда, когда на вход С подан отрицательный перепад напряжений (перепад от уровня 1 к уровню 0).

Рисунок 3. Таблица истинности асинхронного RS-триггера

Асинхронный RS - триггер устройство, имеющее два информационных входа R и S. В нём возможны два устойчивых состояния. Работу асинхронного RS - триггера как и любого другого триггера можно описать с помощь таблицы переходов, (таблиц истинности). Если обозначить Qt - состояние триггера на выходе до поступления информационных сигналов, (состояние в момент времени t), a Q - состояние триггера на выходе после поступления информационных сигналов на вход. То таблица переходов для асинхронного RS - триггера будет выглядеть следующим образом.

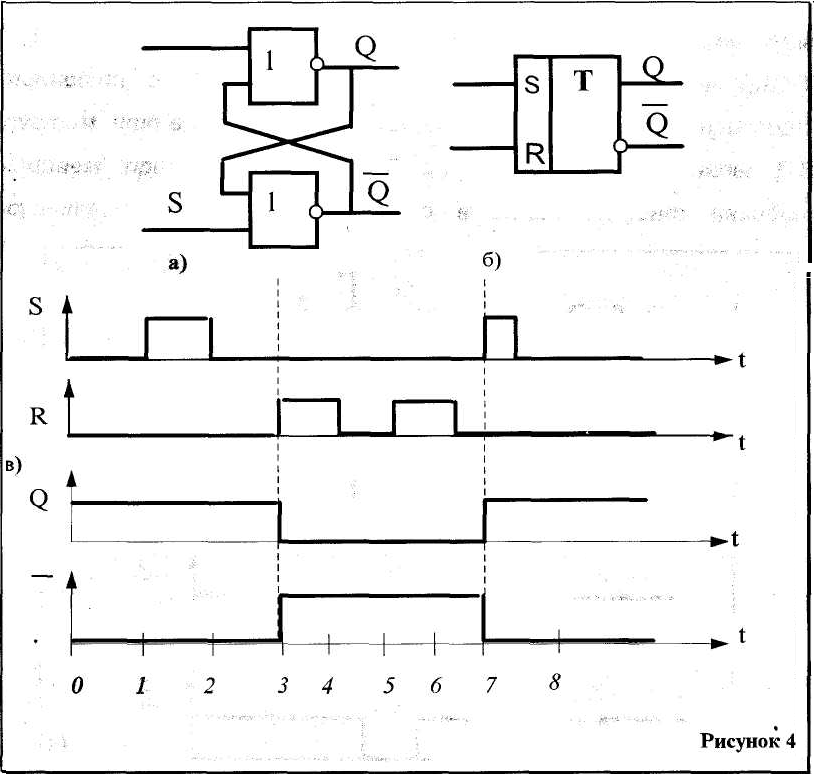

Асинхронный RS - триггер может быть построен на двух логических элементах ИЛИ - НЕ, либо И - НЕ (рис 4). Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента, поэтому триггер может учитывать предшествующее состояние, т. е. является автоматом с памятью.

Асинхронный RS - триггер на ЛЭ ИЛИ - НЕ:

а) - его функциональная схема;

б) - условное обозначение;

в) - временные диаграммы работ.

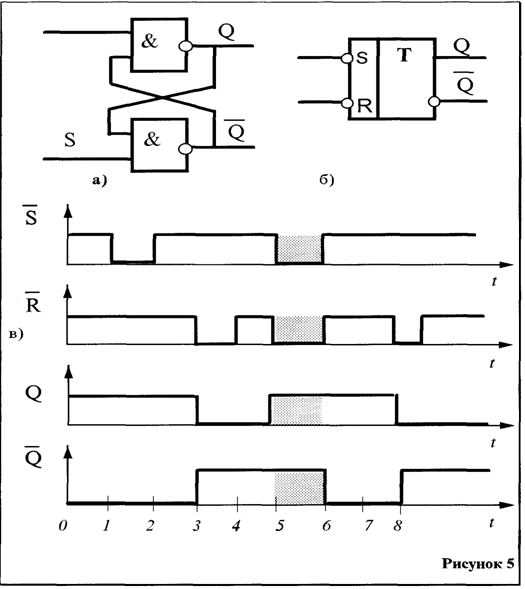

Асинхронный RS - триггер на ЛЭ И-НЕ.

а) - функциональная схема;

б) - условные обозначения;

в) - временные диаграммы работ.

Проследим работу асинхронного RS - триггера по таблице истинности, функциональной схеме, диаграммам работы (рис 3, 4). Допустим, что в исходный момент времени t состояние триггера Qt=1 (выбираем произвольно). 0-й такт. Входные сигналы R и S отсутствуют (равны 0) триггер в этот момент находился в единичном состоянии (Qt=1) первая строка таблицы переходов.

1-й такт. Входной сигнал S=1. триггер принудительно устанавливается в единичное состояние, но так как Q уже равна 1, то состояние выходов триггера не меняется. (2 - ая строка таблицы переходов)

2 - такт. S=R=0. Режим хранения информации, записанной в предыдущем такте Qt=1.

3-й такт. S=0. R=1. Триггер принудительно устанавливается в нулевое состояние при этом состояния Q и меняются на

противоположные (см 3 -я строка таблицы истинности).

4-й такт. S=R=O. Режим хранения.

5-й такт. S=0, R=1. Принудительная установка в 0. Но так как Q уже равнялось 0, то состояние выходов триггера не меняется.

6-й такт. S=R=O. Режим хранения.

7-й такт. S=1, R=0. Принудительная установка в единичные состояние. На выходах триггера появляются сигналы Qt+1=1, t+1=O.Комбинация S=R=1 является запрещенной (см рис 5, в — заштрихованная область), т. к. на триггер поступают одновременно 2 команды "установка в 0 состояние" R=1, " установка в 1 состояние" S=1. Это не позволяет однозначно определить состояние системы. Широкому использованию асинхронного RS-триггера в качестве самостоятельного устройства мешают присущие ему серьезные недостатки наличие запрещенной комбинации входных сигналов, подача информации по двум отдельным цепям (R, S), низкая помехоустойчивость. Когда необходимо синхронизировать во времени работу устройств применяют синхронные триггеры. Рассмотрим работу статического синхронного RS-триггера по таблице истинности функциональной схеме, диаграммам работы.

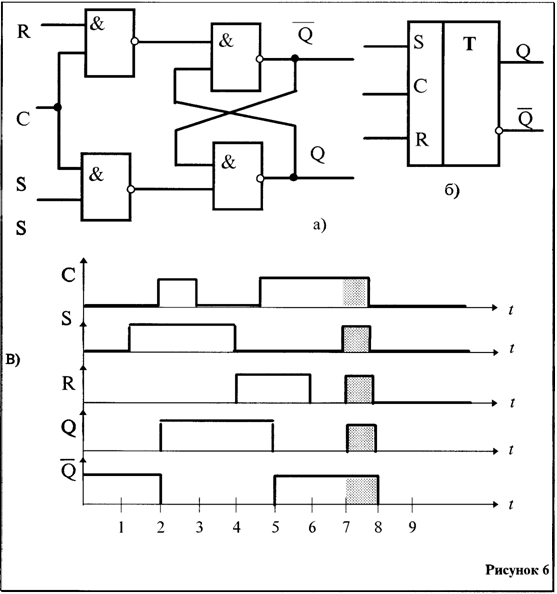

Рис 6. Синхронизируемый RS - триггер.

а) - на ЛЭ И-НЕ;

б) -условное обозначение синхронизируемого RS - триггера;

в) - временные диаграммы работы;

г) - таблица истинности.

Таблица 2.

шаг |

С |

S |

R |

Qt+1 |

Q |

Выполняемая функция |

0 |

0 |

0 |

0 |

0 |

1 |

хранение 0 |

1 |

1 |

1 |

0 |

0 |

1 |

хранение 0 |

2 |

0 |

1 |

0 |

1 |

0 |

запись 1 |

3 |

0 |

0 |

0 |

1 |

0 |

хранение 1 |

4 |

1 |

0 |

1 |

1 |

0 |

хранение 1 |

5 |

0 |

0 |

1 |

0 |

1 |

запись 0 |

6 |

0 |

0 |

0 |

0 |

1 |

хранение 0 |

7 |

1 |

1 |

1 |

0 |

1 |

хранение 0 |

8 |

0 |

1 |

1 |

X |

X |

неопределенное состояние |

1-й такт. Входной сигнал S=1, а тактируемый С=0, поэтому триггер не воспринимает информацию на входах. Qt+1=0, t+1=1. Вторая строка таблицы 2.

2-й такт. Входной сигнал S=1, тактируемый С=1. Поэтому триггер переключается в единичное состояние Qt+1=1, t+1=0. Третья строка таблицы 2.

3-й такт. Входной сигнал S-1, тактируемый С=0. Поэтому триггер не воспринимает информацию на входах, т. е. находится в режиме хранения информации Qt+1=1, t+1=0. четвертая строка таблицы 2.

4-й такт. Входной сигнал R=1, тактирумый С=0. Триггер находится в режиме хранения информации Qt+1=1, t+1=0. Пятая строка таблицы 2.

5-й такт. Входной сигнал R=1 синхронизируемый С=1. Триггер воспринимает информацию на входах и переключается в нулевое состояние Qt+1=0, t+1=1. Шестая строка таблицы 2.

6-й такт. Входные сигналы R=0, синхронизируемый С=1. Триггер хранит O. Qt+1=0, t+1=1. Седьмая строка таблицы 2.

7-й такт. Входные сигналы S=1. R=1, тактируемый сигнал С-1. Триггер сразу получает две команды включить S=1, и выключить R=1. В триггере возникает неопределенность. Поэтому такая команда является запрещенной. Восьмая строка таблицы 2, заштрихованная область на диаграмме работы.

Если сигнал синхронизации будет иметь вид импульса, то рассмотренный выше триггер превратится в динамический синхронный RS - триггер. Как вы уже знаете сигнал синхронизации в таком триггере может иметь вид как положительного (переход напряжения от уровня 0 к 1 или фронт синхроимпульса) так и отрицательного перепада напряжений (переход напряжения от уровня 1 к 0 или срез синхроимпульса).

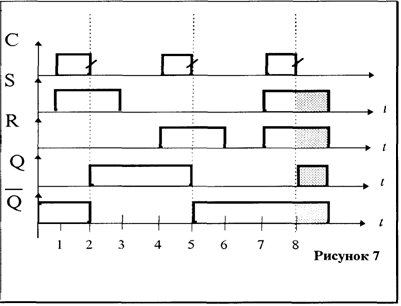

Рассмотрим динамический синхронный RS триггер, который срабатывает по срезу синхроимпульса. Динамический синхронный RS - триггер.

а) временные диаграммы работы (Рис 7);

б) таблица истинности (таблица 2).

Допустим, что в исходный момент времени t состояние триггера Qt=O (выбираем произвольно). 0 -й такт. Тактовый сигнал С=0, входные сигналы R=0, S=0. Значит, на выходе триггера Qt+1=0, Qt+1=1..

|

|

|

|

Выполняемая |

|

|

Т |

Qt+1 |

t+1 |

функция |

|

0-ой |

0 |

0 |

1 |

хранение 0 |

|

|

|

|

|

|

|

1-ый |

1 |

0 |

1 |

хранение 0 |

|

2-ой |

0 |

1 |

0 |

запись 1 |

|

3-ий |

1 |

1 |

0 |

хранение 1 |

|

4-ый |

0 |

0 |

1 |

запись 0 |

|

5-ый |

1 |

0 |

1 |

хранение 0 |

|

|

|

|

|

|

|

6-ой |

0 |

1 |

0 |

запись 1 |

|

7-ой |

1 |

1 |

0 |

хранение 1 |

|

8-ой |

0 |

0 |

1 |

запись 0 |

|

|

|

||||

Таблица 3

1-й такт. Входные сигналы S=1, R=0, тактовый сигнал С=1. Qt+1=0, t+1=1.

2-й такт. S=1, R=0, тактовый сигнал С=0. Отрицательный перепад напряжений переключает триггер в соответствии с информацией на входах S=1. Qt+1=1, t+1=0.

3-й такт. С=0, S=0, R=0. Триггер находится в режиме хранения информации Qt+1=1, t+1=0.

4-й такт. С=1, S=0, R=1. Триггер находится в режиме хранения информации Qt+1=1, t+1=0.

5-й такт. S=0, R=1, C=0 отрицательный перепад напряжений переключает триггер в состояние, соответствующее сигналам на входе R=1, S=0, Qt+1=1, t+1=1.

6-й такт. S=0, R=0, С=0. Qt+1=0, t+1=1 триггер находится в режиме хранения информации.

7-й такт. S=1, R=1, C=1. Триггер не воспринимает информацию на входах Qt+1=0, t+1=1.

8-й такт. S=1, R-1, C=0. Отрицательный перепад напряжений на синхровходе включает триггер, но данная комбинация входных сигналов S=1. R-1, является запрещенной.

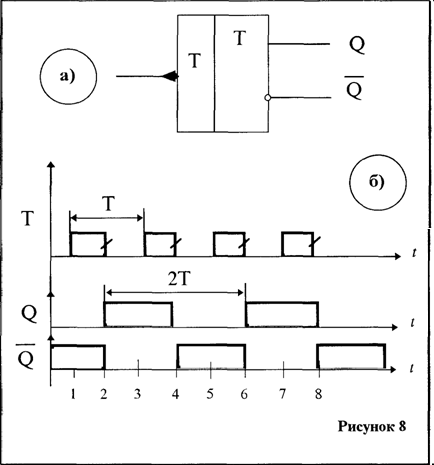

Счетный Т-триггер. Имеет один управляющий вход Т (называемый счетным входом) и два выхода Q, .

Рис 8. Счетный Т-триггер.

а) -условное обозначение;

б) - временные диаграммы работы;

в) - таблица истинности (таблица 3).

Как видно из диаграмм работы и таблицы переключений частота повторения сигнала Q вдвое меньше, чем частота повторения импульсов Т, счетные триггеры широко применяются в счетчиках, разделителях и делителях частоты, а также в различных переключателях. Одним из наиболее часто применяемых триггеров являются Д-триггер. Он имеет два входа Д и С. Вход Д-информационный, а вход С - управляющий (тактовый). Сигнал со входа Д записывается в триггер только при наличии разрешающего сигнала на входе синхронизации С. Также как и RS - триггер. Д - триггеры тоже могут быть 2-х типов статические и динамические, в зависимости от вида сигнала синхронизации.

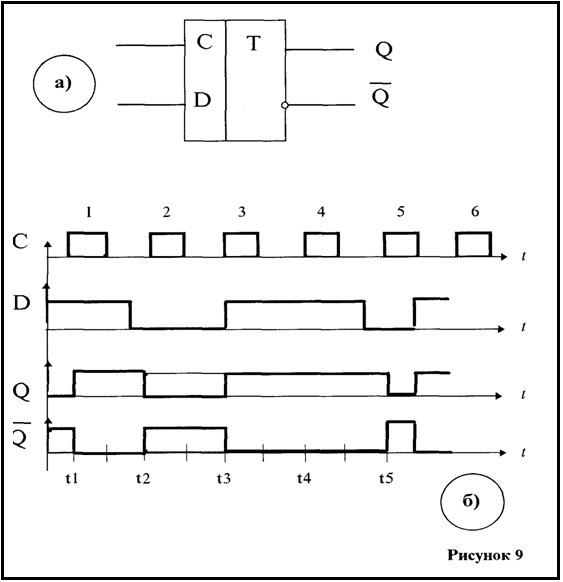

Рис 9. Синхронный статический Д - триггер.

а) - условные обозначение;

б) - временные диаграммы работы;

в) -таблицы истинности(таблица 4)

г) - выполняет функции хранения запись 1, запись 0, хранение.

Таблица 4.

С |

D |

Qt+1 |

Qt+1 |

Выполняемая функция |

0 |

1 |

Qt |

|

хранение |

1 |

1 |

1 |

0 |

запись 1 |

1 |

0 |

0 |

1 |

запись 0 |

0 |

0 |

0 |

0 |

хранение |

Допустим, что в исходный момент времени t состояние триггера Qt= 0. Из таблиц и временных диаграмм (рис 9 - б,в) видно, что Д -триггер находится в режиме хранения при С=0 и в режиме записи при С=1. Такой триггер задерживает выходной сигнал до прихода нового сигнала С=1 на тактовый вход. Отсюда произошло и название Д - триггера (от англ." delay" - задержка), так входной сигнал Д=1 кончается между первым и вторым, четвертым и пятым синхроимпульсами, а состояние Q=1 сохраняется до прихода второго и пятого синхроимпульсов. С приходом второго (пятого синхроимпульса) на выходе триггера Q=0, так как входной сигнал Д-0. Если сигнал на входе изменится во время действия синхроимпульса, то в триггере окажется записанной та информация, которая предшествовала окончанию синхроимпульса — момент t5 - t6. Благодаря этому свойству (изменение информации в течение всего времени пока С=1) рассмотренный триггер называется статическим синхронным Д - триггером. Для нормальной работы статического Д -триггера необходимо, чтобы изменение информации на Д - входе происходило только при С=0.

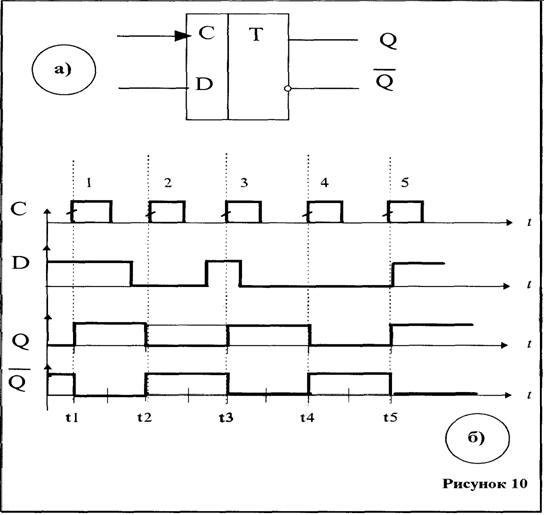

Динамический синхронный Д - триггер исключает сквозную передачу сигнала с Д - входа на выход триггера во время действия синхроимпульса. В триггере с динамическим управлением информация записывается только в момент перепада напряжения на входе синхронизации. Мы рассмотрим триггер, срабатывающий по фронту синхроимпульса (т. е. по положительному перепаду напряжений от 0 к

Рис 10. Динамический синхронный Д - триггер.

а) - условные обозначения;

б) - временные диаграммы работы;

в) - таблица истинности (таблица 5).

Таблица 5.

С |

D |

Qt+1 |

Qt+1 |

Выполняемая функция |

0 |

1 |

Qt |

|

хранение |

1 |

1 |

1 |

0 |

запись 1 |

1 |

1 |

1 |

0 |

хранение |

0 |

0 |

1 |

0 |

хранение |

1 |

0 |

0 |

1 |

запись 0 |

1 |

0 |

0 |

1 |

хранение |

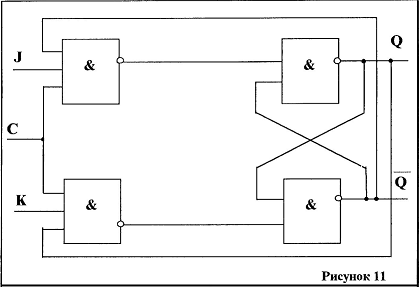

Из таблицы истинности и диаграмм работы видно, что триггер W только в момент перепада напряжения с уровня 0 на 1 на входе синхронизации С. В остальные моменты времени он находится в режиме "хранение информации". Наиболее универсальным среди синхронных триггеров является JK - триггер. Это устройство, имеющее входы J - раздельный вход установки триггера в единичное состояние (Q=1), К - раздельный ход установки универсального триггера в нулевое состояние. В интегральной схемотехнике JK -триггеры обычно выполняются синхронными. Рассмотрим работу динамического синхронного JK- триггера, который срабатывает по срезу синхроимпульса.

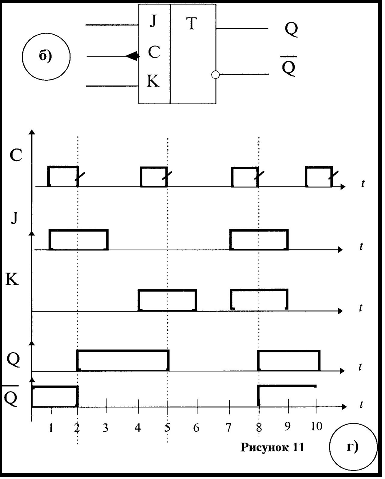

Рис 11. Универсальный JK - триггер.

а) - функциональная схема;

б) - условное обозначение;

в) - временные диаграммы работы;

г) - таблица истинности (таблица 6).

Такой триггер будет работать так же как динамический синхронный RS - триггер (см. рис. 7), при этом вход J эквивалентен входу S, а вход К - входу R, но у него не будет неопределенного состояния. Если на входы J и К подаются сигналы логической единицы, то состояние JK - триггера меняется на противоположное при каждом новом приходящем импульсе, (см момент времени t 8)

Таблица 6.

С |

J |

K |

Qt+1 |

t+1 |

Выполняемая функция |

0 |

0 |

0 |

0 |

1 |

хранение 0 |

1 |

1 |

0 |

0 |

1 |

хранение 0 |

0 |

1 |

0 |

1 |

0 |

запись 1 |

0 |

0 |

0 |

1 |

0 |

хранение 1 |

1 |

0 |

1 |

1 |

0 |

хранение1 |

0 |

1 |

0 |

0 |

1 |

запись 0 |

0 |

0 |

0 |

0 |

1 |

хранение 0 |

1 |

1 |

1 |

0 |

1 |

хранение 0 |

0 |

1 |

1 |

1 |

0 |

запись 1 |

Если входы J и К объединены между собой, то JK-триггер работает как Т - триггер. Триггер JK - типа универсальным называют потому, что на его основе с помощью несложных коммутационных изменений можно получить RS-, Т-, Д - триггеры.

Рис 12. Применение JK - триггера для построения триггеров RS(a), Т(б), Д(в). Триггеры любого типа помимо информационных и управляющих входов могут быть снабжены установочными входами R и S, при подаче сигнала на эти входы триггер устанавливается в соответствующее состояние независимо от уровня сигнала, присутствующего на других его входах.

Как видно из рисунка 12 для проектирования остальных на базе JK-

Триггера применяют двухступенчатый(ТТ) синхронный JK- триггер.

Рассмотрим принцип его работы.

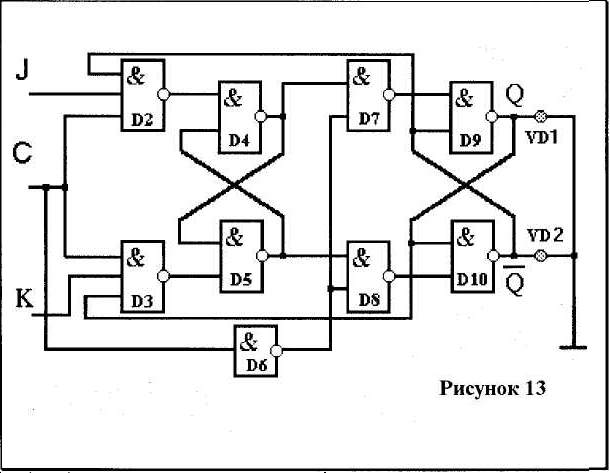

Рис.13. Двухступенчатый JK-триггер.

Как видно из рисунка 13 двухступенчатый триггер состоит из основного триггера на логических элементах D4 и D5 с вентилями D2 и D3 и дополнительного триггера на логических элементах D9, D10 с вентилями D7 и D8. Дополнительный триггер также является тактируемым, причем в отличие от основного синхронизируется потенциалом логического нуля. Для этой цели в схему введен инвертор D6 на логическом элементе И-НЕ.

Рассмотрим работу триггера при разных комбинациях входного сигнала. Пусть в исходном положении триггер находится в нулевом состоянии Q=0).Тогда на одном из входов вентилей D2 и D3 будут соответственно логическая 1 ( =1) и логический 0 (Q=O). При отсутствии тактового импульса на входе С вентили D2 и D3 закрыты независимо от того, какие сигналы на остальных входах D2 и D3.

Пусть на вход J подан сигнал логической единицы. Тогда с приходом импульса синхронизации С=1 вентиль D2 откроется, а вентиль D3 останется закрытым.

Одновременно закроются оба вентиля D7 и D8 сигналом логического О, снимаемого с выхода инвертора D6.

Сигнал логического 0, снимаемый с открытого вентиля D2, записывает в основной триггер информацию, устанавливая его в состояние 1. Тогда на одном из входов D7 будет сигнал логической 1,а на входе вентиля О8-сигнал логического нуля.

Однако эти сигналы никак не меняют состояние вспомогательного триггера, т.к. эти вентили во время действия импульса синхронизации С=1 закрыты. По его окончании на вторых входах вентилей D7 и D8 появится логическая 1, а вентили D2 и D3 закроются. Т.к. основной триггер находится в положении 1, то откроется вентиль D7 и информация запишется во вспомогательный триггер, который установится в положение 1(Q=1).

Совершенно аналогично сигнал, поданный на вход К (К=1),установит триггер в состояние логического 0: Q=0.

Таким образом, в триггере данного типа изменение выходного сигнала происходит только в моменты, когда потенциал С переходит из 1 в о. Поэтому говорят, что эти триггеры тактируются фронтом или срезом, в отличие от триггеров, тактируемых потенциалом.

Если соединить вместе входы J и К и подать на них уровень логической 1, то триггер станет счетным, а счетные импульсы Т будут приходить с генератора одиночных импульсов на вход С триггера.

С помощью двух инверторов на базе JK-триггера можно собрать D-триггер. Первый инвертор нужен для того, чтобы поменять перепад напряжения, по которому срабатывает триггер. D-триггер, в отличие от всех остальных, срабатывает по положительному перепаду напряжения. Второй инвертор нужен для того, чтобы выполнилось

условие

D=J=![]() ,

т.е. чтобы на входах J

и К были всегда разные сигналы и

триггер работал как триггер задержки.

,

т.е. чтобы на входах J

и К были всегда разные сигналы и

триггер работал как триггер задержки.

Промышленностью выпускаются триггеры в виде ИМС, имеющих разные функциональные возможности. JK-триггер ИМС типа К155ТВ1, D-триггер ИМС типа К155ТМ7, К155ТМ8.

Методика исследования.

Работа JK-триггера. Проектирование на его основе RC-, D- и Т-триггеров.

«А» виртуальная реализация лабораторной работы

Прежде чем приступить к выполнению виртуальной лабораторной работы необходимо инсталлировать программное обеспечение CircuiMaker2000. Программа находится на настоящем диске в папке CM2000. Для инсталляции запустите файл SetupCM2000.exe, выберите стандартный тип установки и следуйте указаниям инсталлятора. Пароль для инсталляции находится в файле Password.txt в той же папке. После установки установите пакет обновлений файл CM2000SP1.exe. Инструкция по работе с программой CircuiMaker2000 находится в Приложении №2. В ряде случаев имеются отличия виртуальной лабораторной работы от ее стендовой реализации. Критерием правильности является верное выполнение таблицы истинности.

«Б» стендовая реализация лабораторной работы

Порядок выполнения работы.

Включить стенд (светодиод "POWER" горит) , внешний вид см. в Приложение№1.

Начертите в тетради таблицу 1-таблицу истинности синхронного двухступенчатого JK-триггера.

Таблица 1.

-

J

K

C

Q

Соберите схему JK-триггера для этого соедините проводами соответствующие гнёзда, схему соединения смотри в теоретическом введении.

Переключателями S1 и S2 подать комбинацию входных сигналов J и К на триггер. Записать её в таблицу 1. (светодиод VD1 горит — J=1, не горит — J=0 светодиод VD3 горит — К=1, не горит — К=0)

Кнопкой S3 подайте тактовые импульсы с ГОИ (генератора одиночных импульсов) на вход триггера С. По показаниям светодиодов VD4 и VD5 пронаблюдайте как зависят сигналы на выходе Q и Q от значения на входе С. Результаты запишите в таблицу.

Проделайте пункты 4, 5 для других комбинаций J и К.

Начертите в тетради таблицу 2-таблицу истинности RS- триггера.

Таблица 2.

Соберите схему RS-триггера. (см в теоретическом введении). Напомним лишь, что в этом случае вход S эквивалентен входу J, а вход R-входу К. Комбинация S=R=1 является запрещенной.

Заполните таблицу 2 при разных комбинациях S, R, С.

Начертите в тетради таблицу 3-таблицу истинности Т-триггера.

Таблица 3.

Соберите схему Т-триггера. При этом входы J и К объединяются и на них подается уровень логической 1, на вход С подаются счетные импульсы Т с ГОИ. Более подробное объяснение см в теоретическом введении.

Заполните таблицу 3 для разных комбинаций Т.

Начертите в тетради таблицу истинности D-триггера, таблицу 4.

Таблица 4.

Соберите схему D-триггера (см в теоретическом введении). Один из инвенторов, включенный на С входе, обеспечивает срабатывание D- триггера по фронту импульса в отличии от всех остальных триггеров. Второй инвентор обеспечивает условие D=J=K.

Заполните таблицу 4 при разных комбинациях D и С.

16. Выключить стенд.

t+1

t+1