- •Історія розвитку мп техніки. Закон мура

- •Основні технології виготовлення мпп

- •Сучасний стан та тенденції розвитку мікропроцесорних пристроїв. Наслідки закону Мура.

- •Класифікація мпп та систем

- •Класифікація мікропроцесорів

- •Закон Амдала та його наслідки

- •Структура типового мп

- •Cisk та risc архітектури

- •Гарвардська та принстонська архітектури

- •Поняття та класифікація арифметико – логічних пристроїв

- •Регістри

- •Пристрої синхронізації

- •Ієрархія пам’яті мпп

- •Типова мікросхема пам’яті

- •Структури пам’яті

- •Постійна пам'ять

- •Флеш – пам'ять

- •Структурна схема uart

- •Основні регістри uart

- •Програмування передавання даних за допомогою інтерфейсу uart

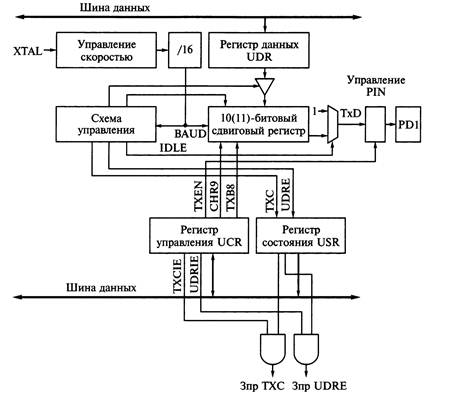

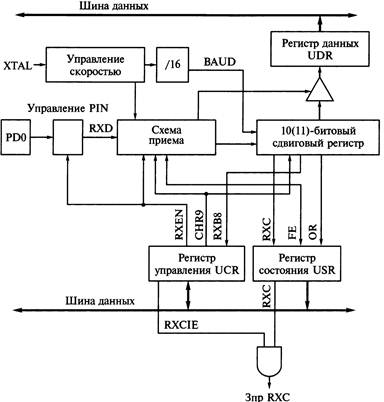

Структурна схема uart

UART (universal asynchronous receiver/transmitter — універсальний асинхроний приймач/передавач) — тип асинхроного приймач-передавача, компонент комп'ютерів та периферії, що переводить дані між паралельною та послідовною формами. UART звичайно використовується спільно з іншими комунікаційними стандартами, такими як EIA RS-232.

Структура:

тактовий генератор, частота якого як правило кратна бітрейту, щоб дозволити дискретизацію на середину циклу передачі біта.

зсувні регістри вводу та виводу

схему контролю передачі/прийому

логіка контролю читання/запису

буфери передачі/прийому (опціонально)

буфер паралельної шини даних (опціонально)

пам'ять буфера стека FIFO (опціонально)

Структурна схема передавача UART 2. Структурна схема приймача UART

Основні регістри uart

• UDR (UART Data Register $0C) — регістр даних UART, містить байт

даних, що приймається або передається;

• UCR (UART Control Register $0A) — регістр керування, управляє

конфігурацією UART, а також містить 8-й біт даних;3

• USR (UART Status Register $0B) — регістр статусу UART, відображає

стан модуля UART, зокрема прапорів переривань;

• UBRR (UART Baud Rate Register, $09) — регістр швидкості передачі,

задається швидкість передачі даних по UART.

Швидкість передачі визначається за формулою:

BAUD=FCK/16(UBRR+1),

де BAUD - частота в бодах;

FCK - частота мікроконтролера;

UBRR -уміст регістра UBRR (0 -255).

Програмування передавання даних за допомогою інтерфейсу uart

До складу UART входить передавальний і приймаючий регістри зсуву, буфер приймача і передавача SBUF і блок управління роботою порту з регістром управління SCON. Запис байта в буферпризводить до автоматичного перепису байта в регістр зсуву передавача і ініціює початок передачі. Наявність буферного регістра приймача дозволяє поєднувати операцію читання з SBUF раніше прийнятого байта з прийомом чергового. Якщо до моменту закінчення прийому чергового байта попередній не був лічений з SBUF, то він буде втрачений.

Швидкість передачі/прийому (частота пересилки бітів) залежить від запрограмованого режиму роботи порту і значення біта SMOD в регістрі PCON. Як вказувалося раніше послідовний порт може працювати в одному з чотирьох режимів.

Режим 0. Інформація і передається і приймається через зовнішній вивід RXD (лінія порту Р3.0). Через вихід передавача TXD (Р3.1) видаються тактові імпульси, що стробують передавані або такі, що приймаються біти. Формат посилки - 8 біт. Зсув даних (молодшим значущим бітом вперед) відбувається на останній фазі (S6P2) кожного периферійного циклу тому частота прийому і передачі рівна FOSC/12.

Режим 1. Інформація передається через вивід TXD, а приймається через RXD. Формат посилки - 10 біт (стартовий - "0", 8 інформаційних і стоповий, - "1"). При прийомі стоп-біт поступає в розряд RB8 регістра SCON. Частота обміну задається програмуванням T/C1.

Режим 2. Послідовні дані видаються на вивід TXD, а приймаються по виводу RXD. Кадр даних складається з 11 біт (старт-біт, 8 інформаційних, програмований дев'ятий біт і стоп-біт). При передачі дев'ятий біт транслюється з SCON.TB8, а при прийомі - передається в SCON.RB8. Дев'ятий біт використовується по розсуду програміста, наприклад як біт контролю інформації по парності або як прапор ("control/data" або "address/data") ідентифікації передаваного або такого, що приймається кадру. Частота обміну рівна 2SMOD 64 OSC . F / .

Режим 3. Ідентичний режиму 2 з тією відмінністю, що частота обміну задається

програмуванням T/C1 (як і в режимі 1) і рівна 2SMOD 32 OV . F /, де FOV – частотапереповнювань (overflow) таймера 1. У більшості додатків таймер 1 конфігурується по схемі режиму 2 (8-бітовий таймер з автоперезавантаженням),