- •Питання контролю спз

- •Класифікація програмного забезпечення обчислювальних систем. Предмет та задачі спз.

- •Еволюція спз.

- •Призначення та склад операційних систем.

- •Основні принципи розробки системного програмного забезпечення.

- •Стратегії планування.

- •Дисципліни диспетчеризації.

- •3. Алгоритми в диспетчеризації з витісненням та без.

- •4. Способи забезпечення гарантованого обслуговування процесів.

- •6. Вплив планування на ефективність обчислювальних систем.

- •7. Використання динамічних пріоритетів.

- •1. Незалежні та взаємодіючі обчислювальні процеси.

- •2. Види задач синхронізації паралельних процесів.

- •3. Синхронізація за допомогою блокування пам’яті.

- •5. Команда “перевірка” та “встановлення”.

- •6. Використання семафорів для синхронізації та впорядкування паралельних процесів.

- •7. Монітороподібні засоби синхронізації паралельних процесів.

- •8. Поштові ящики.

- •9. Конвеєри.

- •10. Черги повідомлень.

- •Підходи до керування реальною пам’яттю.

- •Неперервний розподіл оперативної пам’яті.

- •Розподіл з перекриттям.

- •Статичний розподіл пам’яті.

- •Динамічний розподіл пам’яті.

- •Структура, основні принципи віртуалізації пам’яті.

- •1. Реальний і захищений режими роботи процесора.

- •Мал. 3.1 Схема визначення фізичної адреси для процесора 8086.

- •2. Нові системні регістри мікропроцесорів і80x86.

- •Мал. 7.2 Основні системні регістри мікропроцесорів і80x86.

- •4. Підтримка сторінкового способу організації віртуальної пам'яті.

- •Мал. 7 Дескриптор сторінки.

- •6. Захист адресного простору задач.

- •Якщо цільовий сегмент є сегментом стека, то правило перевірки має вид

- •1. Основні поняття і визначення процесу вводу/виводу.

- •2. Режими керування вводом/виводом.

- •Керування вводом/виводом.

- •3. Закріплення пристроїв, загальні пристрої вводу/виводу.

- •4. Основні системні таблиці вводу/виводу.

- •Процес управління вводом/виводом.

- •Синхронний і асинхронний ввід/вивід.

- •6. Кешування операцій вводу/виводу при роботі з накопичувачами на магнітних дисках.

- •Файлові системи fat, vfat, fat32, hpfs.

- •Структура системи файлів.

- •Файлова система ntfs (New Technology File System)

Мал. 3.1 Схема визначення фізичної адреси для процесора 8086.

У захищеному режимі роботи визначення фізичної адреси здійснюється зовсім інакше. Насамперед використовується сегментний механізм для організації віртуальної пам'яті. При цьому адреси задаються 32-бітовими значеннями. Крім цього, можлива сторінкова трансляція адрес, також з 32-бітовими значеннями. Нарешті, при роботі в захищеному режимі, що за замовчуванням припускає 32-бітовий код, можливе виконання подвійних програм, створених для роботи мікропроцесора в 16-бітовому режимі. Для цього введений режим віртуальної 16-бітової машини і 20-бітові адреси реального режиму транслюються за допомогою сторінкового механізму в 32-бітові значення захищеного режиму. Нарешті, є ще один режим — 16-бітовий захищений, що дозволяє 32-бітовим мікропроцесорам виконувати захищений 16-бітовий код, що був характерний для мікропроцесора 80286. Правда, слід зазначити, що цей останній режим практично не використовується, оскільки програм, створених для нього, не так вже і багато.

Для вивчення цих можливостей розглянемо спочатку нові архітектурні можливості мікропроцесорів i80х86.

2. Нові системні регістри мікропроцесорів і80x86.

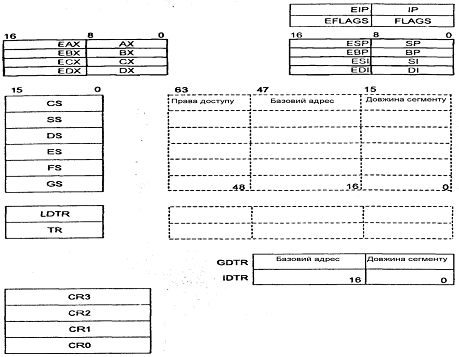

Основні регістри мікропроцесора і80x86, знання яких необхідно для розуміння захищеного режиму роботи, приведені на мал. 3.2. Варто звернути увагу на наступне:

покажчик команди ЕIP — 32 бітовий регістр, молодших 16 розрядів цього регістра є регістр IP;

регістр флагів EFLAGS — 32 біта, молодших 16 розрядів представляють регістр FLAGS;

регістри загального призначення ЕАХ, ЕВХ, ЕСХ, EDX, а також ESP, EBP, ESI, EDI — 32-бітові, однак їх молодші 16 розрядів являють собою відомі регістри АХ, ВХ, СХ, DX, SP, BP, SI, DI;

сегментні регістри CS, SS, DS, ES, FS, GS — 16-бітові. При кожному з регістрів CS, SS, DS, ES, FS, GS зображені пунктиром сховані від програмістів (недоступні нікому, крім власне мікропроцесора) 64-бітові регістри, у які завантажуються дескриптори відповідних сегментів;

регістр-покажчик на локальну таблицю сегментів поточної задачі- - LDTR (16 бітів). При цьому регістрі також є «тіньовий» (схований від програміста) 64-бітовий регістр, у який мікропроцесор заносить дескриптор, що вказує на таблицю дескрипторів сегментів задачі, що описують її локальний віртуальний адресний простір;

регістр-покажчик задачі TR (task register, 16 бітів). Указує на дескриптор у глобальній таблиці дескрипторів, що дозволяє одержати доступ до дескриптора задачі TSS2 — інформаційній структурі, що підтримує мікропроцесор для керування задачами;

регістр CDTR1 (48 бітів) глобальної таблиці GDT, що містить як дескриптори загальних сегментів, так і спеціальні системні дескриптори. Зокрема, у GDTR знаходяться дескриптори, з допомогу яких можна одержати доступ до сегментів TSS;

регістр IDTR (48 бітів) таблиці дескрипторів переривань. Містить інформацію, необхідну для доступу до ”таблиці переривань” IDT;

керуючі регістри CR0 - CR3 (32-бітові) і деякі інші регістри.