Лабораторна робота № 3. Проектування арифметико-логічного пристрою з акумулятором Мета роботи:

Навчитись створювати, модифікувати, компілювати та проводити симуляцію роботи арифметико-логічного пристрою мікропроцесора.

Загальні відомості

Важливою складовою частиною будь-якого мікропроцесора є арифметико-логічний пристрій (АЛП) – комбінаційна схема, що виконує арифметичні та логічні операції над вхідними даними. АЛП може містити і схеми пам’яті, наприклад регістр накопичення результату – акумулятор, регістри-прапорці ознак (ознака нуля, переповнення переносу, тощо).

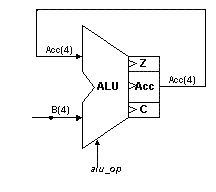

В даній лабораторній роботі розглядається АЛП навчального 4-розрядного мікропроцесора Gnome. Першим вхідним операндом АЛП є поточна інформація з акумулятора curr_ acc, другим — операнд b, що надходить ззовні АЛП. Також вхідними даними є поточні значення ознак переносу curr_carry та нуля curr_zero. АЛП реалізує множину операцій над вхідними даними, вибір операції визначається сигналом на вході коду операції alu_op. Результат роботи подається на вихід next_acc, формуються ознаки переносу next_carry, та нуля next_zero.

Рис. 1. АЛП процесора Gnome

Таблиця 1 Варіанти операцій АЛП

Мнемоніка |

Код |

Дії |

NOP |

0000 |

АЛП дії не виконує |

PASS_OP |

0001 |

На вихід next_acc подається значення операнду b, значення ознак нуля та переносу залишаються незмінними. |

ADD_OP |

0010 |

Виконання арифметичної операції додавання двох вхідних операндів, формується ознака переносу, ознака нуля залишається незмінним. |

XOR_OP |

0011 |

Виконання логічної операції XOR над двома вхідними операндами, ознака нуля та ознака переносу залишаються незмінною. |

AND_OP |

0100 |

Виконання логічної операції AND над двома вхідними операндами, формується ознака нуля, ознака переносу залишається незмінною. |

SET_CARRY_OP |

0101 |

На вихід next_acc подається значення cur_acc, ознака переносу встановлюється в 1, ознака нуля залишається незмінною. |

Хід роботи

Для кодування орепацій АЛП зручно використати мнемонічні позначення. Константи-мнемоніки доцільно винести в окремий package-file, де міститимуться усі мнемоніки, оголошувані користувачем типи даних, та інші настроювані параметри проекту процесора.

-- File: PG13_package.vhd

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

PACKAGE PG13_package IS

-- Constants for ALU operation codes

CONSTANT NOP_OP: std_logic_vector (3 DOWNTO 0):= "0000";

CONSTANT LOAD_OP: std_logic_vector (3 DOWNTO 0):= "0001";

CONSTANT ADD_OP: std_logic_vector (3 DOWNTO 0):= "0010";

CONSTANT XOR_OP: std_logic_vector (3 DOWNTO 0):= "0011";

CONSTANT AND_OP: std_logic_vector (3 DOWNTO 0):= "0100";

CONSTANT SET_C_OP: std_logic_vector (3 DOWNTO 0):= "0101";

CONSTANT CLR_C_OP: std_logic_vector (3 DOWNTO 0):= "0110";

END PG13_package;

Створити новий HDL - файл з інтерфейсом АЛП – вхідні порти:

curr_acc ( 4 розряди)

curr_b (4)

curr_carry (1)

curr_zero (1)

alu_op (4).

Вихідні порти:

next_acc (4);

next_carry (1)

next_zero (1)

Підключити Потрібні бібліотеки та package-file

-- File: ALU.vhd

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

USE IEEE.std_logic_unsigned.ALL;

USE WORK.pg13_package.ALL;

Реалізувати роботу АЛП за допомогою процесу з наступним списком чутливості

PROCESS (curr_acc, curr_b, curr_carry, curr_zero, alu_op)

В процесі використати конструкцію CASE (наведено фрагмент):

CASE alu_op IS

WHEN NOP_OP =>

next_acc <= curr_acc;

next_carry <= curr_carry;

next_zero <= curr_zero;

WHEN XOR_OP=>

. . .

WHEN ADD_OP =>

. . .

WHEN PASS_OP =>

. . .

WHEN AND_OP =>

. . .

WHEN SET_CARRY_OP =>

. . .

WHEN CLR_CARRY_OP =>

. . .

WHEN OTHERS =>

next_acc <= curr_acc;

next_carry <= curr_carry;

next_zero <= curr_zero;

END CASE;

Працюючи по двоє, розробити код, що реалізує АЛП-операції, з кодами рівними порядковим номерам студентів в групі (від 1 до 15, далі- циклічно). Перші 5 операцій приведені в таблиці 1. Інші операції потрібно вибрати самостійно та погодити з викладачем. Можливі арифметичні та логічні дії, наприклад операції «логічне або», зсув, встановлення та онулення прапорців ознак та акумулятора, тощо. Опис операторів мови HDL доступний в системі допомоги пакету Aldec Active-HDL (F1 – contents – operators ).

adding_operator ::= + | - | &

logical_operator ::= and | or | nand | nor | xor | xnor

miscellaneous_operator ::= ** | abs | not

multiplying_operator ::= * | / | mod | rem

relational_operator ::= = | /= | < | <= | > | >=

shift_operator ::= sll | srl | sla | sra | rol | ror

Провести моделювання проектованих операцій АЛП з використанням часових діаграм.

Скласти звіт з виконання лабораторної роботи обсягом 2-3 сторінки друкованого тексту та захистити його. Зміст повинен містити опис проектованих команд, кінцевий HDL код проектованого пристрою. Рекомендується додати часову діаграму.

Список рекомендованої літератури

Сергиенко А. М. VHDL для проектирования вычислительных устройств. ТИД "ДС". 2003. C. 208