- •Предисловие

- •Глава 1. Основные сведения об электронных схемах

- •1.1. Единство электронных схем

- •1.2. Виды технической документации

- •1.3. Пассивные элементы рэа

- •1.4. Свободные электрические колебания в контуре

- •1.5. Вынужденные колебания в последовательном контуре

- •1.6. Вынужденные колебания в параллельном контуре

- •1.7. Связанные колебательные контуры

- •1.8. Электрические фильтры

- •Контрольные вопросы и задания

- •Глава 2. Полупроводниковые диоды и транзисторы

- •2.1. Полупроводниковые диоды

- •2.2. Биполярные транзисторы

- •2.3. Тиристоры

- •2.4. Полевые транзисторы

- •2.5. Полупроводниковые оптоэлектронные приборы

- •2.6. Интегральные активные и пассивные элементы

- •Контрольные вопросы и задания

- •Глава 3. Электровакуумные приборы 3.1. Электронно-управляемые лампы

- •3.2. Электронно-лучевые трубки

- •3.3. Газоразрядные приборы

- •3.4. Фотоэлектрические приборы

- •Контрольные вопросы и задания

- •Глава 4. Общие сведения об усилителях

- •4.1. Структурная схема электронных усилителей и их классификация

- •4.2. Основные технические показатели и характеристики усилителей

- •4.3. Виды обратных связей в усилителях

- •4.4. Влияние обратной связи на коэффициент усиления

- •4.5. Влияние обратной связи на входное сопротивление

- •Контрольные вопросы и задания

- •Глава 5. Усилители переменного напряжения

- •5.1. Принцип усиления переменного напряжения

- •5.2. Усилительные каскады на полевых транзисторах

- •5.3. Усилительные каскады на биполярных транзисторах

- •5.4. Динамические характеристики

- •5.5. Динамические параметры

- •5.6. Эквивалентные схемы

- •5.7. Анализ частотных свойств усилителей напряжения

- •5.8. Широкополосные усилители

- •В вус на бт время установления определяется выражением

- •5.9. Коррекция ачх усилителей переменного напряжения

- •5.10. Повторители напряжения

- •5.12. Интегральные усилители переменного напряжения

- •Контрольные вопросы и задания

- •Глава 6. Усилители мощности

- •6.1. Режимы работы усилительного каскада

- •6.2. Однотактные усилители мощности

- •6.3. Двухтактные усилители мощности

- •Контрольные вопросы и задания

- •Глава 7. Усилители с гальваническими связями

- •7.1. Общие сведения

- •7.2. Простейшие угс прямого усиления

- •7.3. Балансные усилители

- •7.4. Дифференциальные усилители

- •7.5. Дифференциальные усилители с генераторами стабильного тока

- •В качестве диода vd в интегральных ду обычно используется транзистор в диодном включении.

- •7.6. Структура и основные параметры интегральных операционных усилителей

- •7.7. Схемотехника интегральных операционных усилителей

- •7.8. Применение интегральных операционных усилителей

- •7.9. Усилители постоянного и медленно меняющегося напряжения с преобразованием сигнала

- •Контрольные вопросы и задания

- •Глава 8. Генераторы синусоидального напряжения

- •8.1. Условия самовозбуждения

- •8.4. Стабилизация частоты колебаний -автогенератора

- •Контрольные вопросы и задания

- •Глава 9. Основные понятия импульсной техники

- •9.1. Виды и параметры импульсных сигналов

- •9.2. Спектральный состав импульсных сигналов

- •9.3. Формирование импульсов яс-цепями

- •9.4. Амплитудные ограничители

- •Контрольные вопросы и задания

- •Глава 10. Логические функции и базовые логические элементы

- •10.1. Основные положения алгебры логики

- •10.2. Электронные ключи

- •10.3. Параметры логических элементов

- •10.4. Базовые логические элементы на биполярных структурах

- •10.5. Базовые логические элементы на мдп- и кмдп-структурах

- •Контрольные вопросы и задания

- •Глава 11. Формирователи и генераторы электрических импульсов

- •11.1. Виды генераторов -электрических импульсов и их особенности

- •11.2. Мультивибраторы

- •11.3. Одновибраторы

- •11.4. Антидребезговые формирователи одиночных импульсов и перепадов напряжения

- •11.5. Генераторы линейно изменяющегося напряжения

- •11.6. Компараторы напряжений

- •Контрольные вопросы и задания

- •Глава 12. Триггерные структуры

- •12.1. Общие сведения

- •12.2. Симметричный триггер на биполярных транзисторах V с коллекторно-базовыми связями

- •2.3. Структура и классификация интегральных триггеров

- •Контрольные вопросы и задания

- •Глава 13. Цифровые и комбинационные электронные устройства

- •13.1. Двоичная система счисления

- •13.2. Регистры

- •13.3. Двоичные счетчики импульсов

- •13.4. Двоично-десятичные счетчики

- •13.5. Шифраторы и дешифраторы

- •13.6. Мультиплексоры и демультиплексоры

- •13.7. Устройства сдвига и сравнения кодов чисел

- •13.8. Сумматоры

- •13.9. Типы запоминающих устройств и их основные характеристики

- •13.10. Запоминающие элементы на биполярных структурах

- •13.11. Запоминающие элементы на мдп-структурах

- •13.12. Запоминающие устройства на функциональных приборах .

- •13.13. Аналого-цифровые и цифро-аналоговые преобразователи

- •Контрольные вопросы и задания

- •Глава 14. Микропроцессоры и микроэвм 1

- •4.1. Общие сведения о микропроцессорах

- •14.2. Структура микропроцессора

- •14.3. Система команд микропроцессора

- •14.4. Области использования микроэвм в народном хозяйстве

- •14.5. Программируемые калькуляторы как разновидность микроэвм

- •Контрольные вопросы и задания

- •Глава 15. Источники стабилизированного напряжения

- •15.1. Структура источников стабилизированного напряжения

- •15.2. Однофазные неуправляемые выпрямители

- •2 . 15.3. Однофазныеуправляемые выпрямители

- •15.4. Сглаживающие фильтры

- •15.5. Электронные стабилизаторы постоянного напряжения

- •Контрольные вопросы и задания

13.5. Шифраторы и дешифраторы

Процесс обработки сигналов с помощью электронных устройств часто начинается с кодирования этих сигналов. В цифровых устройствах, в том числе в ЭВМ, используются, двоичные и двоично-десятичные коды (см. § 13.1), в которых сигналы представляются в виде логических 0 и 1. Двоичную цифру, принимающую значение 0 или 1, называют битом.

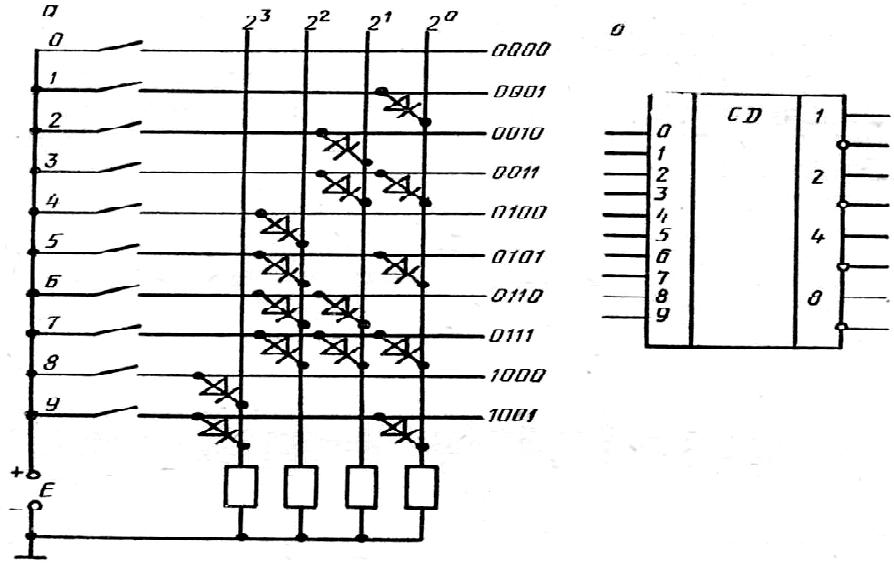

Шифратор, или кодер,— это устройство, осуществляющее кодирование сигналов. На рис. 13.15, а приведена схема матричного шифратора, с помощью которого можно осуществить кодирование любой десятичной цифры от 0 до 9 в соответствующее ей четырехразрядное двоичное число. Кодирование осуществляется нажатием кнопок, соответствующих десятичным цифрам. Например, при нажатии кнопки 9 к источнику питания Е через два нижних (по схеме) диода оказываются подключенными две крайние вертикальные шины 23 и 20. На двух средних вертикальных шинах 22 и 21 при этом напряжение равно нулю.

Рис. 13.15. Схема (а) и условное обозначение (б) шифратора

Дешифратором называют устройство, служащее для преобразования кода числа на входе (или комбинации входных сигналов) в сигнал на определенном выходе. Условное графическое обозначение дешифратора показано на рис. 13.16.

Если при п входах (где п — число разрядов двоичного числа) дешифратор имеет т = 2п выходов, то такой дешифратор называется полным. При 2п-1<т<2п дешифратор называется неполным или частичным.

Рис. 13.16. Условное обозначение дешифратора

Обычно входы дешифратора подключаются к выходам разрядов регистра или счетчика, на которых формируется код числа.

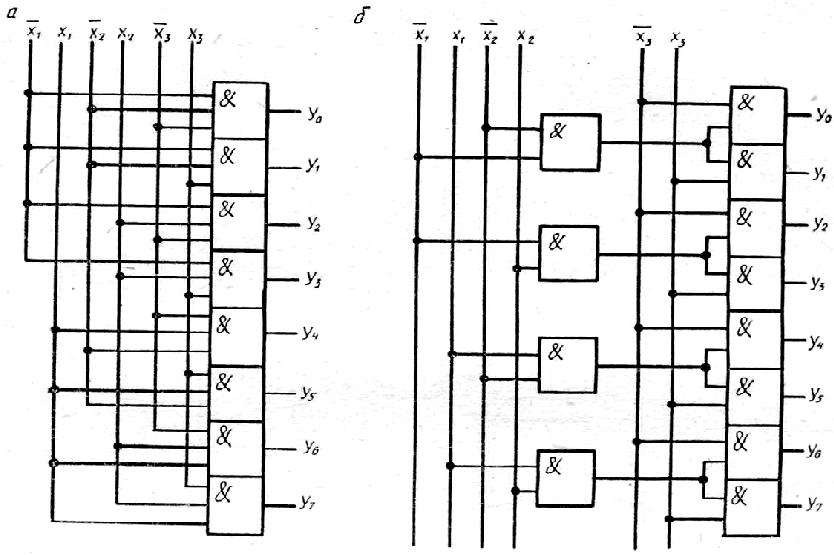

Правила работы дешифратора на три входа х1, х2 и х3 можно представить табл. 13.4.

Количество выходов такого дешифратора т = 23 = 8 (у0, у1, у2, ..., у7). Сигнал на том или ином выходе дешифратора появляется только при вполне определенном наборе входных сигналов. Состояние каждого выхода определяется переключательными функциями, представленными в последнем столбце табл. 13.4.

Табл. 13.4. Состояния трехвходового дешифратора

К аждая из этих функций может быть реализована трехвходовым логическим элементом И, как показано на рис. 13.17, а. Прямые и инверсные значения входных переменных поступают на дешифратор непосредственно с прямых и инверсных выходов регистра или счетчика, в которых записан код числа. В зависимости от этого кода появляется логическая 1 на соответствующем выходе. Если, например, х1 = 0 (х1 — старший разряд), а х2 = х3 = 1, то логическая 1 образуется только на выходе у3, так как при этом переключательная функция х1х2x3 = 1, а все остальные равны 0.

Рассмотренный дешифратор называется одноступенчатым или линейным. Его достоинством является высокое, быстродействие, определяемое временем задержки сигнала в одном элементе И, а недостатком — значительное, число входов ЛЭ и высокие требования к нагрузочной способности элементов входного регистра (коэффициент разветвления по выходу триггера каждого разряда равен половине числа элементов И). Так как коэффициент разветвления большинства базовых ЛЭ ИМС не превышает восьми, то максимальная разрядность дешифрируемых чисел для линейных дешифраторов без принятия специальных мер не превышает п = 4...8.

Усовершенствование структуры дешифраторов возможно за счет каскадного объединения отдельных входов. Такие дешифраторы называются многоступенчатыми.

Рис. 13.17. Схемы одноступенчатого (а) и многоступенчатого (б) дешифраторов

К ним относятся пирамидальные и матричные, или прямоугольные.

Схема пирамидального трехвходового дешифратора приведена на рис. 13.17, б. Легко заметить, что значения у0, у1, ..., у7 определяются теми же переключательными функциями, что и в линейном дешифраторе, однако вместо трехвходовых в пирамидальном дешифраторе используются двухвходовые ЛЭ. При большем числе входных переменных увеличивается число ступеней, или каскадов, дешифратора.

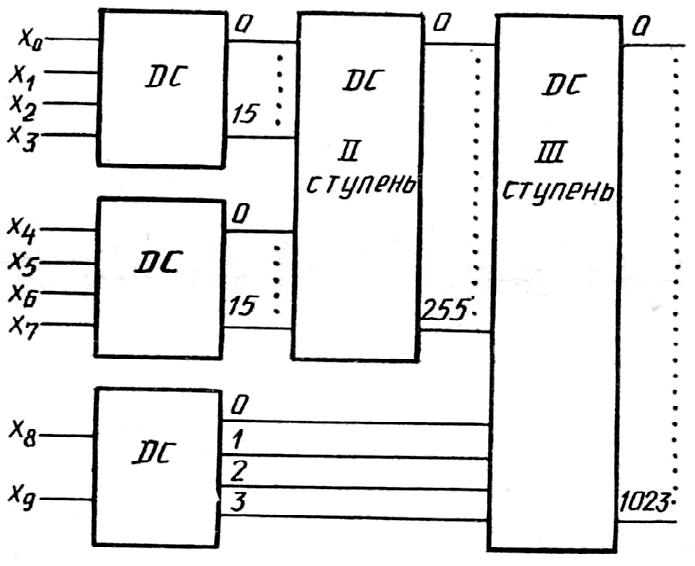

В матричном дешифраторе дешифрируемое слово разбивается на несколько подслов, которые дешифрируются на линейных дешифраторах. Выходы линейных дешифраторов служат входами следующей ступени дешифратора. Вариант схемы матричного дешифратора с десятью входами п=10 и т=210=1024 выходами показан на рис. 13.18.

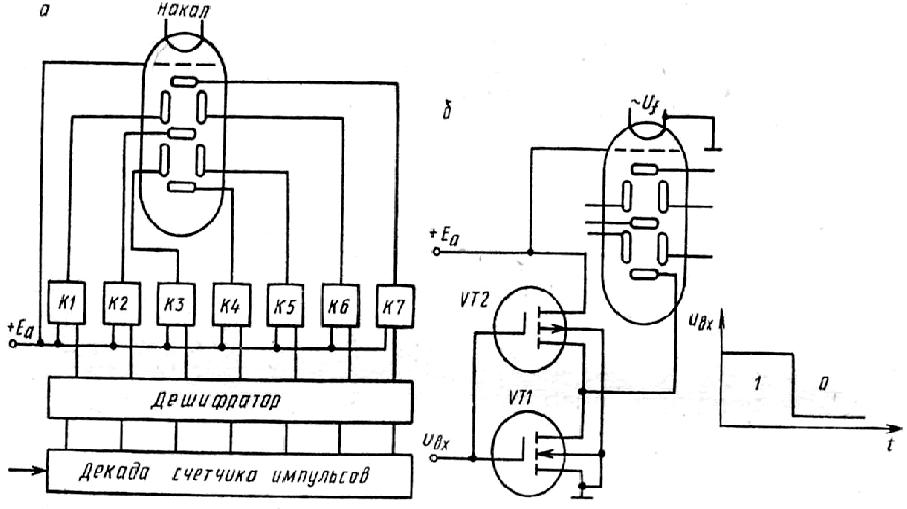

Дешифраторы применяются в устройствах управления ЦВМ, для преобразования параллельного кода в последовательный, построения распределителей импульсов по различным цепям и т. п. На рис. 13.19, а приведена схема статического управления семисегментным вакуумно-люминесцентым индикатором. Управление анодами вакуумно-люминесцетного индикатора осуществляется дешифратором, преобразующим двоичный код счетчика в десятичный, через ключи К1 — К7. Принципиальная схема ключа

Рис. 13. 18. Функциональная схема матричного дешифратора

Рис. 13.19. Функциональная схема статического управления семпсегментным вакуумно-люмннесцеитным индикатором (а) и принципиальнаясхема ключа,

упрвляющего одним сегментом (б)

на МДП-транзисторах, управляющего одним анодом-сегментом, показана на рис. 13.19, б. При ивх = 1 транзистор VT1 открыт, a VT2 закрыт. Так как сопротивление канала открытого транзистора VT1 мало, а закрытого VT2 велико, то напряжение анода-сегмента, коммутируемого таким ключом, близко к нулю и этот сегмент не светится. При ивх = 0 открыт транзистор VT2, a VT1 закрыт. Напряжение источника Еа прикладывается почти целиком к соответствующему аноду-сегменту, вызывая его свечение. Подсвечивая различные сегменты, можно с помощью такого люминесцентного индикатора высветить любую цифру от 0 до 9.

Недостатком статического метода управления сегментными люминесцентными индикаторами является резкое увеличение количества ключей при увеличении разрядности индицируемого числа. Такой способ экономически приемлем, если число разрядов не превышает 3. При большем числе разрядов используется мультиплексный метод управления.