- •Введение

- •Элементно-технологическая база эвм.

- •Свойства цифровых элементов определяет ряд параметров (характеристик), знание которых необходимо для правильного проектирования и эксплуатации цифровых устройств.

- •Для цифровых элементов, как и для других, важны также надежность, стоимость допустимые условия эксплуатации и другие.

- •Допустимые напряжения помех

- •Типовые фрагменты цепей

- •Схемы ттл с повышенным быстродействием.

- •Особенности применения элементов ттл (ттлш)

- •Транзисторно-транзистор-транзисторная логика (т-ттл).

- •Элементы эмиттерно-связанной логики.

- •Интегральные логические элементы на униполярных транзисторах.

- •Логические схемы на моп транзисторах одного типа проводимости.

- •Логические интегральные схемы на комплиментарных моп транзисторах.

- •Типовые функциональные узлы цифровых устройств.

- •Триггеры. Основные понятия, классификация.

- •Двухступенчатые триггеры.

- •Триггеры с динамическим управлением.

- •Функциональные узлы комбинационного типа. Мультиплексоры и демультиплексоры.

- •Дешифраторы и шифраторы

- •Шифраторы

- •Преобразователи кодов

- •Счетчики

- •Двоичные счетчики.

- •Регистры и межрегистровые связи.

- •Сумматоры алу.

- •Аккумуляторы, алу.

- •Интегральные запоминающие устройства.

- •Воспроизведение арифметических операций и произвольных функциональных зависимостей.

Логические схемы на моп транзисторах одного типа проводимости.

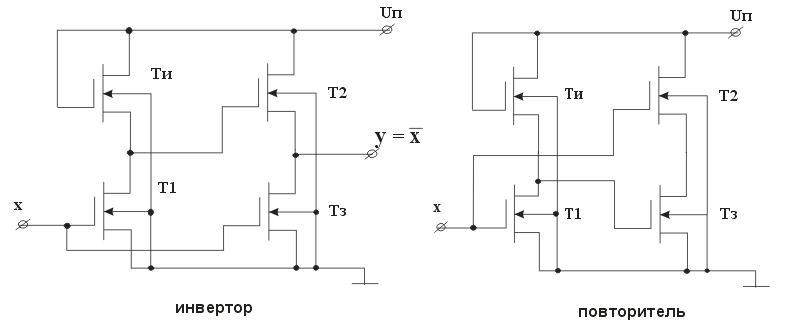

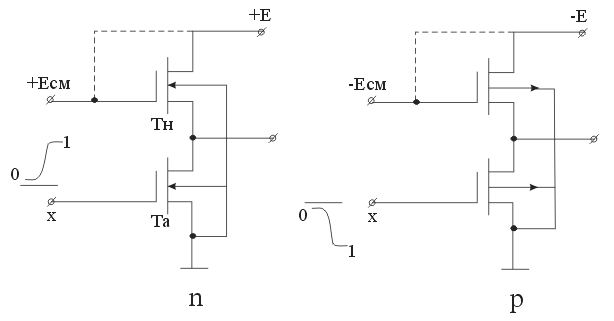

Принципы работы элементов n-МОП и p-МОП удобно проследить на примере инверторов:

В этих схемах исток ключевого – активного транзистора заземляется, а знак питающего напряжения определяется типом МОП транзистора (для p-отрицательное, для n-положительное).

Принципиальное отличие схем на униполярных транзисторах от схем на биполярных заключается в том, что в первых нагрузкой является нормально открытый МОП транзистор. Это существенно упрощает технологию изготовления схем.

Как видно, в элементах p- МОП используется соглашение отрицательной логики. (Логическая единица отображается отрицательным напряжением, модуль которого превышает пороговое напряжение, логический ноль – малым отрицательным напряжением, модуль которого не достигает модуля порогового).

В обеих схемах

транзисторы

![]() являются нагрузочными. Затвор транзистора

– нагрузки подключается к источнику

смещения

являются нагрузочными. Затвор транзистора

– нагрузки подключается к источнику

смещения

![]() ,

который по модулю превышает

,

который по модулю превышает

![]() не менее чем на пороговое напряжение.

Возможно подключение затвора

непосредственно к источнику питания

(пунктир, падает быстродействие схемы).

не менее чем на пороговое напряжение.

Возможно подключение затвора

непосредственно к источнику питания

(пунктир, падает быстродействие схемы).

В обеих схемах при

подаче на вход напряжения, соответствующего

![]() ,

транзистор

,

транзистор

![]() закроется и на выходе будет действовать

напряжение, близкое к

(то есть логическая «1»).

закроется и на выходе будет действовать

напряжение, близкое к

(то есть логическая «1»).

Если же

![]() ,

то

открыт, напряжение на выходе

,

то

открыт, напряжение на выходе

![]() ,

так как сопротивление канала нагрузочного

транзистора

значительно больше сопротивления канала

открытого транзистора:

,

так как сопротивление канала нагрузочного

транзистора

значительно больше сопротивления канала

открытого транзистора:

![]() .

Это неравенство выполнимо лишь при

изготовлении транзисторов с разными

размерами каналов:

.

Это неравенство выполнимо лишь при

изготовлении транзисторов с разными

размерами каналов:

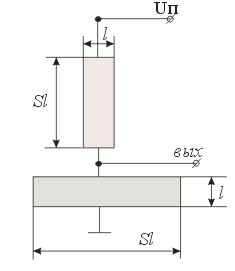

У нагрузочного резистора увеличивают длину канала, у активного – его ширину (на рис. сопротивления отличаются в 25 раз).

Большое входное сопротивление МОП транзисторов позволяет строить логические схемы, используя непосредственное соединение каналов (параллельное, последовательное, смешанное).

При отсутствии

тока через схему (все активные транзисторы

закрыты) напряжение на выходе

![]() ,

что соответствует

,

что соответствует

![]() .

.

Для построения многоступенчатых схем применяют смешанное соединение каналов МОП транзисторов.

Характерные недостатки p(n) МОП схем:

необходимость иметь определенное соотношение между сопротивлением каналов (увеличивает расход площади кристалла и следовательно стоимость элемента). Желательно иметь транзисторы

.

.при

через оба транзистора от источника

питания на общую точку течет статический

ток. Это исключает применение низкоомных

каналов (растет рассеиваемая элементом

мощность). Высокоомность каналов влечет

потерю быстродействия.

через оба транзистора от источника

питания на общую точку течет статический

ток. Это исключает применение низкоомных

каналов (растет рассеиваемая элементом

мощность). Высокоомность каналов влечет

потерю быстродействия.

Время задержки распространения – десятки и сотни наносекунд (частота переключения 1000-50 кГц), потребляемая мощность – десятки мВт/вентиль.

Типичное напряжение питания – 27В.

Нагрузочная способность МОПТ ИС одного типа проводимости достаточно высока (n>10) и ограничивается лишь снижением быстродействия за счет емкости нагрузки Си.

С целью расширения

функциональных возможностей в состав

серии включены буферные схемы (![]() ).

).