Глава 3. Цифровой логический уровень

вторичный сигнал тактового генератора, который сдвинут по фазе относительно первичного (рис. 3.20, а). Временная диаграмма (рис. 3.20, б) обеспечивает четыре начала отсчета времени для дискретных событий:

Нарастающий фронт С1.

Задний фронт С1.

Нарастающий фронт С2.

Задний фронт С2.

Связав различные события с различными фронтами, можно достичь требуемой последовательности выполнения действий. Если в пределах одного такта требуется более четырех начал отсчета, можно сделать еще несколько ответвлений от задающей линии с различным временем задержки.

Рис. 3.20. Тактовый генератор (а); временная диаграмма для тактового генератора (б); порождение асинхронных тактовых импульсов (в)

В некоторых схемах важны временные интервалы, а не дискретные моменты времени. Например, некоторое событие может происходить в любое время, когда уровень импульса С1 высокий, а не на нарастающем фронте. Другое событие может происходить только в том случае, когда уровень импульса С2 высокий. Если необходимо более двух интервалов, нужно обеспечить больше линий передачи синхронизирующих импульсов или сделать так, чтобы состояния с высоким уровнем импульса у двух тактовых генераторов частично пересекались во времени. В последнем_случае можно выделить 4 отдельных интервала: СТ И С2, С1 И С2, С1ИС2иС1 ИС2.

Тактовые генераторы могут быть синхронными. В этом случае время состояния с высоким уровнем импульса равно времени состояния с низким уровнем импульса (рис. 3.20, б). Чтобы получить асинхронную серию импульсов, нужно сдвинуть сигнал задающего генератора, используя цепь задержки. Затем нужно

Память

163

соединить полученный сигнал с изначальным сигналом с помощью логической функции И (см. рис. 3.20, в, сигнал С).

Память

Память является необходимым компонентом любого компьютера. Без памяти не было бы компьютеров, по крайней мере таких, какие есть сейчас. Память используется как для хранения команд, которые нужно выполнить, так и данных. В следующих разделах мы рассмотрим основные компоненты памяти, начиная с уровня вентилей. Мы увидим, как они работают и как из них можно получить память большой емкости.

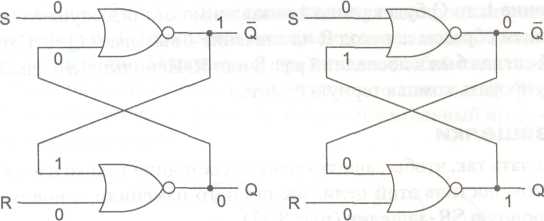

Защелки

Чтобы создать один бит памяти, нам нужна схема, которая каким-то образом «запоминает» предыдущие входные значения. Такую схему можно сконструировать из двух вентилей НЕ-ИЛИ, как показано на рис. 3.21, а. Аналогичные схемы можно построить из вентилей НЕ-И. Мы не будем упоминать эти схемы в дальнейшем, поскольку они, по существу, идентичны схемам с вентилями НЕ-ИЛИ.

А |

В |

НЕ-ИЛИ |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

Рис. 3.21. Защелка НЕ-ИЛИ в состоянии 0 (а); защелка НЕ-ИЛИ в состоянии 1 (б); таблица истинности для функции НЕ-ИЛИ (в)

Схема, изображенная на рис. 3.21, а, называется SR-защелкой. У нее есть два входа: S (setting — установка) и R (resetting — сброс). У нее также есть два комплементарных1 (дополнительных) выхода: Q и Q. В отличие от комбинационной схемы, выходные сигналы защелки не определяются текущими входными сигналами.

Чтобы увидеть, как это осуществляется, предположим, что S=0 и R=0 (вообще они равны 0 большую часть времени). Чтобы провести доказательство, предположим также, что Q=0. Так как Q возвращается в верхний вентиль НЕ-ИЛИ и оба входа этого вентиля равны 0, то его выход, Q, равен 1. Единица возвращается в нижний вентиль, у которого в итоге один вход равен 0, а другой — 1, а на выходе получается Q=0. Такое положение вещей, по крайней мере, состоятельно (рис. 3.21, а).

О т

англ. complementary

—

дополняющий. — Примеч.

пер.

т

англ. complementary

—

дополняющий. — Примеч.

пер.