- •Введение

- •Лабораторная работа №1 Создание проекта в OrCad Capture Создание проекта

- •Сведения о библиотеках системы

- •Лабораторная работа №3

- •Системе сапр OrCad.

- •Лабораторная работа №4 Использование иерархических структур при проектировании сложных устройств в системе OrCad Иерархические блоки

- •Лабораторная работа №5 Синтез и моделирование комбинационных устройств, заданных в табличной форме

- •Порядок выполнения работы

- •Задания к лабораторной работе

- •Лабораторная работа №6 Исследование статических и динамических рисков сбоя.

- •Синхронное логическое моделирование

- •Асинхронное моделирование

- •Порядок выполнения работы

- •Список рекомендуемой литературы

Синхронное логическое моделирование

Синхронное моделирование характеризуется представлением моделей элементов их логическими функциями без учета задержек сигналов. Синхронное моделирование применяется для оценки правильности логического функционирования дискретных устройств без учета переходных

процессов. Процесс моделирования работы проектируемого устройства связан с вычислением значений сигналов на выходах логических элементов схемы по заданным входным сигналам. Моделирование выполняется при каждом изменении сигналов на входах. Преимущественно изменения на входах логических элементов связаны с изменением значений синхросигналов, поэтому и значения выходных сигналов вычисляются для каждого синхросигнала. При этом предполагается, что в промежутке между синхросигналами входные сигналы не меняются, а переходной процесс в устройстве завершается в течение некоторого , меньшего периода повторения тактирующих сигналов.

Синхронное моделирование наиболее удобно использовать для анализа работы комбинационных схем в установившемся режиме. Результат моделирования в этом случае наиболее точно соответствует реальному режиму работы устройства.

Асинхронное моделирование

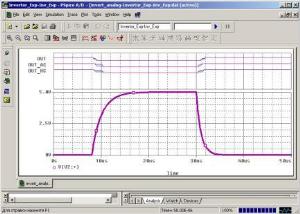

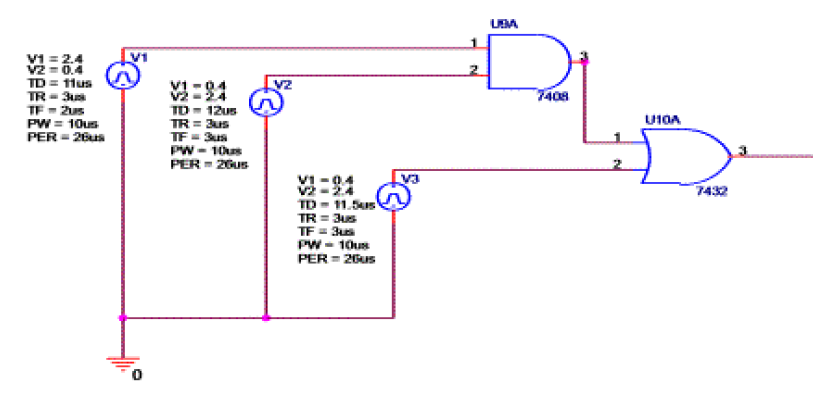

Асинхронный метод моделирования применяется для анализа переходных процессов в логических схемах. В этом методе учитывается время распространения сигналов в элементах и соединительных цепях схемы. Изменение значений выходных сигналов логического элемента происходит с некоторым запаздыванием по отношению к входным сигналам, которое учитывается задержкой в моделях элементов. Каждый элемент характеризуется некоторой средней задержкой, значение которой может меняться в зависимости от режима работы элемента, комбинации входных сигналов, температуры, отклонения в технологии изготовления элемента и т.д. В зависимости от требуемой степени адекватности моделирования учет задержек производится с той или иной степенью детализации. Задержки в линиях связи весьма малы и обычно не учитываются, однако при моделировании устройств с очень высоким быстродействием учитываются и они. Временное рассогласование входных сигналов элемента может привести к появлению ложного сигнала на выходе логического элемента. Такая возможность появления ложных сигналов носит название риска сбоя. Если сигналы на выходе схемы для двух смежных наборов входных воздействий остаются одинаковыми, а во время переходного процесса возможно появление ложного сигнала противоположного значения, то такая ситуация называется статическим риском сбоя.

Порядок выполнения работы

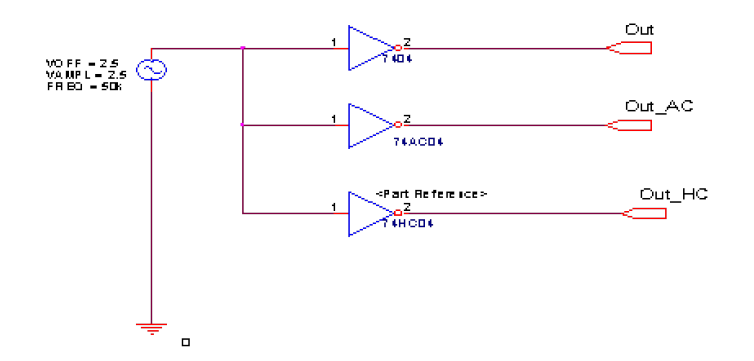

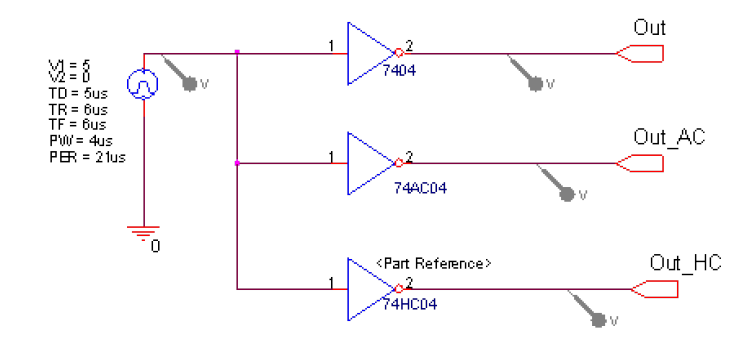

Исследование динамических характеристик цифровых элементов различных серий на примере элементов "НЕ"

1. Создать проект моделирования устройств;

2. Поместить на рабочую поверхность три элемента "НЕ", принадлежащих различным сериям.(Использовать библиотеки 7400.olb, 74ac.olb, 74hc.olb);

3. Подключить к трем элементам один аналоговый источник питания;

Синусоидальный

Импульсный

Экспоненциальный

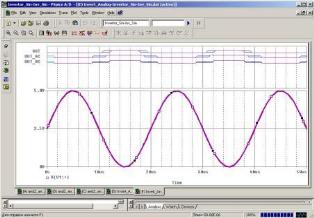

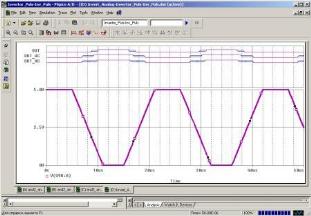

4. Выполнить моделирование устройства;

5. Проанализировать результаты моделирования. Определить различия динамических характеристик элементов приведенных серий.

Подключение синусоидального источника сигнала.

Подключение импульсного источника сигнала.

Подключение экспоненциального источника сигнала.

Моделирование динамических рисков сбоя на примере комбинации элементов "И" и "ИЛИ"

Цель: Получение динамического и статического сбоя на временных диаграммах системы ORCAD для приведенной схемы.