Методичка - Микропроцессоры микроЭВМ

.pdfПовторение первого и второго шагов до тех пор, пока не будут проверены все 8 битов множителя (табл. 23).

Результат составляет 09D8H. Этот процесс работает по следующим причинам. Результат умножения может быть записан следующим образом:

BIT7•M•27+ BIT6•M•26+…+ BIT0•M•20,

где BIT0…BIT7 представляет собой бит множителя (каждый равен 0 или 1), a M является

множимым. |

|

Например: |

|

множимое |

= 00000101B; |

множитель |

= 00001010B; |

0•0АН•27 + 0•0АН•26 + 0•0АН•25 + 0•0АН•24 + 0•0АН•23 + 1•0АН•22 + + 0•0АН•21 + 1•0АН•20 = 00101000 + 00001010 = 00110010 = 5010.

Прибавление множимого к старшему байту результата равносильно прибавлению M•28 к полному 16-битовому результату; сдвиг 16-битового результата на один бит вправо эквивалентен умножению результата на 2-1 (делению на 2).

Таким образом, в шаге 1 имеем: (BIT0•M•28) •2-1.

В шаге 2 имеем: ((BIT0•M•28)•2-1+ (BIT1•M•28))•2-1= BIT0•M•26 + BITl•M•27; и так далее до тех пор, пока в шаге 8 получим:

BIT0•M•20 + BIT1•M•21 +. . . + BIT7•M•27, что является правильным результатом.

Аналогичная процедура используется для деления 16-битовых чисел без знака. Вместо сложения используется вычитание, а вместо сдвига вправо используется сдвиг влево.

4. Задание к лабораторной работе

Составить, отладить и продемонстрировать программу в соответствии с вариантом. При написании программы учесть:

1.Результат работы программы сложения (вычитания, умножения, деления) должен быть представлен в системе счисления одного из исходных чисел.

2.Исходные данные и результат работы программы должны занимать в памяти набор смежных байтов.

5.Содержание отчета

Отчет должен содержать: листинг программы и блок-схему программы.

6. Контрольные вопросы

6. 1. Какие бывают биты условий?

6. 2. На что воздействуют биты условий?

6. 3. Какие команды устанавливают или сбрасывают бит P (S, Z, С, C’)?

6. 4. Как выполняется многобайтное сложение (многобайтное вычитание, десятичное сложение, десятичное вычитание, умножение, деление)?

6. 5. Приведите пример многобайтных вычислений с использованием команды

DAA.

6. 6. Укажите преимущества и недостатки алгоритма умножения с использованием сдвига по сравнению с другими алгоритмами умножения.

31

ЛАБОРАТОРНАЯ РАБОТА № 6

Прямой доступ к памяти

1.Цель работы

1.Исследование способов отображения информации в малогабаритных устройст-

вах.

2.Изучить принцип динамической индикации.

3.Изучить методы организации прямого доступа к памяти.

4.Разработать программу, генерирующую на цифровом дисплее подвижное изображение.

2.Задание на лабораторную работу

Разработать программу, создающую на дисплее изображение в соответствии с заданием (табл. 24).

|

Таблица 24. Задания к лабораторной работе № 6 |

|

|

№ |

Задание |

1 |

Написать на экране УОУ название специальности, создав бегущую строку |

2 |

Вывести с правой стороны на экран свое имя, помигать надписью и по буквам пога- |

|

сить надпись |

3 |

Создать имитацию движения шарика для пинг-понга |

4 |

Воспроизвести на экране часы реального времени |

5 |

Продемонстрировать на экране построчную таблицу умножения на 4 |

6 |

Салют |

7 |

Сымитировать на экране УОУ движущееся перекрестье прицела |

8 |

Написать программу поочередного зажигания (гашения) сегментов |

3. Краткие сведения из теории

Прямой доступ памяти (ПДП) – это метод организации доступа устройств вводавывода к памяти процессора независимо от хода исполнения программы. Для осуществления ПДП устройству управления вводом-выводом или каналу, которому предварительно была выдана команда на обмен с памятью некоторым массивом данных, временно передается управление шинами адреса, данных и шиной управления, благодаря чему отдельное слово (или группа слов) может быть записано в память или считано из нее в устройство ввода-вывода.

Таблица 25. Причины эффективности ПДП

№ |

Прямой доступ к памяти |

Программная реализация пересылки группы |

|

|

данных |

1 |

Аппаратная реализация задачи пе- |

Дополнительные команды инкремента (декре- |

|

ребора адресов |

мента) регистра, отвечающего за адрес |

2 |

Жесткий алгоритм действий. Пере- |

Каждый цикл обращения к памяти или к уст- |

|

сылка занимает два цикла: |

ройству ввода-вывода предваряется циклом |

|

обращения к памяти |

чтения кода команды. Выполняются команды |

|

обращение к устройству ввода- |

изменением текущего адреса, контроля оконча- |

|

вывода |

ния массива |

32

ПДП обычно используют для быстрой пересылки группы данных между памятью и устройством ввода-вывода. ПДП значительно эффективнее (быстрее) программной реализации пересылки группы данных (табл. 25).

Всемействе микросхем процессора К580ВМ80А за реализацию режима ПДП отвечает контроллер К580ИК57.

ВУОУ метод ПДП используется для вывода информации на дисплей. За каждый цикл ПДП осуществляется пересылка одного байта. Диапазон адресов 83F8H…83FFH содержит код информации регулярно отображаемой на экран УОУ. Программная запись информации в эту область памяти вызывает ее автоматическое отображение на экране УОУ в режиме ПДП. Экран УОУ представлен 8 знакоместами, работающими в динамическом режиме. Динамический режим работы создается при помощи поочередного зажигания каждого знакоместа. Полный цикл отображения информации на индикаторе занимает 8 шагов. Время полного цикла отображения информации на индикаторе меньше времени реакции человеческого глаза на ее изменение. Таким образом, создается иллюзия статичного изображения на индикаторе УОУ.

Каждое знакоместо состоит из набора светодиодов красного цвета образующих один цифробуквенный индикатор (рис. 5). Для вывода на дисплей цифры 5 (сегменты a, c, d, f, – зажжены; сегменты b, e, h – погашены) необходимо записать в ячейку памяти соответствующего знакоместа комбинацию нулей и единиц: 10110110 (0B6H).

|

а |

|

|

|

|

|

|

|

|

|

|

f |

g |

b |

Номер бита в слове |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

e |

|

c |

|

|

|

|

|

|

|

|

|

|

Обозначение сегмен- |

а |

b |

c |

d |

e |

f |

g |

h |

||

|

|

h |

|||||||||

|

d |

та на индикаторе |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5. Сегменты индикатора. Соответствие сегментов индикатора информационному слову

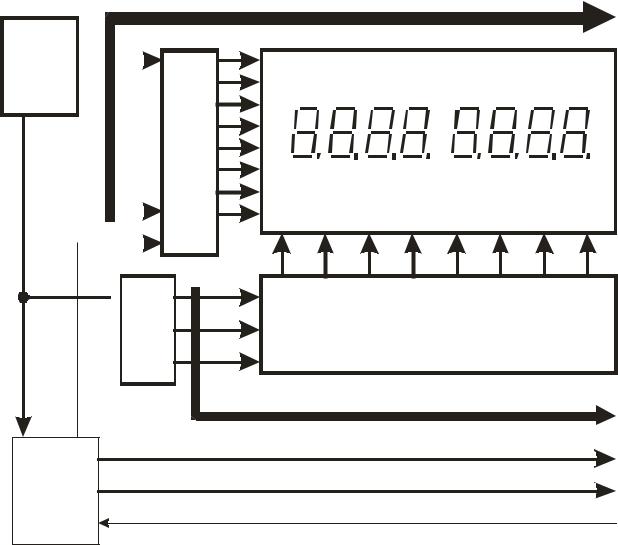

Упрощенная схема контролера прямого доступа к памяти учебно-отладочного устройства (КПДП УОУ) состоит из генератора, счетчика, устройства управления, регистра, дешифратора номера знакоместа (рис. 6).

Работа КПДП УОУ синхронизируется генератором с частотой около 1,2 кГц. Сигнал с выхода генератора поступает на устройство управления контроллером, которое вырабатывает сигнал «запрос прямого доступа памяти» (ЗПДП) для микропроцессора. По сигналу ЗПДП микропроцессор заканчивает выполнение текущей команды и переходит в режим ожидания (шина данных, шина адреса, шина управления переводится в высокоимпедансный режим (третье состояние), выставляется сигнал «Подтверждение прямого доступа к памяти» (ППДП)). Данные трех разрядов счетчика поступают на шину адреса (А0…А2). Прочие разряды шины адреса (А3…А15) при помощи резисторов притягиваются к состоянию 1000 0011 1111 1*** (83F8H). Звездочками обозначены разряды адреса А0…А2. Устройство управления сигналом «чтение памяти» (ЧТПМ) производит вывод из ячейки памяти, адрес которой установлен на шине адреса, данных D0…D7 на шину данных. По сигналу «строб» данные помещаются в регистр. Содержимое регистра определяет комбинацию светодиодов зажженных в текущий момент времени. Привязка считываемой ячейки памяти к знакоместу дисплея производится с помощью дешифратора, преобразующего код трех младших разрядов адреса ячейки памяти в код выбора знакоместа. По окончании фиксации данных в регистре сигналы «строб», ЧТПМ, ЗПДП снимаются. В ответ на снятие сигнала ЗПДП микропроцессор снимает сигнал ППДП, выходит из режима ожидания и продолжает выполнять программу со следующей команды.

33

Генератор 1,2 кГц |

|

|

D0 |

||

|

|

. |

|

|

. |

|

|

. |

|

|

D7 |

Строб |

|

|

|

||

|

|

|

Счетчик

Счетчик

Регистр

A0

А1

А2

Шина данных

Индикатор

Дешифратор

Устройство управления

Шина адреса

Чтение

Запрос ПДП

Подтверждение ПДП

Рис. 6. Схема контроллера прямого доступа к памяти УОУ

4. Задание к лабораторной работе

Составить, отладить и продемонстрировать программу в соответствии с вариантом. При написании программы учесть:

1.В режиме «Отладка» УОУ выполняет дополнительные программные действия, что замедляет выполнение учебной программы. В режиме «Прогон» время выполнения отлаживаемой программы соответствует ожидаемому времени. Рекомендуемый режим работы УОУ – «Прогон».

2.Информация, подготовленная вашей программой, отображается на экране УОУ до тех пор, пока управление УОУ не передано встроенному монитору (учебная программа закончила работу).

3.Для создания визуального эффекта, смена информации на экране УОУ должна происходить через паузу (интервал времени). В УОУ отсутствуют механизмы автоматического вывода микропроцессора из режима ожидания. Реализация паузы возможна только программным путем. На время программной паузы микропроцессор занят выполнением цикла холостых команд. По завершению цикла холостых команд (пауза закончилась) программа может заменить содержимое отображаемых ячеек памяти на новые данные. Далее снова следует пауза и вновь – смена информации. Цикл холостых команд может содержать процедуру уменьшения регистровой пары от заданного числа до нуля.

34

5. Содержание отчета

Отчет должен содержать: листинг программы и блок-схему программы.

6. Контрольные вопросы

6. 1. Для чего предназначен режим прямого доступа к памяти?

6. 2. Почему перенос массива данных в режиме прямого доступа к памяти быстрее, чем программная реализация переноса массива данных?

6. 3. Как работает контроллер прямого доступа к памяти УОУ?

6. 4. Какова схема включения универсального контроллера прямого доступа к памяти КР580ИК57?

6. 5. Какие принципы программирования универсального контроллера прямого доступа к памяти КР580ИК57?

6. 7. Как соответствуют данные в памяти по адресам 87F8H…88FFH и информация, отображаемая на индикаторе УОУ.

35

ЛАБОРАТОРНАЯ РАБОТА № 7

Программирование внешних устройств

1.Цель работы

1.Изучить правила программирования внешних устройств.

2.Ознакомится с методами синтеза широтно-модулированного сигнала.

3.Освоить правила использования и программирования интервального таймера КР580ВИ53.

4.Изучить простейшие устройства синтеза тонального звукового потока.

5.Освоить методику расчета длительности исполнения программного кода.

2.Задание на лабораторную работу

Разработать программу, генерирующую на внешнем устройстве музыкальный или телеграфный поток в соответствии с заданием преподавателя (табл. 26).

|

Таблица 26. Задание к лабораторной работе № 7 |

|

|

|

Тип внешнего устройства |

№ |

Задание |

|

1 |

Создать телеграфный поток, содержащий свое имя, фа- |

«Триггер» |

|

милию, отчество |

«Триггер» |

2 |

Создать музыкальный поток, содержащий 1 куплет мело- |

|

|

дии песни «В лесу родилась елочка» |

«Таймер КР580ВИ53» |

3 |

Создать телеграфный поток, содержащий свое имя, фа- |

|

|

милию, отчество |

«Таймер КР580ВИ53» |

4 |

Создать музыкальный поток, содержащий 1 куплет мело- |

|

|

дии песни «В лесу родилась елочка» |

|

Требование к музыкальному потоку (табл. 32):

1.Мелодия должна быть узнаваема.

2.В каждый момент времени должна звучать только одна нота.

3.По окончании проигрывания мелодии необходимо установить паузу размером в

2с. После паузы мелодия должна начать играть сначала. Требования к телеграфному потоку (табл. 31):

1.Тон точки выше тона тире.

2.Длина тире равна длительности трех точек.

3.Пауза между элементами одной буквы – 1 точка.

4.Пауза между буквами – 1 тире.

5.Пауза между словами – 3 тире.

3.Краткие сведения из теории

Функционирование микропроцессора определяется исполняемыми командами. Выборка очередной команды из памяти осуществляется по содержимому регистра адреса. Все команды состоят из одного, двух или трех байтов. В зависимости от типа каждая команда выполняется за время от одного до пяти машинных циклов (МЦ), в каждом из которых осуществляется обращение к одной ячейке памяти или одному устройству вводавывода.

Исключение составляет команда DAA, которая выполняется за 3 МЦ, но обращение к памяти происходит только в первом МЦ. МЦ может длиться 3, 4 или 5 машинных тактов (МТ). Число МТ в МЦ определяется кодом команды. Длительность каждого МТ

36

определяется как интервал между положительными фронтами импульсов синхронизации. Частоту импульсов синхронизации микропроцессора КР580ВМ80А можно принять равной 2,5 МГц.

Упрощенная временная диаграмма обращения к внешнему устройству состоит из совокупности МЦ «чтение памяти», «запись в память», «чтение внешнего устройства», «запись во внешнее устройство» (рис. 7).

При построении временной диаграммы следует учесть:

1.Информация на шинах микропроцессора не может появиться мгновенно. На временной диаграмме это обстоятельство иллюстрируется пологими фронтами появления

иснятия сигналов.

2.Шина адреса (ША) и шина данных (ШД) на временной диаграмме изображена условно. Действительные данные обозначены двумя параллельными линиями, третье состояние обозначено линией посередине.

3.При чтении данных сначала устанавливается адрес (ША) и только после появления сигнала чтения (ЧТПМ, ЧТВУ) на шине данных (ШД) появляется информация для считывания.

4.При записи сигнал ЗП (ЗППМ, ЗПВУ) должен появиться только при установившейся информации на шинах ША и ШД.

|

|

ША |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

ШД |

|

|

|

|

|

|

|

|

|

|

|

|

ША |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ШД |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ЧТПМ |

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ЧТПМ |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

ЗППМ |

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЗППМ |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

ЧТВУ |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЧТВУ |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

ЗПВУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЗПВУ |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

ША |

|

|

|

|

|

|

|

|

ША |

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

ШД |

|

|

|

|

|

|

|

|

|

ШД |

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

ЧТПМ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

ЧТПМ |

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

ЗППМ |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЗППМ |

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

ЧТВУ |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЧТВУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

ЗПВУ |

|

|

|

|

|

|

|

|

ЗПВУ |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

в |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

г |

|

||||||

Рис. 7. Временные диаграммы МЦ:

а – чтение из памяти, б – запись в память, в – чтение внешнего устройства, г – запись во внешнее устройство

Микропроцессор К580ВМ80 осуществляет связь с «внешним миром» через 256 входных и 256 выходных устройств (устройств ввода-вывода). Выходное устройство работает с микропроцессором через байты данных посылаемых «на» или получаемых «из» аккумулятора. Каждому устройству присваивается уникальный номер от 0 до 255=0FFH, являющимся его адресом. Команды, выполняющие ввод данных в аккумулятор и вывод данных из аккумулятора, – соответственно IN (AA) и OUT (AA), где АА – 8-и битный адрес устройства ввода-вывода. На 16-битной шине адреса 8-битый адрес устройства вводавывода дублируется в 8 старших и 8 младших разрядах шины.

37

Выполнение лабораторной работы предполагает использование одного из двух внешних устройств генерирования звукового потока. В лабораторной работе используется два типа внешних устройств «Таймер» (рис. 8) и «Триггер» (рис. 9). Устройства выполнены в виде сменных модулей, устанавливаемых в разъем на передней части УОУ.

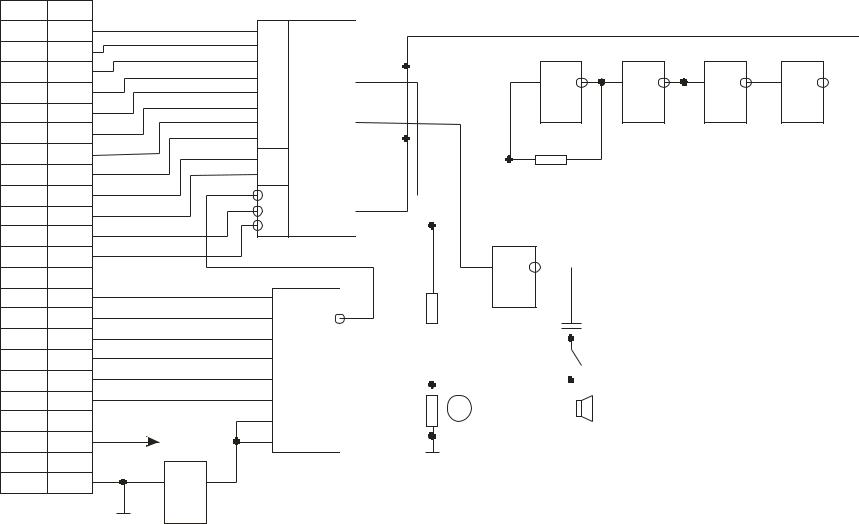

3. 1. Внешнее устройство «Таймер»

Внешнее устройство «Таймер» (рис. 8) выполнено на базе интервального таймера К580ИК53. В качестве дешифратора адреса внешнего устройства использована микросхема DD3. На элементах микросхемы DD2 собран генератор тактовых импульсов частотой 2,5 МГц. Выход первого канала через инвертор подключен к излучателю. Сигнал на излучатель попадает в случае нажатия кнопки S1. Кнопка расположена на боковой поверхности модуля.

В адресном пространстве внешнее устройство «Таймер» занимает адреса с 0FCH по 0FFH, причем командное слово записывается по адресу 0FFH.

Добиться звукового сигнала возможно при программировании соответствующего канала интервального таймера в режим «меандр», с заданием такого коэффициента деления, при котором частота выходного сигнала лежит в диапазоне 200…7000 кГц.

Пример программы проверки работоспособности внешнего устройства «Таймер» (листинг 2) содержит команду 76H, переводящую первый канал таймера в режим «меандр» с двухбайтным заданием коэффициента деления в 16-ой системе счисления. Для получения выходного сигнала частотой 1 кГц 2500000/2500=1000 Гц в счетчик необходимо послать число 2500 в десятичной системе счисления (младшая часть = 00, старшая часть = 25).

Листинг 2. Генерация однотонного сигнала на «Таймере»

Метка |

Мнемоника |

Примечание |

START: |

MVI A,76H |

Командное слово 76H |

|

OUT 0FFH |

Загрузка командного слова |

|

MVI A,00H |

Младшая часть делителя |

|

OUT 0FDH |

Запись в канал 1 |

|

MVI A,25H |

Старшая часть делителя |

|

OUT 0FDH |

Запись в канал 1 |

|

RST 32 |

|

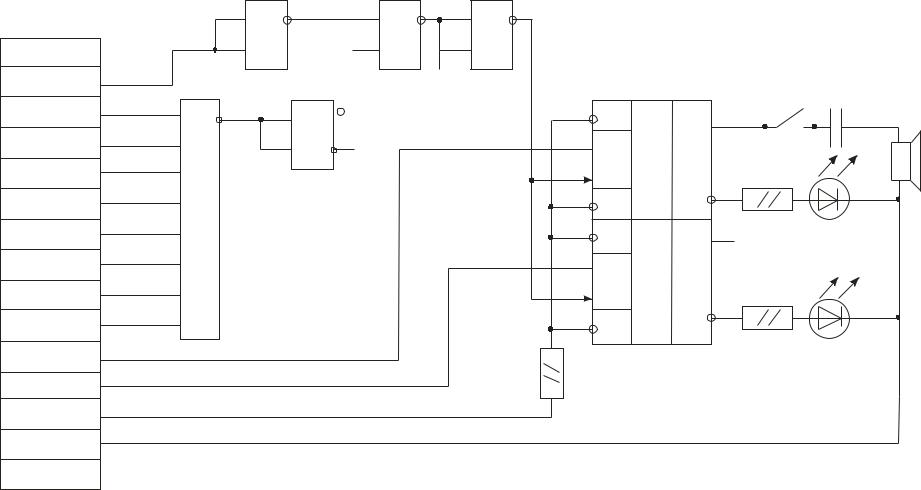

3. 2. Внешнее устройство «Триггер»

Внешнее устройство «Триггер» (рис. 9) выполнено на базе D-триггера. Дешифратор адреса (DD1) при появлении высокого уровня сигнала на разрядах адреса А0…А7 (адрес 0FFH) выставляет низкий уровень. На элементах микросхемы DD2 сигнал c выхода дешифратора смешивается с сигналом ЗПВУ и формирует сигнал «строб записи информации в триггер». Сигнал «строб записи информации в триггер» появляется только при обращении по адресу 0FFH сопровождаемом сигналом ЗПВУ. По сигналу «строб записи информации в триггер» данные с двух младших разрядов ШД запоминаются в триггере. Для генерации звука используется бит D0. Сигнал на излучатель попадает в случае нажатия кнопки S1. Кнопка расположена на боковой поверхности модуля.

Генерация звука на излучателе возможна, если в триггер поочередно записывается 0, 1, 0, 1 и т. д. В этом случае напряжение, подводимое к излучателю, похоже на синусоидальный сигнал. Период звукового сигнала равен сумме времени фиксации в триггере 0 и времени фиксации в триггере 1.

38

|

X1 |

|

|

|

Цепь |

Конт. |

|

|

8 |

D0 |

Б4 |

|

|

|

|

|

7 |

||

D1 |

Б5 |

|

|

|

|

|

6 |

||

D2 |

Б6 |

|

|

5 |

D3 |

Б7 |

|

|

4 |

|

|

3 |

||

D4 |

Б8 |

|

|

|

|

|

2 |

||

D5 |

Б9 |

|

|

1 |

D6 |

Б10 |

|

|

19 |

D7 |

Б11 |

|

|

20 |

|

|

21 |

||

A0 |

Б1 |

|

|

|

|

|

23 |

||

A1 |

A1 |

|

|

|

|

|

22 |

||

ЗпВу |

Б13 |

|

|

|

ЧтВу |

Б12 |

|

|

|

39 |

A7 |

|

|

|

A7 |

|

|

|

|

A6 |

A6 |

|

|

|

A5 |

A5 |

|

|

|

A4 |

A4 |

|

|

|

A3 |

A3 |

|

|

|

A2 |

A2 |

|

|

|

+5В |

А22 |

+5В |

|

|

|

DD2.6 |

|

||

|

|

|

|

|

GND |

А21 |

13 |

1 |

12 |

|

|

|

||

|

|

GND |

|

|

DD1

D0 |

|

|

D1 |

|

|

D2 |

|

|

D3 |

|

|

D4 |

3 |

|

D5 |

5 |

|

И |

||

D6 |

||

В |

||

D7 |

||

0 |

||

8 |

||

A0 |

5 |

|

К |

||

A1 |

|

|

CS |

|

|

WR |

|

|

RD |

|

DD3

21 &

3

4

5

6

11

12

OUT0 |

10 |

|

|

|

|

|

|

|

|

|

DD2.4 |

|

|

DD2.3 |

|

|

|

DD2.2 |

|

|

DD2.1 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

CLK0 |

9 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

2 |

3 |

1 |

4 |

5 |

1 |

6 |

9 |

1 |

8 |

|||||

11 |

|

|

|

|

|

|

1 |

|

|

|

|||||||||||||||||||

CATE0 |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

CLK1 |

15 |

|

|

|

|

|

|

|

|

|

R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

CATE1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C3 |

|

|

|

|

|

|

|

|

||

|

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CLK2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CATE2 |

16 |

|

|

|

|

|

|

|

DD2.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R1 - 2k0 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

11 1 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2 - 200 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

8 |

|

|

|

|

R1 |

|

|

|

C2 |

|

|

|

|

|

|

R3 - 2k0 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 - 10.0 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

C2 - 0.1 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C3 - 680p |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

R |

3 |

+ |

|

|

+ |

|

|

|

|

BA1 |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

C1 |

V |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выводмикросхемы DD1-12, DD2-7, DD3-7 к GND Выводмикросхемы DD1-24, DD2-14, DD3-14 к +5В

Рис. 8. Выносное устройство «Таймер»

»Триггер« устройства внешнего работоспособности проверки программы Пример внешнему к обращениями между паузу задающую ,подпрограмму содержит 3) листинг( -со цикл Каждый .шагов 255 из цикла счет за реализована Пауза .»Триггер« устройству 40

Цепь |

Конт. |

IOW |

Б12 |

А0 |

Б1 |

А7 |

А7 |

А6 |

А6 |

А5 |

А5 |

А4 |

А4 |

А3 |

А3 |

А2 |

А2 |

А1 |

А1 |

D0 |

Б4 |

D1 |

Б5 |

+5В |

А22 |

GND |

A21 |

Rese t |

A16 |

|

|

|

|

|

DD2.1 |

|

|

DD2.3 |

|

|

DD2.2 |

|

|

|

|

|

|

|

|

|

|

1 |

& |

3 |

9 |

& |

8 |

4 |

& |

6 |

|

|

|

|

|

|

|

|

|

2 |

|

|

10 |

|

|

5 |

|

|

|

|

|

|

|

|

|

12 |

DD1.1 |

|

DD2.4 |

|

|

|

|

|

|

|

DD3 |

|

|

S1 |

|

|

|

& |

8 |

12 |

& |

|

|

|

|

|

1 |

R |

Т |

|

5 |

C1 |

BA1 |

||

|

|

|

|

|

Q |

|

|||||||||||

11 |

|

|

13 |

11 |

|

|

|

|

|

2 |

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

1 |

|

|

|

|

|

|

|

|

|

3 |

C |

|

|

|

R2 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|||

|

|

|

|

|

|

|

|

|

4 |

S |

|

|

|

|

|

||

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

13 |

R |

Т |

Q |

8 |

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

12 |

D |

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

11 |

C |

|

|

|

R3 |

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|||

|

|

|

|

|

|

|

|

|

10 |

S |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

R1 |

|

|

|

|

|

|

|

Вывод14 микросхемы DD1, DD2, DD3 подсоединитьк +5В Вывод7 микросхемыDD1, DD2, DD3 подсоединить кGND

Рис. 9. Выносное устройство «Триггер»