- •Компоненты микропроцессора

- •3 Стадии процесса при подаче напряжения в схему:

- •1)Относительная простота схемного решения

- •Мультиплексоры

- •Дешифраторы-демультиплексоры

- •Одноразрядные сумматоры

- •4.1.2 Многоразрядные сумматоры

- •Параллельные сумматоры с параллельным переносом

- •Регистры сдвига

- •Реверсивные регистры сдвига

1)Относительная простота схемного решения

Возможность хранения информации.

Возможность передачи информации после установившихся информационных вводах.

2)Открытость входа и выхода на время действия тактового импульса(опасность дребезга) Неопределённость входа при незакончившихся переходных процессах в элементах. Наличие запрещенных входных информационных комбинаций

!Ширина импульса не должна быть меньше времени процессов дельта t

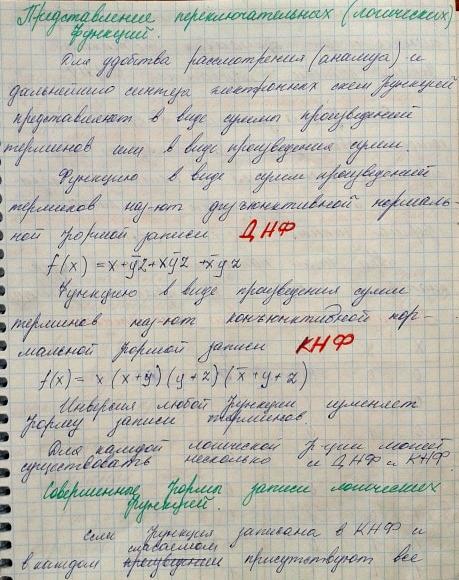

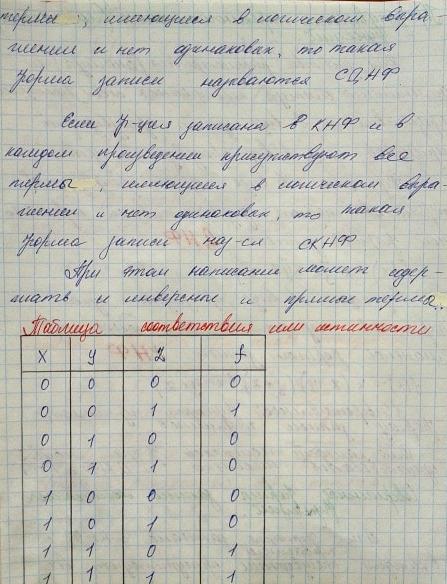

Логической ( булевой) функцией (или просто функцией) n переменных y = f(x1, x2, …, xn) называется такая функция, у которой все переменные и сама функция могут принимать только два значения: 0 и 1.

Вопрос №11.

Комбинационные схемы. D-Триггеры. Логические функции. Таблицы истинности. Временные диаграммы.

Комбинационные схемы. Обработка входной информации Х в выходную У в любых схемах ЭВМ обеспечивается преобразователями или цифровыми автоматами двух видов: комбинационными схемами и схемами с памятью.

Комбинационные схемы - это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х). Топология Локальные сети Коаксиальные кабели

Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует.

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др.

D-Триггеры. Триггеры относятся к классу последовательных элементов. Выход зависит не только от потенциалов на их информационных входах, но и от последовательности их задания.

Триггеры различают по функциональному признаку: R-S ,D-T,J-k и др.

По способу управления:

-Асинхронные (запись информации в асинхронный триггер осуществляется в произвольный момент времени непосредственно с поступлением информационного сигнала на 1 из установочных входов триггера)

-Тактируемые(помимо информационных входов содержат один или несколько синхронизирующих входов . Запись информации в такие триггеры осуществляется только при подаче синхронизирующего импульса (С). В свою очередь, синхронные триггеры подразделяются на триггеры, работающие по уровню С – потенциальные триггеры и на триггеры динамического типа, срабатывающие поначалу или концу синхроимпульса.) (есть ещё 1 тактовый вход ,а выход, только когда есть тактовый сигнал).

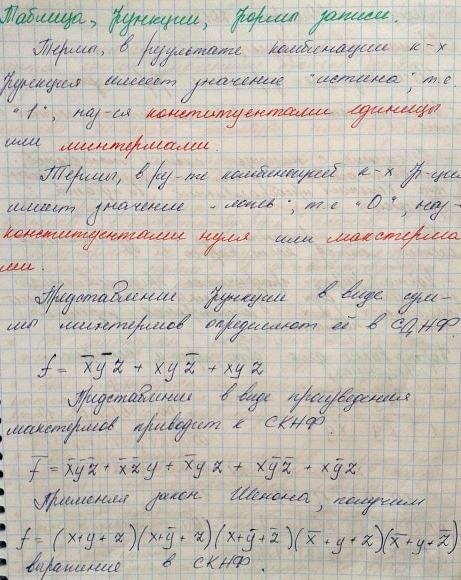

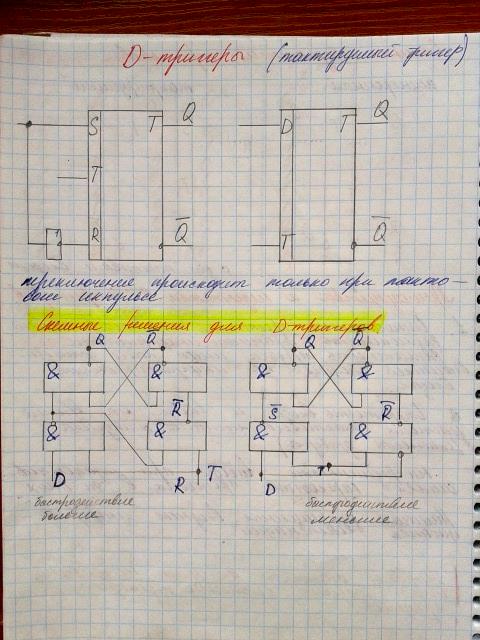

D-триггер

Особенности:

1)Переключение происходит если есть тактовый импульс. 2)работает симфазно вход и выход

3)данные защёлкиваются ло прихода нового тактового импульса

4)происходит задержка

Преимущества и недостатки D –триггеров

1)Относительная простота схемного решения.

Возможность хранения информации Возможность передачи информации после установившихся процессов на информационных входах

Триггер-защёлка(спадом тактового импульса

Триггер с задержкой

Отсутствие запрещённых входных информационных комбинаций.

Недостаток

2)Открытость входа и выхода на время действия тактового импульса

Имеет лишь один информационный вход, называемый входом D, Вход С управляющий и служит для подачи синхронизирующего сигнала.

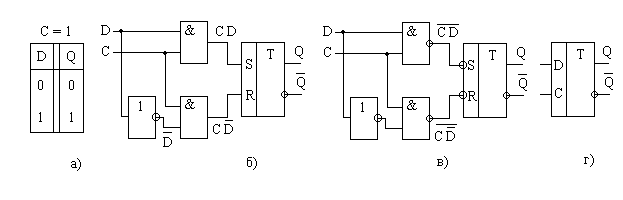

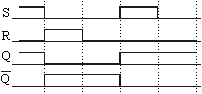

Функционирование D-триггера определяется таблицей состояний (рис. 4.4,а). Как видно из таблицы, при C = l триггер устанавливается в состояние, определяемое логическим уровнем на входе D (при C = 0 он сохраняет ранее установленное состояние Q0). Такое функционирование может быть описано логическим выражением

(4.4)

![]()

рис

4.4

На рис. 4.4,б представлены логические структуры D-триггера, состоящего из асинхронного RS-триггера с логическими элементами на входах. При C = 0 на выходах элементов И (И-HE) образуются пассивные для входов асинхронного RS-триггера уровни. При C = l уровень, поданный на информационный вход D, создает активный уровень либо на входе R (при D = 0) либо на входе S (при D = l) асинхронного RS-триггера, и триггер устанавливается в состояние, соответствующее логическому уровню на входе D). Таким образом, D-триггер воспринимает информацию со входа D при C = l и затем ее может хранить неопределенно длительное время, пока C = 0. На рис. 4,г показано символическое изображение D-триггера.

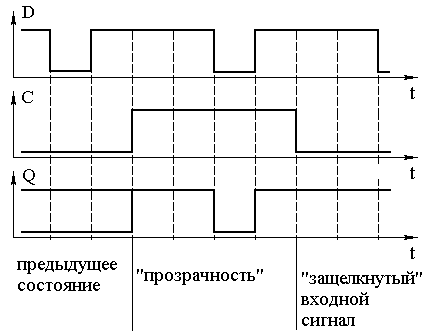

Временные диаграммы D-триггера: Ещё одно название таких триггеров, пришедшее из иностранной литературы - триггеры-защёлки. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке. По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название – триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Вопрос №12.

Комбинационные схемы. T-Триггеры. Логические функции. Таблицы истинности. Временные диаграммы.

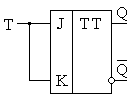

T триггер — это счетный триггер. У T триггера имеется только один вход. После поступления на этот вход импульса, состояние T триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T триггер снова сбрасывается в исходное состояние.

T триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью

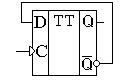

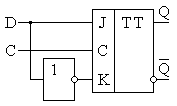

T триггер можно синтезировать из любого двухступенчатого триггера. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.

Рисунок 1. Схема T триггера, построенная на основе D триггера

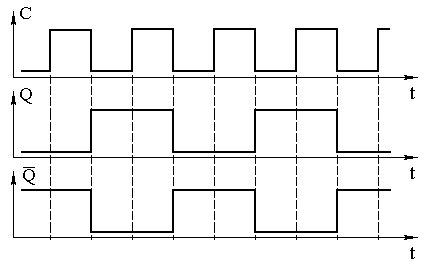

Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Рисунок 2. Временные диаграммы T триггера

Рисунок 2. Временные диаграммы T триггера

Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 3.

T-триггер синхронный T Q(t) Q(t+1)

0 0 0

0 1 1

1 0 1

1 1 0

Комбинационные схемы - это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х). Топология Локальные сети Коаксиальные кабели

Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует.

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др.

Триггеры относятся к классу последовательных элементов. Выход зависит не только от потенциалов на их информационных входах, но и от последовательности их задания. Триггеры различают по функциональному признаку: R-S ,D-T,J-k и др.

По способу управления:

-Асинхронные (запись информации в асинхронный триггер осуществляется в произвольный момент времени непосредственно с поступлением информационного сигнала на 1 из установочных входов триггера)

-Тактируемые(помимо информационных входов содержат один или несколько синхронизирующих входов . Запись информации в такие триггеры осуществляется только при подаче синхронизирующего импульса (С). В свою очередь, синхронные триггеры подразделяются на триггеры, работающие по уровню С – потенциальные триггеры и на триггеры динамического типа, срабатывающие поначалу или концу синхроимпульса.) (есть ещё 1 тактовый вход ,а выход, только когда есть тактовый сигнал)

Вопрос №13.

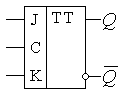

Комбинационные схемы. JK-Триггеры. Логические функции. Таблицы истинности. Временные диаграммы.

Комбинационные схемы - это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х).

Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует.

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др.

Триггеры относятся к классу последовательных элементов. Выход зависит не только от потенциалов на их информационных входах, но и от последовательности их задания. Триггеры различают по функциональному признаку: R-S ,D-T,J-k и др.

А) R-S-триггеры (R – С – S – триггеры) или триггеры с установочными входами. Они являются основой для построения статических запоминающих устройств, и нашли широкое применение для устранения эффекта «дребезга» контактов. Б) Т-триггеры (счетные триггеры). Являются основой для построения двоичных счетчиков или используются в качестве делителей частоты. В) D-триггеры (триггеры задержки). Используются в качестве построения регистров хранения и регистров сдвига. Являются неотъемлемой составляющей частью микропроцессора. Г) J-K-триггеры (или универсальные триггеры). Свое название получили потому, что с помощью них можно создать любой из вышеперечисленных триггеров.

По способу управления:

-Асинхронные (запись информации в асинхронный триггер осуществляется в произвольный момент времени непосредственно с поступлением информационного сигнала на 1 из установочных входов триггера)

-Тактируемые(помимо информационных входов содержат один или несколько синхронизирующих входов . Запись информации в такие триггеры осуществляется только при подаче синхронизирующего импульса (С). В свою очередь, синхронные триггеры подразделяются на триггеры, работающие по уровню С – потенциальные триггеры и на триггеры динамического типа, срабатывающие поначалу или концу синхроимпульса.) (есть ещё 1 тактовый вход ,а выход, только когда есть тактовый сигнал)

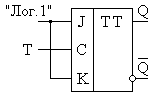

JK-триггер. JK-триггер относится к двухвходовым устройствам и функционирует по правилам, похожим на правила функционирования RS-триггера. Отличие состоит в том, что в JK-триггере все состояния являются определенными. Можно провести аналогию входов JK- и RS-триггеров: вход K JK-триггера выполняет функцию входа R RS-триггера, а вход J JK-триггера – функцию входа S RS-триггера. При этом, если в RS-триггере комбинация единичных значений входов R и S является запрещенной, то в случае аналогичной комбинации J- и K-входов, JK-триггер меняет свое состояние на противоположное. Правило работы асинхронного JK-триггера можно сформулировать следующей таблицей переходов:

tn |

tn+1 |

|

Kn |

Jn |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

Выполнив действия, аналогичные действиям по нахождению логической функции RS-триггера, можно определить выражение для Qn+1 асинхронного JK-триггера

![]() .

.

Наибольшее распространение получили тактируемые или синхронные JK-триггеры, работа которых задается таблицей переходов:

tn |

tn+1 |

||

Cn |

Kn |

Jn |

Qn+1 |

0 |

0 |

0 |

Qn |

0 |

0 |

1 |

Qn |

0 |

1 |

0 |

Qn |

0 |

1 |

1 |

Qn |

1 |

0 |

0 |

Qn |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

Соответствующее таблице логическое выражение имеет вид

![]()

Поскольку

при подаче на J-

и K-входы

триггер инвертирует свое состояние,

т.е. выполняет функцию Т-триггера, то

логично предположить, что структура

синхронного JK-триггера должна повторять

структуру T-триггера. В качестве базовых

следует выбрать RS-триггеры. Причем,

первый RS-триггер должен быть асинхронным

и иметь внешнюю в структурном плане

схему стробирования выходных сигналов

с сигналом синхронизации C

и соответствующими сигналами J

и K

(рис. 5.11,а).

С выходов элементов И-НЕ сигналы имеют

инвертированные значения, поэтому в

качестве асинхронного RS-триггера следует

выбирать триггер, реализованный на базе

элементов И-НЕ и имеющий инверсные входы

![]() и

и

![]() .

Условное графическое изображение

синхронного двухступенчатого JK-триггера

приведено на рис. 5.11,б.

.

Условное графическое изображение

синхронного двухступенчатого JK-триггера

приведено на рис. 5.11,б.

а) б)

Рис. 5.11. Структура синхронного JK-триггера и его условное графическое обозначение.

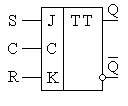

Триггер JK-типа относится к разряду универсальных, поскольку на его основе можно получить схемы, выполняющие функции RS-, D- и T-триггеров. Для выполнения функции RS-триггера, JK-триггер можно использовать, не вводя никаких дополнительных связей и узлов. Достаточно сигнал S подать на вход J, а сигнал R – на вход K (рис. 5.12,а). При этом одновременная подача на эти входы логических единиц не нарушит правило работы RS-триггера, поскольку у RS- триггера такая комбинация входных сигналов является вовсе неопределенной.

Если

в логическом уравнении для синхронного

JK-триггера принять

![]() и

и

![]() ,

тогда

,

тогда

![]() ,

,

что совпадает с логическим уравнением D-триггера. Таким образом, для получения D-триггера из JK-триггера необходимо сигнал подавать на вход J, который будет выполнять функцию D-входа, а на вход K сигнал D подавать через инвертор (рис. 5.12,б).

Для получения T-триггера достаточно объединить входы J и K. Тогда справедливы следующие преобразования

![]() .

.

Это уравнение приобретает вид логического уравнения T-триггера, причем объединенные входы J и K играют роль T-входа (рис. 5.12,в). В качестве входа Т можно использовать и вход разрешения записи С тактируемого JK-триггера. В этом случае на объединенные входы J и K необходимо постоянно подавать логическую единицу, что задает режим инвертирования состояния JK-триггера. При этом само инвертирование будет происходить лишь при поступлении на вход C разрешающего сигнала (рис. 5.12,г).

а) б)

в) г)

Рис. 5.12. Реализация триггеров различных типов на базе JK-триггера.

Временная диаграмма JK-триггера

Вопрос №14.

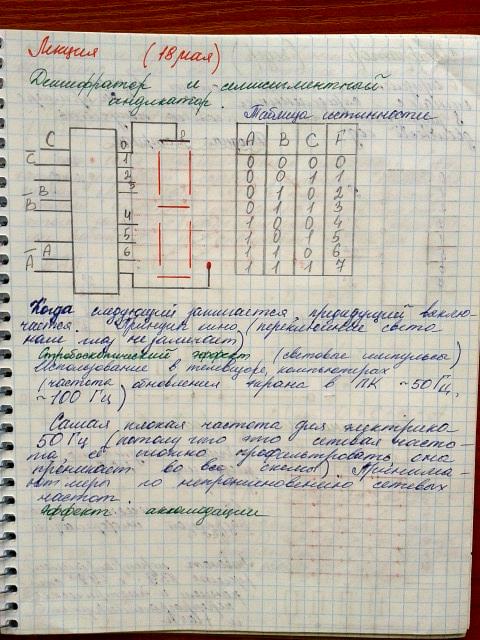

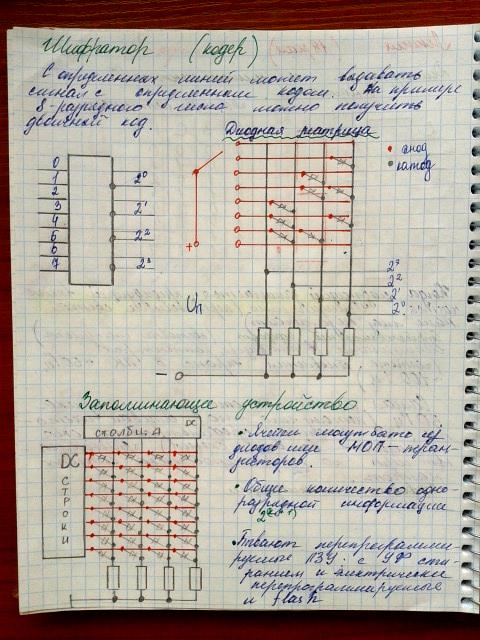

Комбинационные схемы. Дешифраторы. Шифраторы. Логические функции. Таблицы истинности.

Цифровыми устройствами комбинационного типа или цифровыми автоматами без памяти называются цифровые устройства, логические значения на выходе которых однозначно определяются совокупностью или комбинацией сигналов на входах в данный момент времени. К ним относятся суммирующие схемы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, цифровые компараторы и другие устройства. Цифровые устройства комбинационного типа выпускаются в виде интегральных микросхем или входят в состав больших интегральных микросхем, таких как процессоры, запоминающие и другие устройства.

Дешифраторы (декодеры)

Ячейки могут быть из диодов или МОП транзисторов. Общее количество одноразрядной информации 2(к+1) Бывают перепрограммируемые ПЗУ с УФ стиранием и электрически перепрограммируемые и flash

Вопрос №15.

Комбинационные схемы. Мультиплексоры. Демультиплексоры. Логические функции. Таблицы истинности.

Цифровыми устройствами комбинационного типа или цифровыми автоматами без памяти называются цифровые устройства, логические значения на выходе которых однозначно определяются совокупностью или комбинацией сигналов на входах в данный момент времени. К ним относятся суммирующие схемы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, цифровые компараторы и другие устройства. Цифровые устройства комбинационного типа выпускаются в виде интегральных микросхем или входят в состав больших интегральных микросхем, таких как процессоры, запоминающие и другие устройства.