- •Список экзаменационных вопросов по курсу «Схемотехника эвм», 4-й семестр. 2012 г.

- •Задачи анализа и задачи синтеза в деятельности инженера-схемотехника: их особенности и различия.

- •Основные физические величины, используемые при описании электромагнитных устройств: что характеризуют эти величины.

- •Как свойство накопления энергии в магнитном поле влияет на характеристики цифровых устройств?

- •Источники электрической энергии: для чего они нужны в электронных информационных устройствах? Каково основное отличие вольт-амперной характеристики источника электрической энергии?

- •Системные законы (уравнения) в математической модели цепи. Что они характеризуют? Назовите основные системные законы, позволяющие описывать процессы в электрической цепи.

- •Что называют сигналом в электронных информационных устройствах? Каков общий принцип отображения данных (информации) в сигнале?

- •Чем определяется точность при переходе к цифровому способу отображения информации в сигнале.

- •Каково может быть влияние на логический сигнал резистора, подключенного между выходом логического элемента и одним из выводов источника питания? Чем определяется сила этого влияния?

- •Что такое – свойство функциональной полноты системы логических функций. Какие совокупности логических функций обладают свойством функциональной полноты.

- •Теорема де Моргана и дуальные изображения логического элемента с несколькими входами. Для чего могут быть полезны дуальные изображения лэ?

- •Как могут быть построены электронные логические устройства, реализующие логические функции двух и более аргументов?

- •В чем состоит основное преимущество комплементарной схемотехники логических элементов с точки зрения энергоэффективности и в отношении динамических свойств (скорости переключения)?

- •Каковы основные характеристики, используемые для оценки динамических свойств лэ?

- •Что такое «многоразрядный логический вентиль» и для какой цели он используется?

- •Как можно реализовать любую из логических функций двух аргументов, а) используя только двухвходовый элемент и-не; б) используя только двухвходовый элемент или-не?

- •Что называют логической глубиной комбинационной схемы. Оцените логическую глубину для заданной вам логической схемы.

- •Каков обычный порядок проектирования цифрового устройства? Какими могут быть критерии минимизации, выполняемые при проектировании?

- •Проектирование произвольной логики комбинационного типа производится по этапам.

- •Каким способом можно наращивать разрядность дешифратора? Опишите схемотехнические приемы, укажите, каким требованиям должны удовлетворять используемые при этом малоразрядные дешифраторы.

- •Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса.

- •Воздействие временной задержки в логическом элементе при инвертировании сигнала а

- •Для чего используется импульсное устройство, называемое «триггером Шмитта»? Каков принцип функционирования триггера Шмитта?

- •Простой rs-триггер на элементах или-не: схема, принцип функционирования, таблица изменения состояний. Дуальная конфигурация rs-триггера на элементах и-не.

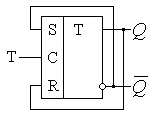

- •Условное графическое обозначение асинхронного rs-триггера

- •Триггеры типа crs (с управляемой записью): принцип функционирования, таблица изменения состояний, временные диаграммы, иллюстрирующие работу. Варианты crs-триггеров на элементах разного типа.

- •Триггер, управляемый перепадом синхросигнала: принцип функционирования, таблица изменения состояний, временные диаграммы, основное отличие от более простых триггерных цепей.

- •Двухступенчатый триггер: структурные особенности построения, принцип функционирования, таблица изменения состояний, временные диаграммы, основное отличие от более простых триггерных цепей.

- •Регистры для хранения данных: назначение, принципы построения, разновидности, особенности использования.

- •Сдвиговые регистры: их основные применения, принципы организации, особенности функционирования.

- •Счетный триггер: особенности построения, принцип функционирования, таблица изменения состояний, временные диаграммы, основное назначение счетного триггера.

- •Способы ускорения переноса в счетчике. Счетчик со сквозным переносом. Связь между задержкой переключения разряда и максимальной частотой счета.

- •Организация счетчика с модулем пересчета, отличным от 2n. Для чего может понадобиться изменять модуль пересчета в ходе работы устройства, как это можно сделать?

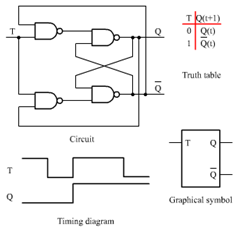

Счетный триггер: особенности построения, принцип функционирования, таблица изменения состояний, временные диаграммы, основное назначение счетного триггера.

Триггер Т является разновидностью триггера JK и отличается от него тем, что имеет один основной вход Т, сигнал с которого поступает на оба элемента И, за счёт чего триггер работает только в двух режимах: при Т = 0 он сохраняет предыдущее состояние выходов, а при Т = 1 изменяет его на противоположное. Правильное функционирование таких Т-триггеров возможно лишь при отсутствии у триггера свойства «прозрачности», т.е. это возможно на базе триггера с динамическим управлением, либо двухступенчатого.

|

Триггер T-типа является одновходовым устройством с двумя устойчивыми состояниями, изменяющимися каждый раз на противоположные при подаче на вход Т управляющего сигнала. Работа Т-триггера задается таблицей переходов:

tn |

tn+1 |

Tn |

Qn+1 |

0 |

Qn |

1 |

|

Характерной его особенностью является то, что частота изменения потенциала на его выходах в два раза меньше частоты сигналов на входе T . Это свойство используется при построении двоичных счетчиков. Отсюда второе название T-триггера – счетный триггер.

Структуру

T-триггера можно определить путем

преобразования его логической функции

к удобному для синтеза в заданном

базисе виду. Однако, из анализа работы

RS-триггера очевидно, что в том случае,

если он находился в единичном состоянии

Q=1, то для сброса его в нулевое состояние

необходимо сигнал с прямого выхода Q

подать на вход R сброса в нуль. Если же

RS-триггер изначально находился в

нулевом состоянии, т.е.

|

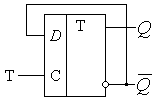

Т-триггер можно

построить и на базе D-триггера. Если в

логическом уравнении синхронного

D-триггера принять

|

Рассмотренные структуры Т-триггера являются практически нецелесообразными, поскольку характеризуются нестабильностью работы. Действительно, в течение всего времени, пока на входе T присутствует активный уровень сигнала, будет происходить непрерывная смена его состояний на противоположные с частотой, равной обратной величине времени задержки триггера. В результате возникает колебательный процесс. Причиной этого явления служит то, что Т-триггер, обладая обратными связями, принимает информацию как из внешней среды, так и со своих собственных выходов. Поэтому для устойчивой работы Т-триггера необходимо разделить во времени функции приема тактирующего сигнала Т и фиксации на входах R, S или D сигналов с соответствующих выходов Q и .

Т – триггер, или

счётный триггер, имеет один счётный

вход Т и два выхода (Рис ниже,а).

Функционирование триггера определяется

уравнением:

![]() Из уравнения следует, что Т – триггер

каждый раз изменяет своё состояние

на противоположное с приходом на

счётный вход Т очередного тактирующего

импульса длительностью tи. Этому

способствует наличие перекрёстных

обратных связей с выходов триггера

на входы элементов D1 и D2. Для надёжной

работы триггера, с целью сохранения

информации о предыдущем состоянии

триггера в момент его переключения,

в схему вводят элементы задержки,

имеющие время задержки

Из уравнения следует, что Т – триггер

каждый раз изменяет своё состояние

на противоположное с приходом на

счётный вход Т очередного тактирующего

импульса длительностью tи. Этому

способствует наличие перекрёстных

обратных связей с выходов триггера

на входы элементов D1 и D2. Для надёжной

работы триггера, с целью сохранения

информации о предыдущем состоянии

триггера в момент его переключения,

в схему вводят элементы задержки,

имеющие время задержки

![]() .

.

Рис. Т – триггеры: - а) структурная схема, б) УГО TV - триггера, в) Т – триггер на основе D – триггера.

Пусть в исходном

состоянии Q=1. Сигнал Т=1 откроет

элемент D2, так как на втором входе

D2 имеется сигнал лог «1» с выхода Q,

а элемент D1 будет закрыт. Триггер

переходит в состояние Q=0. Вентиль D2

остаётся открытым в течение времени

tи, т. к. сигнал Q=1 будет задержан ЛЗ1

на время

![]() .

В то же время сигнал

.

В то же время сигнал

![]() не попадёт на вентиль D1 из – временной

задержки в ЛЗ2. При отсутствии

элементов задержки возможно неоднократное

переключение триггера при условии,

если длительность импульса tи

значительно превышает время переключения

триггера. По окончании действия

тактирующего импульса, элементы D1 и

D2 закроются, так как потенциал входа

Т=0. После чего на вход элемента D1

через ЛЗ2 поступит сигнал

. В результате с приходом второго

импульса Т=1 откроется элемент D1 и

триггер переключится в состояние Q=1

и т. д. Роль ЛЗ в Т – триггерах

выполняют логические элементы с

большим временем задержки tзд.р. Кроме

счётного входа Т – триггер может

иметь вход разрешения V (Рисунок ,б).

Сигнал на этом входе разрешает (при

V=1) или запрещает (при V=0) срабатывание

триггера от поступающих на вход Т

сигналов. Т – триггеры, имеющие

дополнительный вход V, называются TV

– триггерами. Наличие входа V позволяет

организовать счёт в заданном временном

интервале, что существенно расширяет

функциональные возможности Т –

триггера.

не попадёт на вентиль D1 из – временной

задержки в ЛЗ2. При отсутствии

элементов задержки возможно неоднократное

переключение триггера при условии,

если длительность импульса tи

значительно превышает время переключения

триггера. По окончании действия

тактирующего импульса, элементы D1 и

D2 закроются, так как потенциал входа

Т=0. После чего на вход элемента D1

через ЛЗ2 поступит сигнал

. В результате с приходом второго

импульса Т=1 откроется элемент D1 и

триггер переключится в состояние Q=1

и т. д. Роль ЛЗ в Т – триггерах

выполняют логические элементы с

большим временем задержки tзд.р. Кроме

счётного входа Т – триггер может

иметь вход разрешения V (Рисунок ,б).

Сигнал на этом входе разрешает (при

V=1) или запрещает (при V=0) срабатывание

триггера от поступающих на вход Т

сигналов. Т – триггеры, имеющие

дополнительный вход V, называются TV

– триггерами. Наличие входа V позволяет

организовать счёт в заданном временном

интервале, что существенно расширяет

функциональные возможности Т –

триггера.

Счётный Т – триггер

может быть построен на основе D –

триггера, соединив инверсный выход

D – триггера со входом D, как показано

на рисунке ,в.

В такой схеме каждый переход 1/0 на

входе С будет приводить к переходу

триггера в противоположное состояние.

Например, если Qn=1, то

![]() , и поэтому очередной тактовый импульс

переведёт триггер в новое состояние,

т. е. установит

, и поэтому очередной тактовый импульс

переведёт триггер в новое состояние,

т. е. установит

![]() Для правильной работы Т – триггера

тактовый импульс должен быть коротким,

а наличие элемента задержки ЛЗ

ослабляет требование к длительности

тактового импульса. Таким образом,

из рассмотрения принципа работы Т –

триггера следует, что при Т=1 спадающий

фронт сигнала на входе С переводит

триггер в противоположное состояние.

Частота изменения потенциала на

выходе Т – триггера в два раза меньше

частоты импульсов на входе С. Это

свойство Т – триггеров позволяет

строить на их основе двоичные счётчики.

Поэтому эти триггеры и называют

счётными.

Для правильной работы Т – триггера

тактовый импульс должен быть коротким,

а наличие элемента задержки ЛЗ

ослабляет требование к длительности

тактового импульса. Таким образом,

из рассмотрения принципа работы Т –

триггера следует, что при Т=1 спадающий

фронт сигнала на входе С переводит

триггер в противоположное состояние.

Частота изменения потенциала на

выходе Т – триггера в два раза меньше

частоты импульсов на входе С. Это

свойство Т – триггеров позволяет

строить на их основе двоичные счётчики.

Поэтому эти триггеры и называют

счётными.

Способы построения счетчика с последовательным переносом и его основные особенности. Задержка распространения в счетчике с последовательным переносом, ее зависимость от времени переключения разряда, ее влияние на максимальную частоту счета. Аномальные состояния в счетчике с последовательным переносом и способы устранения их влияния.

Счетчики

строятся из разрядных схем, имеющих

межразрядные связи. Организации этих

связей различают счетчики с последовательным,

параллельным и комбинированными

переносами. Счетный

триггер делит частоту входных импульсом

на два. Счетчик с

последовательным переносом может

быть построен в виде цепочки последовательно

включенных счетных триггеров (рис., а).

В числе, содержащемся в счетчике, младшие

разряды расположены левее старших.

Представление счетчика цепочкой

Т-триггеров справедливо как для

суммирующего, так и для вычитающего

вариантов, поскольку закономерность

по соотношению частот переключения

разрядов сохраняется как при просмотре

таблицы сверху вниз (прямой счет), так

и снизу вверх (обратный счет). Различия

при этом состоят в направлении переключения

предыдущего разряда, вызывающего

переключение следующего. При прямом

счете следующий разряд переключается

при переходе предыдущего в направлении

от 1

к О, а при обратном — при переключении

от 0 к 1.

Следовательно, различие между вариантами

заключается в разном подключении входов

триггеров к выходам предыдущих. Если

схема строится на счетных триггерах с

прямым динамическим управлением, то

характер подключения следующих триггеров

к предыдущим для получения счетчиков

прямого и обратного счета будет

соответствовать рис. 3.47, б.

Полученные

структуры относятся к асинхронным

счетчикам,

т. к. в них каждый триггер переключается

выходным сигналом предыдущего, и эти

переключения происходят не одновременно.

Переключение

одного триггера за другим есть не что

иное, как распространение переноса по

разрядам числа при изменении содержимого

счетчика.

В худшем случае перенос распространяется

по всей разрядной сетке от младшего

разряда к старшему, т. е. для установления

нового состояния должны переключиться

последовательно все триггеры. Отсюда

видно, что время установления кода в

асинхронном счетчике составит величину

![]() .

Другим названием асинхронного счетчика

является название "последовательный

счетчик".

.

Другим названием асинхронного счетчика

является название "последовательный

счетчик".

Максимальная частота входных импульсов в режиме деления частоты ограничивается возможностями триггера младшего разряда, т. к. все последующие разряды переключаются с более низкими частотами.

Особенностью последовательных (асинхронных) счетчиков является возникновение в переходных процессах ложных состояний из-за задержек переключения триггеров. На рис. ниже показана временная диаграмма работы двухразрядного суммирующего счетчика на триггерах с прямым динамическим управлением, построенная с учетом задержек переключения триггеров tTг. Читая состояние счетчика Q по потенциалам на выходах триггеров Q0 и Q1, видим, что после состояний 1 и 3 появляются ложные состояния 0 и 2 (показаны штриховкой). Опасность воздействия коротких ложных импульсов на ЦУ заставляет прибегать при необходимости к стробированию выхода счетчика. В рассмотренных счетчиках срабатывание триггеров происходит поочередно друг за другом, т.е. последовательно. Такие счетчики называются асинхронными. Их недостаток состоит в том, что увеличивается общее время установления tуст с увеличением числа триггеров. Кроме того, появление промежуточных комбинаций может привести к ложному срабатыванию дешифратора, если такой есть в структуре ПЦУ. Для устранения этого недостатка используются счетчики, у которых все триггеры срабатывают одновременно. Такие счетчики получили название синхронных счетчиков.

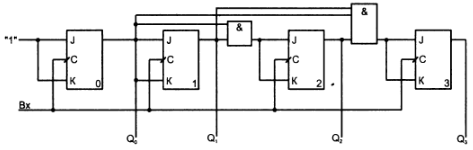

Асинхронный двоичный счетчик представляет собой совокупность последовательно соединенных триггеров (D - или JK ), каждый из которых ассоциируется с битом в двоичном представлении числа. Если в счетчике m триггеров, то число возможных состояний счетчика равно 2m, и, следовательно, модуль счета М также равен 2m. Счетная последовательность в двоичном суммирующем счетчике начинается с нуля и доходит до максимального числа 2m - 1, после чего снова проходит через нуль и повторяется. В вычитающем двоичном счетчике последовательные двоичные числа перебираются в обратном порядке, и при повторении последовательности максимальное число следует за нулем. Рассмотрим устройство двоичного суммирующего счетчика по модулю М=16, выполненного на базе JK-триггеров (рис. а). Как видно из рис. (а), синхронизирующие входы всех триггеров, кроме крайнего левого (Т1), соединены с выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния предыдущего триггера. Из таблицы состояния счетчика (рис., б) легко заметить, что значение разряда в выбранной позиции меняется тогда, когда в соседней справа позиции состояние переходит из “1” в “0”, управление триггерами осуществляется задним фронтом синхроимпульсов (отрицательным перепадом напряжения импульса синхронизации).

Асинхронный двоичный счетчик с последовательным переносом.

Импульсы, подлежащие счету, подаются на вход С0 первого триггера, который формирует младший разряд счетчика. Перед производством подсчета подаваемых импульсов, счетчик обнуляется. Для этого все установочные входы R объединены и при подаче сигнала RS = 0 устанавливаются Q0 = Q1 = Q2 = Q3 = 0. Входы J,K находятся в единичном состоянии. Триггеры работают в счетном режиме. На входах получаем информацию в двоичном коде. При подаче некоторых импульсов идет последовательное переключение разряда триггеров. Длительность переходного процесса будет зависеть от разрядности счетчика. Из временной диаграммы видно, что счетчик работает в параллельном двоичном коде как суммирующий. Срабатывание всех триггеров должно находиться в районе пауз между сигналами. С учетом собственного времени срабатывания триггеров этот процесс при большой частоте подаваемых сигналов может не уложиться в период паузы синхроимпульсов и приведет к неправильному срабатыванию счетчика. Общим недостатком всех асинхронных счетчиков является большое время переключения счетчика. Если принять время переключения одного счетчика за Dt, то время переключения n- разрядного счетчика составит n×Dt. Этим объясняется, что асинхронные счетчики не выпускаются разрядностью более четырех. В синхронных счетчиках входной сигнал Хсч подается одновременно на все входы синхронизации, время переходного процесса не зависит от разрядности счетчика и равно tпер=Dt взамен переключения одного триггера.

В качестве примера рассмотрим 3-х разрядный счетчик, выполненный на двухтактных Т-триггерах с дополнительным R-входом для установки исходного нулевого состояния (рисунок ниже).

В рассмотренном счетчике каждый последующий триггер переключается сигналом переноса, формируемым на выходе предыдущего разряда, поэтому схема называется счетчиком с последовательным переносом. Переключение отдельных триггеров происходит последовательно друг за другом (не одновременно, асинхронно), поэтому такой счетчик называется асинхронным. Подачей единичного сигнала на вход УИС все триггеры устанавливаются в исходное нулевое состояние. Срезом каждого входного импульса переключается триггер младшего разряда Тг1. Срезом сигналов UQ1 переключается триггер второго разряда Тг2. Срез импульсов на выходе Q2 вызывает переключение триггера третьего разряда Тг3.

Частота импульсов на выходе каждого триггера вдвое меньше частоты импульсов на его входе. N-разрядный счетчик делит частоту входных импульсов в 2n раз. С наибольшей частотой, равной частоте входных импульсов, переключается входной триггер счетчика.

В момент, предшествующий переключению очередного триггера, все предыдущие разряды счетчика находятся в единичном состоянии;

восьмой импульс для трехразрядного счетчика (рисунок 9.51) является импульсом переполнения, которым все триггеры устанавливаются в нуль (счетчик “обнуляется”). Девятым импульсом счетчик вновь начинает заполняться;

максимальное число импульсов, которое может зафиксировать схема, равно (2n - 1). В нашем примере n = 3 и в счетчик можно записать 7 импульсов.

если использовать сигнал переноса, формируемый на выходе, то счетчик может посчитать 2n импульсов. Если n=3, то Ксч=23=8.

Достоинство счетчика с последовательным переносом – простота внутренней структуры.

Недостаток счетчика с последовательным переносом – большое время установления выходного кода tk

tk≠const, зависит от конкретного значения его выходного кода.

tк max будет в случае изменения выходного кода со значения 111….в 000….. или наоборот

tк max=N х tkтр., где

N – число разрядов в счетчике

tkтр – время переключения одного разряда счетчика

Понизить tmax можно при условии, что все триггеры его разрядных схем будут переключаться одновременно. Для этого:

1.используют синхронные триггеры

2.организуют сигналы, определяют порядок переключения триггеров до прихода сигнала С

Способы ускорения переноса в счетчике. Счетчик с параллельным переносом. Связь между задержкой переключения разряда и максимальной частотой счета.

Максимальным быстродействием обладают синхронные счетчики с параллельным переносом, структуру которых найдем эвристически, рассмотрев процессы прибавления единицы к двоичным числам и вычитания ее из них, например:

Результат всегда отличается от исходного числа только в нескольких младших разрядах, значения которых инвертируются. Для суммирующего счетчика требуется инверсия разрядов до первого разряда, равного логическому нулю, включая и его, а для вычитающего аналогично до разряда, равного логической единице. Таким образом, в суммирующем счетчике должны переключиться разряды, для которых все младшие единичны, для вычитающего — те, для которых все младшие находятся в нуле. Время установления нового состояния для таких счетчиков (если не учитывать зависимости задержек элементов от нагрузок на них) не зависит от их разрядности и равно времени переключения триггера tтг. Длительность цикла равна tтг + tk , где tk — задержка коньюнктора. Структура суммирующего синхронного счетчика с параллельным переносом, реализованного на триггерах с управлением фронтом, показана на рис. ниже.

Для ускорения переноса в счетчике используются счетчики, у которых все триггеры срабатывают одновременно

( синхронные). Идея синхронного счетчика заключается в построении внешней комбинационной схемы, формирующей сигналы, согласно которым будет происходить одновременное переключение только части триггеров в зависимости от текущего выходного кода. Причем эти сигналы должны быть сформированы до поступления очередного счетного импульса. Счетный импульс должен поступать на все триггеры одновременно. Для этих целей необходимо использовать тактируемые Т-триггеры, входы синхронизации которых объединяются в общую шину. На тактовые Т-входы каждого триггера подаются заранее сформированные сигналы переноса с комбинационной схемы.

рис. 5.18 Структурная схема четырехразрядного суммирующего счетчика с параллельным переносом.

Анализ смены состояний суммирующего счетчика показывает, что если значение младшего разряда меняется каждый раз с приходом входного сигнала, то в остальных разрядах значение будет меняться на противоположное только в тех случаях, когда до этого во всех предыдущих разрядах были единицы. Для этого единичный входной сигнал должен поступать на вход триггера только в том случае, если триггеры во всех предыдущих разрядах находятся в единичном состоянии. Задачу формирования входного сигнала для каждого последующего триггера выполняет логический элемент И ЛЭ1 (ЛЭ2), на входы которого подаются сигналы со всех выходов предыдущих триггеров (рис. 5.18). Срабатывание всех триггеров происходит одновременно по общему сигналу синхронизации С, который является счетным импульсом для всего счетчика. Изображенная на рисунке структура называется счетчиком с параллельным переносом, поскольку сигналы на все элементы И, формирующие единичные переносы, подаются с выходов триггеров одновременно в параллельном виде. В исходном состоянии на выходах всех триггеров присутствуют логические нули. С поступлением каждого счетного импульса выходные коды начинают увеличиваться на единицу (инкрементироваться). Задержка в такой схеме равна времени срабатывания одного триггера. Недостатком счетчиков с параллельным переносом является необходимость использования в случае увеличения разрядности счетчика элементов И с большим числом входов. При этом выходы триггеров должны обладать высокой нагрузочной способностью. Поэтому многоразрядные счетчики строят по групповому принципу. Согласно этому принципу, весь счетчик структурно реализуется путем соединения отдельных групп небольшой разрядности с параллельным переносом внутри этих групп. Сигнал переноса из очередной группы формируется элементом И, объединяющим выходы всех триггеров данной группы. Сформированный сигнал переноса предыдущей группы подается на счетный вход последующей группы. Общая задержка такого счетчика определяется суммой задержек каждой группы.

В схеме с помощью конъюнкторов организован так называемый параллельный перенос. Его идея состоит в том, что сигнал переноса поступает на J, K входы последующих триггеров лишь в том случае, если предыдущие находятся в состоянии единица. Триггер Тг1 переключается каждым счетным импульсом, т.к. на его J и K входы постоянно подается единица. Остальные триггеры переключаются счетными импульсами при следующих условиях: Тг2 - при Q1=1; Тг3 - при Q1=1; Q2=1; Тг4 - при Q1=1; Q2=1; Q3=1.

Недостатком описанного счетчика является необходимость иметь конъюнкторы с большим количеством входов, число которых возрастает с увеличением числа разрядов. Если число разрядов синхронного счетчика не превышает четыре, то схему можно реализовать без внешних конъюнкторов, используя JK-триггеры с входной логикой И.

Синхронный двоичный счетчик с параллельным переносом.

Старший триггер срабатывает при наличии «1» на всех младших разрядах. На всех свободных входах подается «1». Срабатывание всех триггеров происходит параллельно. Длительность переходного процесса в таком случае для данного счетчика равна длительности переходного процесса одного разряда. Так как JK триггер имеет до 3-х входов, то число разрядов делают не более 4-х. Если требуется большее число разрядов, то делают группы с параллельным переносом по 4- разряда, а между группами методом сквозного переноса. Этот способ переноса называется групповым. Способ обладает большим быстродействием. JK триггеры работают в режиме инвертирования. Последующие триггера срабатывают, если на всех входах J и K будет «1», т. е. будет «1» на всех выходах предыдущих триггеров.

Достоинство высокое быстродействие. В синхронных счетчиках входной сигнал Хсч подается одновременно на все входы синхронизации, время переходного процесса не зависит от разрядности счетчика и равно tпер=Dt взамен переключения одного триггера. Недостаток – ограниченное число разрядов.