- •Список экзаменационных вопросов по курсу «Схемотехника эвм», 4-й семестр. 2012 г.

- •Задачи анализа и задачи синтеза в деятельности инженера-схемотехника: их особенности и различия.

- •Основные физические величины, используемые при описании электромагнитных устройств: что характеризуют эти величины.

- •Как свойство накопления энергии в магнитном поле влияет на характеристики цифровых устройств?

- •Источники электрической энергии: для чего они нужны в электронных информационных устройствах? Каково основное отличие вольт-амперной характеристики источника электрической энергии?

- •Системные законы (уравнения) в математической модели цепи. Что они характеризуют? Назовите основные системные законы, позволяющие описывать процессы в электрической цепи.

- •Что называют сигналом в электронных информационных устройствах? Каков общий принцип отображения данных (информации) в сигнале?

- •Чем определяется точность при переходе к цифровому способу отображения информации в сигнале.

- •Каково может быть влияние на логический сигнал резистора, подключенного между выходом логического элемента и одним из выводов источника питания? Чем определяется сила этого влияния?

- •Что такое – свойство функциональной полноты системы логических функций. Какие совокупности логических функций обладают свойством функциональной полноты.

- •Теорема де Моргана и дуальные изображения логического элемента с несколькими входами. Для чего могут быть полезны дуальные изображения лэ?

- •Как могут быть построены электронные логические устройства, реализующие логические функции двух и более аргументов?

- •В чем состоит основное преимущество комплементарной схемотехники логических элементов с точки зрения энергоэффективности и в отношении динамических свойств (скорости переключения)?

- •Каковы основные характеристики, используемые для оценки динамических свойств лэ?

- •Что такое «многоразрядный логический вентиль» и для какой цели он используется?

- •Как можно реализовать любую из логических функций двух аргументов, а) используя только двухвходовый элемент и-не; б) используя только двухвходовый элемент или-не?

- •Что называют логической глубиной комбинационной схемы. Оцените логическую глубину для заданной вам логической схемы.

- •Каков обычный порядок проектирования цифрового устройства? Какими могут быть критерии минимизации, выполняемые при проектировании?

- •Проектирование произвольной логики комбинационного типа производится по этапам.

- •Каким способом можно наращивать разрядность дешифратора? Опишите схемотехнические приемы, укажите, каким требованиям должны удовлетворять используемые при этом малоразрядные дешифраторы.

- •Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса.

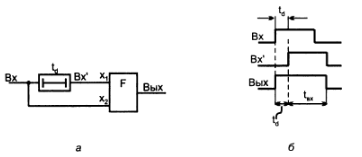

- •Воздействие временной задержки в логическом элементе при инвертировании сигнала а

- •Для чего используется импульсное устройство, называемое «триггером Шмитта»? Каков принцип функционирования триггера Шмитта?

- •Простой rs-триггер на элементах или-не: схема, принцип функционирования, таблица изменения состояний. Дуальная конфигурация rs-триггера на элементах и-не.

- •Условное графическое обозначение асинхронного rs-триггера

- •Триггеры типа crs (с управляемой записью): принцип функционирования, таблица изменения состояний, временные диаграммы, иллюстрирующие работу. Варианты crs-триггеров на элементах разного типа.

- •Триггер, управляемый перепадом синхросигнала: принцип функционирования, таблица изменения состояний, временные диаграммы, основное отличие от более простых триггерных цепей.

- •Двухступенчатый триггер: структурные особенности построения, принцип функционирования, таблица изменения состояний, временные диаграммы, основное отличие от более простых триггерных цепей.

- •Регистры для хранения данных: назначение, принципы построения, разновидности, особенности использования.

- •Сдвиговые регистры: их основные применения, принципы организации, особенности функционирования.

- •Счетный триггер: особенности построения, принцип функционирования, таблица изменения состояний, временные диаграммы, основное назначение счетного триггера.

- •Способы ускорения переноса в счетчике. Счетчик со сквозным переносом. Связь между задержкой переключения разряда и максимальной частотой счета.

- •Организация счетчика с модулем пересчета, отличным от 2n. Для чего может понадобиться изменять модуль пересчета в ходе работы устройства, как это можно сделать?

Воздействие временной задержки в логическом элементе при инвертировании сигнала а

На входы элемента И подаются одновременно сигнал А и его отрицание. По правилам алгебры логики сигнал на его выходе должен быть равен 0. Однако, как можно видеть на временных диаграммах, в течение интервалов времени, отмеченных штриховкой, А и отрицание А одновременно равны 1 Выходная функция этого элемента состоит из серии положительных выбросов, возникающих при изменении А от 0 до 1 и имеющих длительность в tg с. Это явление объясняется временной задержкой логического инвертора. Схему, в которой возможна генерация такого сигнала, называют схемой со статическим нулевым риском (0-риском), поскольку выходной сигнал, который должен быть все время равен логическому «0», в короткие временные интервалы устанавливается в «1».

В

другом случае, если сигналы поступают

на входы двухвходового элемента ИЛИ,

то на выходе элемента появится функция

![]() ,

которая в соответствии с алгеброй логики

должна быть равна логической «1».

Расположение импульсов

,

которая в соответствии с алгеброй логики

должна быть равна логической «1».

Расположение импульсов

![]() показывает, что в течение временных

периодов, соответствующих заштрихованным

частям рисунка, оба они одновременно

равны «0». В течение этих заштрихованных

интервалов, имеющих небольшую

продолжительность, выходной сигнал

равен логическому «0». В таком случае

говорят, что схема имеет статический

показывает, что в течение временных

периодов, соответствующих заштрихованным

частям рисунка, оба они одновременно

равны «0». В течение этих заштрихованных

интервалов, имеющих небольшую

продолжительность, выходной сигнал

равен логическому «0». В таком случае

говорят, что схема имеет статический

единичный риск (1-риск), так как сигнал на ее выходе, равный в нормальном состоянии «1», на короткие периоды времени переходит в логический «О». Следует отметить, что для элемента ИЛИ отрицательные выбросы появляются в моменты, когда А изменяется от 1 до 0.

Каковы причины возникновения «рисков»? В чем состоят вредные, нежелательные последствия возникновения «рисков»? Какие два различных способа используются для предотвращения вредных последствий «рисков»?

Из-за наличия задержек распространения сигнал на выходе более или менее сложной логической цепи может измениться (и даже несколько раз), что приведет к появлению рисков. Со временем они исчезают, и выход комбинационных цепей (КЦ) приобретает значение, предусмотренное логической формулой, описывающей работу цепи. Однако риски могут быть восприняты элементами памяти автоматов памяти (АП), необратимое изменение состояния которых может радикально изменить работу ЦУ, несмотря на исчезновение сигналов рисков на выходе КЦ. При изменении входных сигналов комбинационной схемы на ее выходе могут возникнуть выбросы. Они появляются из-за того, что на различных путях прохождения сигналов через схему от входа к ее выходу могут возникать различные временные задержки.

Если при проектировании выясняется, что проектируемая цепь, возможно, подвержена «рискам», имеются два различных пути.

Можно спроектировать цепь, которая выполняет ту же логическую функцию, но свободна от рисков; это достигается усложнением схемы, иногда значительным.

Можно запрещать восприятие сигналов устройствами, для которых формируемые цепью сигналы, являются входными, на время, за которое гарантированно закончатся переходные процессы. Это время можно оценить произведением логической глубины на максимальную задержку распространения элемента.

Первый состоит в синтезе схем, свободных от рисков, и требует сложного анализа процессов в схеме и введения избыточных элементов для исключения рисков. Этот путь редко используется на практике. Второй путь, основной для современной схемотехники, предусматривает запрещение восприятия сигналов КЦ элементами памяти на время переходных процессов. Прием информации с выходов КЦ разрешается только специальным сигналом синхронизации, подаваемым на элементы памяти после окончания переходных процессов в КЦ. Таким образом, исключается воздействие ложных сигналов на элементы памяти. Иными словами, основная идея здесь может быть выражена словами "переждать неприятности". Соответствующие структуры называются синхронными.

Каким способом можно организовать в цифровой цепи задержку момента переключения сигнала на заданное время? Для чего в цифровой цепи может понадобиться задержка переключения сигнала (приведите какой-нибудь пример)?

Задержка переключения естественным образом имеется у реального элемента. В реальных цепях бывает необходимо реализовать задержку переключения на заданное время. Это может относиться как к отдельному переключению, так и к последовательности переключений в целом. Это две разные задачи. Если требуемая задержка невелика, ее можно получить с помощью цепи последовательно включенных ЛЭ (не более 3…5).

Что делать, если требуется значительная задержка? Для этого используют дополнительные цепи, содержащие реактивные элементы (накопители энергии: конденсаторы или индукторы – катушки индуктивности). Элементы задержки относятся к числу вспомогательных элементов. Задержки цифровых сигналов требуются прежде всего для временного согласования распространения сигналов по различным путям в ЦУ с целью борьбы с критическими временными состязаниями, нарушающими работоспособность автоматов с памятью. Вариант технической реализации элементов задержки зависит от требуемых значений параметров задержки сигналов, а именно: величины, стабильности, регулируемости и т. д. На практике применяют следующие различные варианты реализации задержек:

отрезки обычных или специальных коаксиальных кабелей;

цепочки логических элементов;

искусственные электромагнитные линии задержки;

RC-цепочки;

одновибраторы;

схемы деления частоты тактовых сигналов.

|

|

В чем состоит основной недостаток организации задержки использованием цепочки последовательно включенных стандартных логических элементов? Как используют цепи, содержащие конденсатор, для организации задержки переключения логического элемента?

Остановимся на самых типичных вариантах — цепочках логических элементов и RC-цепочках. В первом случае используется естественная инерционность логических элементов. При составлении из нескольких логических элементов последовательной цепочки можно суммировать задержки отдельных элементов. Для целей задержки естественно применять простейшие элементы-инверторы или повторители. Это удобный способ — в простейшем корпусе малой интегральной схемы (МИС) уже размещены 6 инверторов или повторителей. Задержку можно регулировать дискретно, изменяя число элементов в цепочке. Если цепочка составлена из инверторов, то при четном их числе получается просто задержка сигнала, при нечетном — задержка с инверсией. Величины получаемых задержек обычно подходят к требуемым, т. к. требуется компенсация разновременности распространения сигналов в цепях, также составленных из логических элементов. Точность задержки в этом случае ограничивается разбросом собственных задержек элементов и поэтому невысока и время задержки не велико (ограничено количеством ЛЭ). Задержку на большее время можно получить с помощью RC-цепочки, включаемой в цепь передачи сигнала, где она формирует экспоненциальные процессы перезаряда емкости через резистор R с постоянной времени RC. Если считать пороговым напряжением середину логического перепада, то время задержки td = RC • 1n2 = 0,7RC (индекс d происходит от англ. delay, что означает задержку). После RC- цепочки в схеме включены три инвертора для формирования достаточно крутых фронтов на выходе элемента задержки. Есть возможность регулирования и значительного увеличения времени задержки.

Имеется существенная разница в условиях применения RC-цепочек в схемах на МОП-транзисторах и в схемах на биполярных приборах. В первом случае входные токи элементов пренебрежимо малы и включение на входе логического элемента даже большого сопротивления вполне допустимо. Во втором случае входные токи элементов значительны, поэтому в их входные цепи можно включать лишь малые сопротивления (иначе произойдут недопустимые изменения уровней напряжения U0 и U1 из-за падений напряжения на резисторе R). Нередко допустимые значения сопротивления резистора R составляют в этом случае величину порядка сотен Ом. При малых значениях сопротивления R постоянную времени придется увеличивать за счет больших емкостей С, что не всегда удобно по конструктивным соображениям. С увеличением постоянной времени RC напряжение на емкости при переключениях становится все более пологим. При этом свойственный логическим элементам разброс пороговых напряжений будет вызывать все больший разброс задержек. Таким образом, чем больше задержка, тем менее точной она становится. Кроме того, для некоторых элементов (типа КМОП) слишком длительные фронты входных сигналов недопустимы по паспортным данным. Нежелательны затянутые фронты и для элементов ТТЛ(Ш) с их сквозными токами. Перед повторным срабатыванием схема должна восстановиться, для чего длительность постоянного уровня входного напряжения должна быть около 3RC. В схемах ЦУ задержки на RC-цепочках могут составлять величины до единиц миллисекунд. Цепочки RC используются не только непосредственно, но и в форме время-задающих цепей одновибраторов, которые также являются элементами, пригодными для использования в качестве задержек цифровых сигналов (фронтов).

Как можно расширить длительность логического импульса? Какие схемотехнические решения позволяют это осуществить?

К задачам формирования импульсов по длительности относятся расширение, сужение и стандартизация их длительности. Если конкретизировать функцию F, считая ее дизъюнкцией, то, как видно из временных диаграмм на рис. 1.27 б, схема будет расширять входной импульс на интервал, равный времени задержки td.

Как «ведет себя» в логической цепи устройство, называемое одновибратором? Каков принцип действия одновибратора? В чем состоит преимущество одновибраторов, в схеме которых имеется обратная связь?

Формирователи импульсов заданной длительности "(одновибраторы) обеспечивают получение выходных импульсов при соответствующем перепаде входного сигнала.

Некоторые варианты схем одновибраторов, построенных на цифровых ИС, показаны на рис: 5.10.

В одновибраторе по схеме рис. 5.10, а) на входы второго инвертора поданы взаимно инверсные сигналы со входа и выхода первого инвертора, поэтому в статическом режиме сигнал на выходе устройства всегда равен единице. Сигнал «нуль» на выходе второго инвертора появляется только в том случае, когда сигнал на входе первого инвертора переходит из нуля в единицу. При этом пока происходит переключение первого инвертора, на оба входа второго будет подан сигнал «единица». Длительность выходного импульса формирователя, можно увеличивать, увеличивая время переключения первого инвертора присоединением к его выходу RС-цепи.

Длительность выходного импульса одновибратора можно также увеличивать, включая несколько инверторов между входом устройства и выходным инвертором (рис. 5.10,6). Необходимо только помнить, что число этих инверторов должно быть нечетным.

Еще одна схема формирователя показана на рис. 5.10 в). В данном случае перепад нуль — единица на входе приводит к появлению на выходе отрицательного импульса, длительность которого равна утроенной средней задержке распространения сигнала, характерной для примененных инверторов.

Более крутые фронты выходного импульса обеспечивает одновибратор на основе тактируемого фронтом триггера (рис. 5.10,г). Перепад 0/1 на тактовом входе триггера устанавливает его в состояние 0. По истечении времени, необходимого для разряда конденсатора, на выходе RС-цепи, подключенной к триггеру, также появляется сигнал 0. Этот сигнал, воздействуя на установочный вход триггера S, возвращает его в состояние 1.

К генераторам одиночных импульсов относится ждущий мультивибратор или одновибратор. Ждущий мультивибратор (одновибратор) – это устройство с одним устойчивым и одним неустойчивым состоянием, длительность которого определяется внутренними переходными процессами времязадающих реактивных цепей. После пребывания в неустойчивом состоянии ждущий мультивибратор снова возвращается в устойчивое состояние. Для перевода одновибратора в неустойчивое состояние на его вход подается запускающий импульс. Таким образом, при подаче на вход короткого запускающего импульса, одновибратор вырабатывает на выходе импульс фиксированной длительности. Схема ждущего мультивибратора на двух логических элементах и RC-цепи представлена на рис. 3.7.

Рис. 3.7. Схема ждущего мультивибратора.

В состав ждущего мультивибратора входят логические элементы ЛЭ1, ЛЭ2 и RC-цепь. При этом, ЛЭ2 и RC-цепь образуют схему задержки на основе дифференцирующей цепи, рассмотренную выше. Источником входного импульса для нее является выход элемента ЛЭ1. Схема задержки формирует задержку входного импульса на величину tзад. В устойчивом состоянии, поскольку на входе ЛЭ2 действует напряжение UR0, меньшее Uпор, на выходе схемы присутствует логическая единица, которая одновременно подается на один из входов ЛЭ1. Если при этом на другой вход ЛЭ1 (Uвх) также подавать логическую единицу, то на выходе ЛЭ1 сохраняется логический нуль. Схема, таким образом, находится в устойчивом состоянии (рис. 3.8). Подав теперь на вход Uвх напряжение логического нуля, на выходе ЛЭ1 сформируется напряжение логической единицы, которое через конденсатор передастся на ЛЭ2. На входе ЛЭ2 напряжение возрастет до значения URmax и на его выходе сформируется логический нуль. По мере заряда конденсатора, напряжение на входе ЛЭ2 будет стремиться к значению UR0. В момент равенства напряжения на входе ЛЭ2 значению Uпор, на выходе ЛЭ сформируется логическая единица и схема вернется в устойчивое состояние. Длительность выходного импульса будет определяться длительностью задержки tзад, задаваемой схемой задержки на элементе ЛЭ2, конденсаторе и резисторе.

Рис. 3.8. Временная диаграмма работы ждущего мультивибратора.