- •1.Параметры усилителей

- •4. Основные характеристики усилителей

- •5 .Способы задания режимов по пост. Току ус-ых каскадов на бт

- •6. Способы задания режимов по пост. Току ус-ых каскадов на пт

- •11. Влияние ос на коэфф. Усилителя и стабильность

- •12. Усилительный каскад в схеме с ок (эмиттерный габарит)

- •13. Усилители постоянного тока (упт)

- •14. Методы борьбы с дрейфом нуля

- •17,18.Мостовые схемы. Дифференциальные усилители.

- •18. Дифференциальные усилители

- •19. Метод модуляции, демодуляции

- •22. Операционные усилители

- •2 3. Инвертируемый усилитель

- •24. Неинвертирующий усилитель

- •27. Основные параметры ключей

- •28. Простейший ключ на бт.

- •31.Ключи на полевых транзисторах (пт)

- •32. Ключи на комплементарных тр-рах.

- •33. Параметры логических элементов

- •Преимущества и недостатки

- •Резисторно-емкостная транзисторная логика (ретл)

- •Достоинства и недостатки ртл и ретл

- •37. Элемент эсл

- •38.Логический элемент ттлш(35. Транзисторно-транзисторная логика с барьером Шотки)

- •39. Логический элемент n-моп логики

- •40. Логический элемент p-моп логики

- •41. Логический элемент k-моп логики

- •42. Основные элементы

- •43. Простейшие коды (двоичный, двоично-десятичный, код с приоритетом)

- •44. Триггерная ячейка

- •45. Триггер с разделённым входом

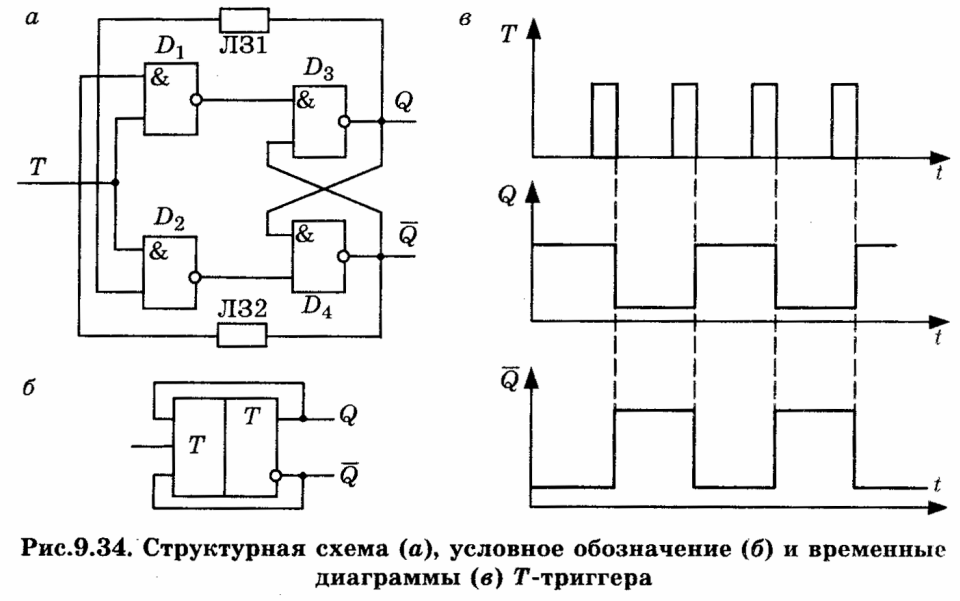

- •46. Триггер со счётным входом

- •48. Синхронизируемые rs-триггеры

- •49. Двухтактные триггеры

45. Триггер с разделённым входом

46. Триггер со счётным входом

47. RS-триггер

RS-триггер[9][10], или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. Триггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое. Триггер имеет два устойчивых состояния 0 и 1 и два выхода: прямой Q и

Инверсный Q Информационный вход, входной сигнал которого устанавливает триггер

в единичное состояние, называют S–входом. Перевод триггера в нулевое состояние называют сбросом или гашением (reset), а соответствующий сигнал и вход обозначают R.

Схема простейшего триггера получается на основе двух двухвходовых логических элементов ИЛИ–НЕ или И–НЕ. Устойчивое состоя-ние обеспечивается за счет связи выхода каждого элемента с одним из входов другого. Свободные входы логических элементов служат для управления и называются информационными или логическими (R – сброс, S – установка).

Асинхронные RS-триггеры

Строится на эл-ах ИЛИ-НЕ и И-НЕ

Для созд-я RS тр. исп-ся лог. эл-т с двумя вх-ми. За счёт ПОС с вых. одного лог эл-та на вх. др. происходит быстрое переключ. схемы при смене инф. входов.

Отличие ИЛИ-НЕ и И-НЕ состоит в том, что управл. тр. на эл-ах И-НЕ осущ-ся инверсн., т.е. низкими пот-ми.

Асинхр. тр. не нашли шир. примен., а явл-ся сост. частью для созд-я др. тр.

Синхронизируемые RS-триггеры

Строятся как на эл-ах И-НЕ, так и на эл-ах ИЛИ-НЕ. Однако исп-е эл-ов И-НЕ наиб. распростр. в инж. практике.

Кроме инф. входов S и R ещё им-ся синхрос-л. При этом тр-р перех. в др. сост-е только при налич. с-ла на С-входе.

Особ-ю постр-я синхр.RS-тр. явл-ся схема управления, собр-я на эл-ах D1,D2 и упр.

происх. прямыми инф. с-ми.На эл-ах D3,D4 собран обычный асинхр. тр-р.

Состояние тр-ра будет изм-ся только при наличии с-ла на синхровходе и на одном из инф. входах.

48. Синхронизируемые rs-триггеры

С троятся

как на эл-ах И-НЕ, так и на эл-ах ИЛИ-НЕ.

Однако исп-е эл-ов И-НЕ наиб. распростр.

в инж. практике. Кроме инф. входов S

и R ещё им-ся синхрос-л.

При этом тр-р перех. в др. сост-е только

при налич. с-ла на С-входе.

троятся

как на эл-ах И-НЕ, так и на эл-ах ИЛИ-НЕ.

Однако исп-е эл-ов И-НЕ наиб. распростр.

в инж. практике. Кроме инф. входов S

и R ещё им-ся синхрос-л.

При этом тр-р перех. в др. сост-е только

при налич. с-ла на С-входе.

Особ-ю постр-я синхр.RS-тр. явл-ся схема управления, собр-я на эл-ах D1,D2 и упр. происх. прямыми инф. с-ми.При налич сигн на R и S вх и отсутствия сигн на C-вх. Триг сохран предыдущ сост.Триг может перех. В др.сост,если на одном из инфовх. И синхровх имеется одновремен «1».Предполож,на S-вх и С-вх под-ся

«1».На вх D1 будет «1», D1открыт и на его выходе будет «0».В это же время на вх D2 действуют разные сигн(на R-вх под-ся «0», а на С-вх-«1»).D2 закр-ся и на его вх форм-ся «1».На D3 с вых D1 поступ «0»,D3 закр-ся и на его вых форм-ся «1».С вых D3 на вх D4 под-ся «1».D4 откр-ся и на его вых форм-ся «0».И триг устан-ся в еиничное сост.Это сост опр-ся на прямом вых.Если на R-вх под-ся «1»,на С-вх «1»,а на S-вх «0». То на на вх. D2 поступ «1»,D2 откр-ся и на вых форм-ся «0».На вх D1 поступ «1» и «0»,D1 закр-ся и на его вых форм-ся «1».На вх D4 поступ «0»,D4 закр-ся и на его вых форм-ся «1»,кот поступ и инверт вых на 2-ой вх D3.И D3 откр-ся и на его вых форм-ся «0».Т.о. на прямом вых получ «0»,а на инверт. «1» и триг восст в единичное сост.Если на оба инфовх и синхровх подать «1».То на D1 и D2 нах-ся в одинаковых сост.и под действ вх сигнал. D1 и D2 откр-ся и на их вых форм-ся одновремен «0», кот перед-ся на вх асинхрон R-S-триг на элем И-НЕ. Но эта комбинауия на асинхрон R-S-триг явл-ся запрещ. Поэтому подача «1» на R,S,C вх явл-ся запрещ.Структурная схема для синхрон R-S триг на элем И-НЕ аналогична.Отличие:триг на элем ИЛИ-НЕ упр-ся инверсн. вх сигналами.