- •Элементы устройств вычислительный систем. Вентили, триггеры, регистры, счетчики, мультиплексоры, шифраторы, дешифраторы, сумматоры.

- •Асинхронные счетчики.

- •Синхронные счётчики.

- •Мультиплексор

- •Демультиплексор

- •Сумматор

- •4. По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

Мультиплексор

Мультиплексором называется комбинационная схема, имеющая m+2m входов и один выход, где m – количество адресных входов, а 2m – количество информационных входов мультиплексора. Адреса представляются в двоичном коде и им присваивается номер j. Каждому адресу с номером j соответствует свой информационный вход Aj , сигнал с которого при данном адресе проходит на выход. Основным назначением мультиплексора является коммутация 2m входных сигналов на один выход. Таким образом, мультиплексор выполняет функцию

![]()

где X – двоичный код адреса; Aj – входные информационные сигналы мультиплексора; Kj(X) – конституенты 1, принимающие значения, равные 1 на единственном наборе переменных X = j. Условное описание мультиплексора задаётся формулой 2mx1. Примерами являются мультиплексоры: 2x1, 4x1, 8x1, 16x1.

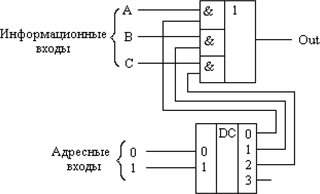

В состав мультиплексора обычно включают двоичный дешифратор, как показано на рисунке 10.1. Это позволяет управлять переключением информационных входов при помощи двоичных кодов, подаваемых на управляющие входы. Количество информационных входов в таких схемах выбирают кратным степени числа два.

Рисунок 10.1 – Схема подключения мультиплексора с дешифратором

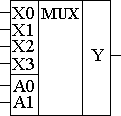

Условно графическое обозначение четырёхвходового мультиплексора с двоичным управлением приведено на рисунке 10.2. Входы A0 и A1 являются управляющими входами мультиплексора, определяющими адрес входного сигнала, который будет соединён с выходным выводом мультиплексора Y. Сами входные сигналы обозначены как X0, X1, X2 и X3.

Рисунок 10.2 - Четырёхвходовой мультиплексор

Демультиплексор

Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексор можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора для усиления входного сигнала лучше поставить инвертор.

Схема демультиплексора приведена на рисунке 1.1. В этой схеме для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор.

Рисунок 11.1 – Схема демультиплексора

Однако, если рассмотреть принципиальную схему самого дешифратора, то можно значительно упростить демультиплексор. Достаточно просто к каждому логическому элементу 'И', входящему в состав дешифратора просто добавить ещё один вход – In. Такую схему часто называют дешифратором с входом разрешения работы. Условно-графическое изображение демультиплексора приведено на рисунке 11.2.

Рисунок 11.2 Условно графическое обозначение демультиплексора с четырьмя выходами.

В этом обозначении вход In обозначен как вход E, а выходы не названы никак, оставлены только их номера.

Сумматор

Сумматор - логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учет знаков чисел, выравнивание порядков слагаемых и тому подобное.

Сумматоры классифицируются по разным признакам:

1. В зависимости от системы исчисления:

Двоичные

Двоично-десятичные (двоично кодированые)

Десятичные

Прочие (пример: амплитудные)

2. По количеству одновременно обрабатываемых разрядов складываемых чисел:

Одноразрядные

Многоразрядные

3. По числу входов и выходов одноразрядных двоичных сумматоров:

Четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

Полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд);

Полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд).