- •Раздел 1 Представление информации в вычислительных системах

- •Тема 1.1 Системы счисления

- •Тема 1.2 Арифметические операции в двоичной и двоично-десятичной системе счисления

- •Тема 1.3 Формы представления чисел

- •Тема 1.4 Кодирование чисел

- •Раздел 2 Основы алгебры логики

- •Тема 2.1 Логические основы

- •Тема 2.2 Логические элементы

- •Тема 2.3 Минимизация логических функций

- •Раздел 3 Функциональные узлы комбинационного типа

- •Тема 3.1 Шифраторы и дешифраторы

- •Тема 3.2 Мультиплексоры

- •Тема 3.3 Сумматоры

- •Тема 3.4 Цифровые компараторы

- •Тема 3.5 Преобразователи кодов

- •Раздел 4 Функциональные узлы последовательного типа

- •Тема 4.1Асинхронные триггеры

- •Тема 4.2 Синхронизируемые однотактные триггеры

- •Тема 4.3 Синхронизируемые двухтактные триггеры

- •Тема 4.4 Регистры

- •Тема 4.5 Счётчики

- •Раздел 5 Схемотехника запоминающих устройств

- •Тема 5.1 Оперативные запоминающие устройства статического типа

- •Тема 5.2 Оперативные запоминающие устройства динамического типа

- •Тема 5.3 Постоянные запоминающие устройства

- •Раздел 6 Цифро-аналоговые и аналого-цифровые преобразователи

- •Тема 6.1 Цифро-аналоговые преобразователи (цап)

- •Тема 6.2 Аналого-цифровые преобразователи (ацп)

Тема 3.4 Цифровые компараторы

55 Условное графическое изображение схемы является:

а )

УГО регистра

)

УГО регистра

б) цифрового компаратора

в) счётчика

г) сумматора

56 Данная микросхема является:

а ) сумматором для сложения двух четырёхразрядных слов

б) компаратором сравнения двух четырёхразрядных слова

в) регистром для восьмиразрядного слова

г) другое

57 Цифровые компараторы выполняются на основе схем:

а) сумматоров, б) полусумматоров, в) регистров, г) другое

Тема 3.5 Преобразователи кодов

56 УГО схемы а) сумматора, б) регистра, в) преобразователя кодов, г) счётчика

58 Для индикации цифр семисегментного индикатора применяется: а) дешифратор, б) шифратор, в) преобразователь кода, г) счётчик

Раздел 4 Функциональные узлы последовательного типа

Тема 4.1Асинхронные триггеры

59 Какая из нижеприведённых комбинаций реализуется на выходе RS-триггера, если на входе S действует логическая единица, а на входе R- логический нуль?

а)

Q

= 1

![]() = 1

б)

Q

= 0

= 1 в)

Q

= 1

= 0 г) Q

= 0

= 0

= 1

б)

Q

= 0

= 1 в)

Q

= 1

= 0 г) Q

= 0

= 0

60 Т – триггер называется: а) триггером задержки, б) счётным триггером, в) асинхронным триггером) г) синхронным триггером

61 D триггер имеет: а) один информационный вход, б) два информационных входа, в) два информационных входа и один синхровход, г) один информационный и один синхровход

Тема 4.2 Синхронизируемые однотактные триггеры

62 Синхронный триггер устанавливается в состояние Q = 1, если:

а) S=1 R=0 C = 0

б) S=1 R=1 C = 0

в) S=1 R=1 C = 1

г) S=1 R=0 C = 1

63 На выходе синхронного однотактного триггера сигнал логической единицы появляется:

а) при наличии логической единицы на любом входе триггера с приходом синхроимпульса по его заднему фронту

б) при наличии логической единицы на любом входе триггера с приходом синхроимпульса по его переднему фронту

в) при наличии логической единицы на входе S триггера с приходом синхроимпульса по его переднему фронту

г) при наличии логической единицы на входе R триггера с приходом синхроимпульса по его переднему фронту

Тема 4.3 Синхронизируемые двухтактные триггеры

64 Условие записи в триггер логической единицы:

а) J = 0 K=1 C=1

б) J = 1 K = 0 C = 0

в) J = 1 K =1 C =1

г) J = 1 K = 0 C = 1

65 Дополнительный вход S в схеме JK триггера служит: а) для запрещения приёма информации, б) для принудительной установки в 0, в) для принудительной установки в 1, г) для разрешения приёма информации

66 Дополнительный вход R в схеме JK триггера служит: а) для запрещения приёма информации, б) для принудительной установки в 0, в) для принудительной установки в 1, г) для разрешения приёма информации

67 В каком состоянии будет находиться JK триггер, если на оба его входа поданы логические единицы: а) на выходе будет 0

б) на выходе будет 1

в) сохранит предыдущее состояние

г) перебросится в состояние противоположное предыдущему

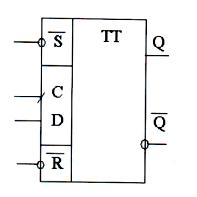

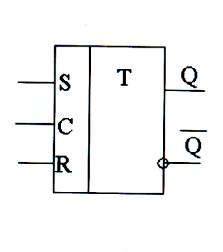

68 Входы S и R в сxеме данного триггера являются : а) информационными,

б) установочными, в) синхронизирующими, г) запрещающими

69

Диаграмма работы какого триггера

изображена на рисунке

а

а

б

б

в

в

г

г

70 При S=1 выход Q а) всегда равен 1, б) всегда равен 0 , в) равен 1, в зависимости от состояния на входах С и D, г) равен , в зависимости от состояния на входах С и D,

71 Данная схема является схемой: а) D –триггера, б) Т-триггера, в) RS- триггера,

г) RSC-триггера

72 Триггер управляется по входу С: а) по переднему фронту синхроимпульса, б) по заднему фронту синхроимпульса, в) потенциалом, г) другое