- •Определение ос. Назначение и функции операционной системы

- •Место ос в структуре вычислительной системы

- •Понятие ресурса. Управление ресурсами в вычислительной системе

- •Критерии эффективности и классы ос

- •Эволюция ос

- •Современный этап развития ос

- •Функциональные компоненты ос персонального компьютера

- •Требования, предъявляемые к современным ос

- •Классификации ос.

- •Архитектура ос. Ядро и вспомогательные модули

- •Классическая архитектура ос. Монолитные и многослойные ос

- •Микроядерная архитектура ос

- •Многослойная модель ядра ос

- •Функции ос по управлению процессами

- •Процессы и потоки

- •Состояния потока

- •Планирование и диспетчеризация потоков, моменты перепланировки

- •Алгоритм планирования, основанный на квантовании

- •Приоритетное планирование

- •Алгоритмы планирования ос пакетной обработки: «первым пришел – первым обслужен», «кратчайшая задача – первая», «наименьшее оставшееся время выполнения»

- •Алгоритмы планирования в интерактивных ос: циклическое, приоритетное, гарантированное, лотерейное, справедливое планирование

- •Алгоритм планирования Windows nt

- •Планирование в ос реального времени

- •Синхронизация процессов и потоков: цели и средства синхронизации

- •Ситуация состязаний (гонки). Способы предотвращения.

- •Способы реализации взаимных исключений: блокирующие переменные, критические секции, семафоры Дейкстры Блокирующие переменные

- •Критические секции

- •Семафоры

- •Взаимные блокировки. Условия, необходимые для возникновения тупика

- •Обнаружение взаимоблокировки при наличии одного ресурса каждого типа

- •Обнаружение взаимоблокировок при наличии нескольких ресурсов каждого типа

- •Предотвращение взаимоблокировки. Алгоритм банкира для одного вида ресурсов

- •Предотвращение взаимоблокировки. Алгоритм банкира для нескольких видов ресурсов

- •Синхронизирующие объекты ос: системные семафоры, мьютексы, события, сигналы, ждущие таймеры, мониторы

- •Мьютексы

- •Системные семафоры

- •События

- •Ждущие таймеры

- •Мониторы Хоара

- •Организация обмена данными между процессами (каналы, разделяемая память, почтовые ящики, сокеты)

- •Прерывания (понятие, классификация, обработка прерываний).

- •Средства вызова процедур.

- •Механизм вызова при переключении между задачами.

- •Обработка аппаратных прерываний.

- •Функции ос по управлению памятью

- •Виртуальная память

- •Алгоритмы распределения памяти без использования внешних носителей (фиксированные, динамические, перемещаемые разделы)

- •Страничное распределение памяти

- •Алгоритмы замещения страниц.

- •Оптимальный (нереализуемый)

- •Исключение недавно использованных страниц

- •Алгоритм «первый пришёл, первый ушёл» (fifo)

- •«Второй шанс»

- •Алгоритм нечастого использования

- •«Рабочий набор»

- •Сегментное распределение памяти.

- •Сегментно-страничное распределение памяти.

- •Средства поддержки сегментации памяти в мп Intel Pentium.

- •Сегментный режим распределения памяти в мп Intel Pentium.

- •Сегментно-страничный режим распределения памяти в мп Intel Pentium.

- •Средства защиты памяти в мп Intel Pentium.

- •Случайное отображение основной памяти на кэш.

- •Детерминированное отображение основной памяти на кэш.

- •Комбинированный способ отображения основной памяти на кэш.

- •Кэширование в мп Intel Pentium. Буфер ассоциативной трансляции Кэширование в процессоре Pentium

- •Буфер ассоциативной трансляции

- •Кэширование в мп Intel Pentium. Кэш первого уровня Кэширование в процессоре Pentium

- •Кэш первого уровня

- •Задачи ос по управлению файлами и устройствами

- •Организация параллельной работы устройств ввода-вывода и процессора

- •Разделение устройств и данных между процессами

- •Обеспечение удобного логического интерфейса между устройствами и остальной частью системы

- •Поддержка широкого спектра драйверов и простота включения нового драйвера в систему

- •Динамическая загрузка и выгрузка драйверов

- •Поддержка нескольких файловых систем

- •Поддержка синхронных и асинхронных операций ввода-вывода

- •Многослойная модель подсистемы ввода-вывода Общая схема

- •Менеджер ввода-вывода

- •Физическая организация жесткого диска Диски, разделы, секторы, кластеры

- •Файловая система. Определение, состав, типы файлов. Логическая организация файловой системы Цели и задачи файловой системы

- •Типы файлов

- •Иерархическая структура файловой системы

- •Физическая организация и адресация файлов

- •Fat. Структура тома. Формат записи каталога. Fat12, fat16, fat32

- •Ufs : структура тома, адресация файлов, каталоги, индексные дескрипторы

- •Ntfs: структура тома

- •Структура тома ntfs

- •Ntfs: типы файлов, организация каталогов. Структура файлов ntfs

- •Каталоги ntfs

- •Файловые операции. Процедура открытия файла. Открытие файла

- •Организация контроля доступа к файлам. Доступ к файлам как частный случай доступа к разделяемым ресурсам

- •Механизм контроля доступа

- •Контроль доступа к файлам на примере Unix.

- •Отказоустойчивость файловых систем.

- •Восстанавливаемость файловых систем

- •Протоколирование транзакций

- •Процедура самовосстановления ntfs.

- •Избыточные дисковые подсистемы raid

- •Многоуровневые драйверы

- •Дисковый кэш

- •Параметры, свойства и показатели эффективности ос.

- •Основные и частные показатели эффективности ос.

- •Мониторинг производительности ос.

- •Настройка и оптимизация ос.

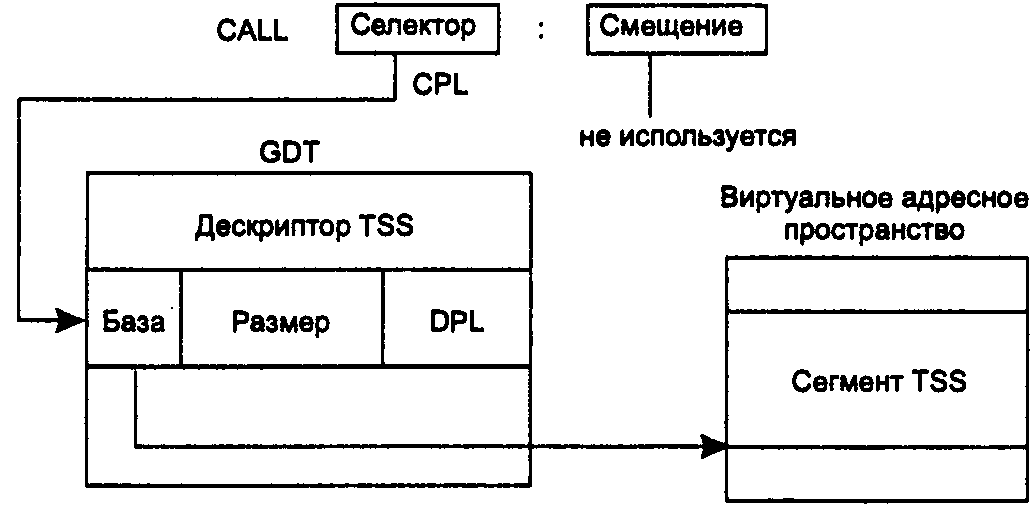

Механизм вызова при переключении между задачами.

Механизм вызова при переключении между задачами отличается от механизма вызова процедур. В этом случае селектор команды CALL должен указывать на дескриптор системного сегмента TSS. Сегмент TSS хранит контекст задачи, то есть информацию, которая нужна для восстановления выполнения прерванной в произвольный момент времени задачи. Контекст задачи включает значения регистров процессора, указатели на открытые файлы и некоторые другие, зависящие от операционной системы, переменные. Скорость переключения контекста в значительной степени влияет на производительность многозадачной операционной системы.

Как и в случае вызова процедуры, имеются два способа вызова задачи — непосредственный вызов путем указания селектора дескриптора сегмента TSS нужной задачи в поле команды CALL и косвенный вызов через шлюз вызова задачи.

Однако условие, разрешающее непосредственный вызов задачи, отличается от условия непосредственного вызова процедуры: вызов возможен только в случае, если вызывающий код обладает уровнем привилегий, не меньшим, чем вызываемая задача (CPL<DPL). Здесь применяется то же правило, что и при доступе к данным. Действительно, операционная система, работающая с высоким уровнем привилегий, должна иметь возможность запускать на выполнение пользовательские задачи, работающие с низким уровнем привилегий. В этом случае ОС не поручает ненадежному низкоуровневому коду выполнять некоторые свои функции, как это происходило бы при вызове низкоуровневых процедур, а просто выполняет переключение между пользовательскими процессами.

При вызове через шлюз вызывающему коду достаточно иметь права доступа к шлюзу, а шлюз может указывать на дескриптор TSS в таблице GDT с равным или более высоким уровнем привилегий. Поэтому через шлюз вызова задачи можно выполнить переключение на более привилегированную задачу.

Непосредственный вызов задачи показан на рисунке. При переключении задач процессор выполняет следующие действия:

Выполняется команда CALL, селектор которой указывает на дескриптор сегмента типа TSS. Происходит проверка прав доступа, успешная при CPL<DPL;

В TSS текущей задачи сохраняются значения регистров процессора. На текущий сегмент TSS указывает регистр процессора TR, содержащий селектор сегмента;

В TR загружается селектор сегмента TSS задачи, на которую переключается процессор;

Из нового TSS в регистр LDTR переносится значение селектора таблицы LDT в таблице GDT задачи;

Восстанавливаются значения регистров процессора (из соответствующих полей нового сегмента TSS);

В поле селектора возврата нового сегмента TSS заносится селектор сегмента TSS снимаемой с выполнения задачи для организации возврата к ней в будущем.

Рисунок 12. Непосредственный вызов задачи

Вызов задачи через шлюз происходит аналогично, добавляется только этап поиска дескриптора сегмента TSS по значению селектора дескриптора шлюза вызова.

Обработка аппаратных прерываний.

Аппаратные прерывания бывают маскируемыми и немаскируемыми.

Маскируемые прерывания вызываются сигналом INTR на одном из входов микросхемы процессора. При его возникновении процессор завершает выполнение очередной инструкции, сохраняет в стеке значение регистра признаков программы EFLAGS и адреса возврата, а затем считывает с входов шины данных байт вектора прерываний и в соответствии с его значением передает управление одной из 256 процедур обработки прерываний.

Маскируемость прерываний управляется флагом разрешения прерываний IF (Interrupt Flag), находящимся в регистре EFLAGS процессора. При IF-1 маскируемые прерывания разрешены, а при IF-0 — запрещены. Для явного управления флагом IF в процессоре имеются чувствительные к уровню привилегий инструкции разрешения маскируемых прерываний STI (Set Interrupt flag) и запрета маскируемых прерываний CLI (CLear Interrupt flag). Эти инструкции разрешается выполнять при CPL≤IOPL. Кроме того, состояние флага изменяется неявным образом в некоторых ситуациях, например он сбрасывается процессором при распознавании сигнала INTR, чтобы процессор не входил во вложенные циклы процедуры обработки одного и того же прерывания. Процедура обработки прерывания завершается инструкцией IRET, по которой происходит извлечение из стека признаков EFLAGS, адреса возврата, установка флага разрешения прерываний IF и передача управления по адресу возврата. Для маскируемых прерываний в процессоре отведены процедуры обработки прерываний с номерами 32-255. Соответствие между сигналом запроса прерывания на шине ввода-вывода (например, сигналом IRQn на шине PCI) и значением вектора задается внешним по отношению к процессору блоком компьютера — контроллером прерываний.

Немаскируемое прерывание происходит при появлении сигнала NMI (Non Maskable Interrupt) на входе процессора. Этот сигнал всегда прерывает работу процессора, вне зависимости от значения флага IF. При обработке немаскируемого прерывания вектор не считывается, а управление всегда передается процедуре с номером 2, описываемой третьим элементом таблицы процедур обработки прерываний. Немаскируемые прерывания предназначаются для реакции на «сверхважные» для компьютерной системы события, например сбой по питанию. В ходе процедуры обслуживания немаскируемого прерывания процессор не реагирует на другие запросы немаскируемых и маскируемых прерываний до тех пор, пока не будет выполнена команда IRET. Если при обработке немаскируемого прерывания возникает новый сигнал NMI, то он фиксируется и обрабатывается после завершения обработки текущего прерывания, то есть после выполнения команды IRET.

При одновременном возникновении запросов прерываний различных типов процессор Pentium разрешает коллизию с помощью приоритетов. Немаскируемые прерывания имеют более высокий приоритет, чем маскируемые. Приоритетность внутри маскируемых прерываний устанавливается не процессором, а контроллером прерываний (процессор не может этого сделать, так как для него все маскируемые запросы представлены одним сигналом INTR). Проверка некорректных ситуаций, порождающих исключения, выполняется в процессоре в соответствии с определенной последовательностью.