- •Асинхронный rs триггер. Условное обозначение, таблица состояний, временные диаграммы.

- •Синхронный rs триггер. Условное обозначение, таблица состояний, временные диаграммы.

- •Т триггер. Условное обозначение, таблица состояний, временные диаграммы.

- •D триггер. Условное обозначение, таблица состояний, временные диаграммы.

- •1) По способу записи информации: синхронный и асинхронный.

- •2) По способу организации логических связей: rs, t, d, jk триггеры.

- •1) По способу записи информации: синхронный и асинхронный.

- •2) По способу организации логических связей: rs, t, d, jk триггеры.

- •Четырех разрядный параллельный регистр. Назначение, условное обозначение, принцип работы.

- •Четырех разрядный последовательный регистр. Назначение, условное обозначение, принцип работы.

- •Трех разрядный дешифратор. Назначение, условное обозначение, принцип работы.

- •Восьми разрядный шифратор. Назначение, условное обозначение, принцип работы.

- •Трех разрядный суммирующий счетчик. Назначение, условное обозначение, принцип работы, временные диаграммы.

- •Суммирующий четырех разрядный двойной счетчик на т триггерах с последовательным переносом.

- •Трех разрядный вычитающий двоичный счётчик. Назначение, условное обозначение, принцип работы, временные диаграммы.

- •Оперативный зу.

- •Оперативное запоминающее устройство. Назначение, структурная схема, принцип работы в режиме считывания.

- •Назначение, структура, принцип работы программируемого постоянного запоминающего устройства.

- •Назначение, структура, принцип работы масочного постоянного запоминающего устройства.

- •Назначение, структура, принцип работы перепрограммируемого постоянного запоминающего устройства.

- •Назначение, классификация микропроцессоров.

- •Структурная схема микропроцессора, принцип работы.

- •Устройство управления. Назначение, структурная схема, принцип работы.

- •Арифметико-логическое устройство. Назначение, структурная схема, принцип работы.

Назначение, классификация микропроцессоров.

Микропроцессор – это программно управляемое логическое устройство, предназначенное для обработки цифровой информации.

Классификация:

1. по назначению: универсальные (широкое применение, для решения различных задач); специализированные (для решения конкретных задач узкого профиля).

2. по разрядности: с фиксированной и изменяемой разрядностью (8-16-32разряда)

3. по числу внутренних регистров: 2-х; 4-ми; 16-ти; 64-ех.

4. по принципу организации управления вычислительным процессом: схемного; микропрограммного; смешанного.

5. по способу синхронизации: синхронного (рабочий цикл постоянный); асинхронного (меняется от команды).

Все МП делятся на 3 группы:

1. с полным набором команд. CISC – Complete Instruction Set Computing (используются в большинстве IBM XP ПК).

2. с сокращением набора команд. RISC – Reduced Instruction Set Computing, в этих МП содержится набор только простых, чаще всего встречающихся команд. При решении более сложных команд в МП производится сборка из простых команд.

3. с минимальным набором команд. MISC – Minimum Instruction Set Computing (на стадии разработки).

Характеристики МП.

1. Система команд – это максимальное число команд и их состав, которое может обрабатывать МП.

2. Разрядность обрабатываемых данных.

3. Быстродействие.

4. Производительность.

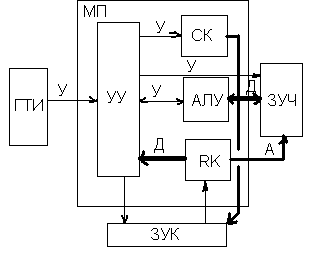

Структурная схема микропроцессора, принцип работы.

Структурная схема МП.

ГТИ – генератор тактовых импульсов

УУ – устройство управления

АЛУ – арифметика логическое устройство.

СК- счетчик команд

ЗУК / ЗУЧ – запоминающие устройства чисел / команд

RK – регистр команд

У/ Д /А – шины управления / данных / адреса

ГТИ вырабатывает тактовые импульсы для управления МП. По приходу сигнала УУ вырабатывает следующие действия: подает сигнал на СК, содержимое которого помешается на ША и далее на ЗУК, где по полученному адресу открывается команда, и она через ШД поступает в RK.

- Если команда обработки, то она поступает на УУ, где обрабатывается.

- Если команда арифметика логическая, то она через ША поступает в ЗУЧ, где достаются данные, которые обрабатываются в АЛУ. по завершению этого цикла счетчик команд автоматически увеличивает свое содержимое на 1.

Устройство управления. Назначение, структурная схема, принцип работы.

Команда содержит в себе адрес и код операции, если команда безадресная, то код из регистра поступает в дешифратор. Он его расшифровывает и шифратор операций вырабатывает управляющие сигналы к тем устройствам к которым они адресуются.

Если поступает адрес в команде, то он расшифровывается в БРА и по шине адреса передается к тому ЗУ к которому адресовано

СДК- вносит корректирующее воздействие

КОП-Код операции

БРА-блок расшифровки адреса

Арифметико-логическое устройство. Назначение, структурная схема, принцип работы.

Арифметические и логические операции над числами (операндами, словами) выполняются в главной части процессора- АЛУ.

УУПустройство

управления проц.

УУПустройство

управления проц.

ЗУПЗапоминающее устройство проц.

Роль аккумулятора выполняет Рг1

См сумматор

Рг1 и Рг2 хранение слагаемых, вычитаемых…

УУВ устройство управл вычисления

ШЗД ШЧД шины записи и данных

С УП по IE в УУВ поступают тактовые импульсы, а из УУВ сигнал об окончании вычислений.

Из УП код арифм или лог опер поступает в УУВ, где формируются сигналы, соответствующие данной операции. Затем из ЗП выбирается первый операнд ( по адресу указанному в команде), который по ШЧД поступает на Рг1. Второй операнд, выбранный из ЗП по второму адресу поступает также в Рг2, После приема обоих операндов начинается выполнение операции, в ходе которой используются сигналы переноса, делаются необходимые сдвиги. Результат операции формируется в СМ. Сигналы, характеризующие признаки результата в См, называются признаками. Эти сигналы являются также составной частью понятия Состояние процессора.

По окончании формирования результата выбирается сигнал признака конца операции, в соответствии с которым результат из См поступает через ШЗД в ЗП по адресу. Кроме формирования результата в АЛУ могут выбираться различные сигналы, обозначающие признаки результата (признак переполнения, признак отрицательного результата…). Эти признаки поступают в УП и влияют на дальнейший ход выч процесса.