Танненбаум Е. Архітектура компютера [pdf]

.pdf

Intel IA-64 |

423 |

щие 11 команд связывают две цепочки и два целых числа в одну цепочку в этом буфере и передают ее в println для вывода на экран.

Если п не равно 1, управление передается к L1. Переменная к вычисляется простым путем с использованием арифметических операций над числами в стеке. Затем совершаются три вызова один за другим.

Машина IJVM содержит ряд команд для вызова процедур. В данном случае компилятор использовал три разные команды. Все они содержат 2-байтный операнд, который индексирует набор констант, чтобы найти указатель надескриптор, сообщающий все о вызываемой процедуре. Константы #10, #11 и т. д. — индексы в наборе констант.

Наличие нескольких типов команд для вызова процедур связано с оптимизацией. Команда INVOKESTATIC используется для вызова статических процедур, например towers. Команда INVOKESPECIAL применяется для вызова процедур инициализации, нестандартных процедур и процедур надкласса текущего класса. Наконец, команда INVOKEVIRTUAL используется для внутренних (библиотечных) вызовов.

Intel IA-64

Со временем увеличивать скорость работы IA-32 становилось все сложнее и сложнее. Единственным возможным решением этой проблемы стала разработка совершенно новой архитектуры команд. Новая архитектура, которая разрабатывалась совместно компаниями Intel и Hewlett Packard, получила название IA-64. Это полностью 64-битная машина от начала до конца. Появление полной серии процессоров, в которых реализуется эта архитектура, ожидается в ближайшие годы. Самым первым процессором этого типа был процессор Merced с высокой производительностью, хотя в будущем наверняка появится полный спектр процессоров разного уровня.

Поскольку все, что делает компания Intel, очень важно для компьютерной промышленности, мы подробно рассмотрим архитектуру IA-64. Однако ключевые идеи этой архитектуры уже очень хорошо известны многим исследователям, поэтому они могут отражаться в других разработках. Вообще, некоторые из них уже реализованы в разных формах в экспериментальных системах. В следующих разделах мы изложим, с какой проблемой столкнулась компания Intel, каким образом архитектура IA-64 помогла справиться с этой проблемой и как работают ключевые идеи этого проекта.

Проблема с Pentium II

Основная проблема заключалась в том, что IA-32 — это старая архитектура команд с совершенно не подходящими для современной техники свойствами. Это архитектура CISC с командами разной длины и огромным количеством различных форматов, которые трудно декодировать быстро и на лету. Современная техника лучше всего работает с архитектурами команд RISC с командами одной

4 2 4 Глава 5. Уровень архитектуры команд

длины и с кодом операции фиксированной длины, который легко декодировать. Команды IA-32 можно разбить на микрооперации типа RISC во время выполнения программы, но для этого требуется дополнительное аппаратное обеспечение (пространство на микросхеме), что занимает время и усложняет разработку. Это первый недостаток.

IA-32 — это архитектура, которая ориентирована на двухадресные команды. В настоящее время популярны архитектуры команд типа загрузка/сохранение, где обращение к памяти совершается только в тех случаях, когда нужно поместить операнды в регистры, а все вычисления выполняются с использованием трехадресных регистровых команд. Поскольку скорость работы процессора растет гораздо быстрее, чем скорость работы памяти, положение дел с IA-32 со временем все больше ухудшается. Это второй недостаток.

Архитектура IA-32 содержит небольшой и нерегулярный набор регистров. Из-за столь малого числа регистров общего назначения (четыре или шесть, в зависимости от того, как считать ESI и EDI) постоянно нужно записывать в память промежуточные результаты, и поэтому приходится делать дополнительные обращения к памяти, даже когда они по логике вещей не нужны. Это третий недостаток.

Из-за недостаточного числа регистров возникает множество ситуаций зависимостей, особенно WAR-зависимостей, поскольку промежуточные результаты нужно куда-то поместить, а дополнительных регистров нет. При недостатке регистров требуется переименование регистров в скрытые регистры. Во избежание слишком частых промахов кэш-памяти команды приходится выполнять не по порядку. Однако семантика архитектуры IA-32 определяет точные прерывания, поэтому команды, выполняемые не по порядку, должны записывать результаты в выходные регистры в строгом порядке. Для всего этого требуется очень сложное аппаратное обеспечение. Это четвертый недостаток.

Чтобы скорость работы была высокой, нужна сильно конвейеризированная система (12 стадий). Однако это значит, что для выполнения команды потребуется 11 циклов. Следовательно, становится существенным точное предсказание переходов, поскольку в конвейер должны попадать только нужные команды. Но даже при низком проценте неправильных предсказаний существенно снижается производительность. Это пятый недостаток.

Чтобы избежать проблем с неправильным прогнозированием переходов, процессору приходится осуществлять спекулятивное выполнение команд со всеми вытекающими отсюда последствиями. Это шестой недостаток.

Мы не будем перечислять недостатки дальше, поскольку уже сейчас ясно, что за ними кроется реальная проблема. И мы еще не упомянули, что 32-битные адреса архитектуры IA-32 ограничивают размер отдельных программ до 4 Гбайт, а это требование очень сложно выполнять на дорогостоящих серверах с высокой производительностью.

Ситуации с IA-32 можно сравнить с положением в небесной механике как раз перед появлением Коперника. В те времена в астрономии доминировала теория, что Земля является центром Вселенной и неподвижна, а планеты движутся вокруг нее. Однако новые наблюдения показывали все больше и больше несоответствий этой теории действительности, и в конце концов теория полностью разрушилась.

Intel IA-64 |

425 |

Компания Intel находится приблизительно в таком же положении. Огромное количество транзисторов в процессоре Pentium II предназначено для переделывания команд CISC в команды RISC, разрешения конфликтов, прогнозирования переходов, исправления неправильных предсказаний и решения многих других задач подобного рода, оставляя лишь незначительное число транзисторов на долю реальной работы, которая нужна пользователю. Поэтому компания Intel пришла к следующему выводу: нужно выбросить IA-32 и начать все заново (IA-64).

Модель IA-64: открытое параллельное выполнение команд

Первой реализацией архитектуры IA-32 был 64-битный процессор RISC (один из примеров этого процессора — UltraSPARC II). Поскольку архитектура IA-64 была разработана совместно с компанией Hewlett Packard, в ее основу, несомненно, легла архитектура PA-RISC. Merced — это двухрежимный процессор, который может выполнять и программы IA-32, и программы IA-64, но мы будем говорить только об архитектуре IA-64.

Архитектура IA-64 — это архитектура типа загрузка/сохранение с 64-битными адресами и 64-битными регистрами. Здесь имеется 64 регистра общего назначения, доступных для программ IA-64 (и дополнительные регистры для программ IA-32). Все команды имеют фиксированный формат: код операции, два 6-битных поля для указания входных регистров, одно 6-битное поле для указания выходного регистра и еще одно 6-битное поле, которое мы обсудим позже. Большинство команд берут два регистровых операнда, выполняют над ними какую-нибудь операцию и помещают результат в выходной регистр. Для параллельного выполнения различных операций существует много функциональных блоков. Как видим, пока ничего необычного в этой архитектуре нет. Большинство RISC-процессоров имеют сходную архитектуру.

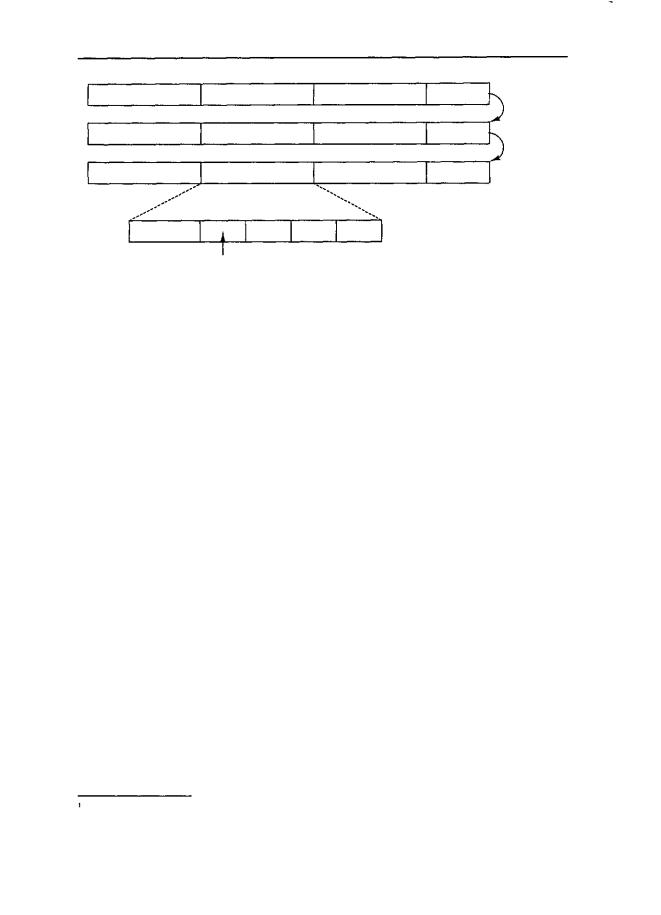

А необычной здесь является идея о пучке связанных команд. Команды поступают группами по три штуки (рис. 5.31). Каждая такая группа называется пучком. Каждый 128-битный пучок содержит три 40-битные команды фиксированного формата и 8-битный шаблон. Пучки могут быть связаны вместе (при этом используется бит конца пучка), поэтому в одном пучке может присутствовать более трех команд. Формат содержит информацию о том, какие команды могут выполняться параллельно. При такой системе и при наличии большого числа регистров компилятор может выделять блоки команд и сообщать процессору, что эти команды можно выполнять параллельно. Таким образом, компилятор должен переупорядочивать команды, проверять, нет ли взаимозависимостей, проверять доступность функциональных блоков и т. д. вместо аппаратного обеспечения. Основная идея состоит в том, что работа упорядочивания и распределения команд RISC передается от аппаратного обеспечения компилятору. Именно поэтому эта технология называетсяEPIC(ExplicitlyParallelInstructionComputing—технологияпарал-

лельной обработки команд с явным параллелизмом).

Intel IA-64 |

427 |

В современных машинах все команды являются безусловными в том смысле, что когда центральный процессор натыкается на команду, он просто ее выполняет. Здесь никогда не решается вопрос: «Выполнять или не выполнять?» Напротив, в архитектуре с предикацией команды содержат условия, которые сообщают, в каком случае нужно выполнять команду, а в каком — нет. Именно этот сдвиг от безусловных команд к командам с предикацией позволяет избавиться от многих условных переходов. Вместо того чтобы выбирать ту или иную последовательность безусловных команд, все команды сливаются в одну последовательность команд с предикацией, используя разные предикаты для различных команд.

Чтобы понять, как работает предикация, рассмотрим простой пример (листинги 5.10-5.12), в котором показано условное выполнение команд (условное выполнение — предтеча предикации). В листинге 5.10 мы видим оператор if. В листинге 5.11 мы видим трансляцию этого оператора в три команды: команду сравнения, команду условного перехода и команду перемещения.

Листинг5.10. Оператор if

if (Rl=0) R2=R3:

Листинг 5 . 1 1 . Код на ассемблере для листинга 5.10

CMP R1.0

BNE L1 MOVR2.R3

L1:

Листинг 5.12. Условная команда CMOVZ R2.R3.R1

В листинге 5.12 мы избавились от условного перехода, используя новую команду CMOVZ, которая является условным перемещением. Эта команда проверяет, равен ли третий регистр R1 нулю. Если да, то команда копирует R3 в R2. Если нет, то команда не выполняет никаких действий.

Если у нас есть команда, которая может копировать данные, когда какой-либо регистр равен нулю, значит, у нас может быть и такая команда, которая копирует данные, если какой-нибудь регистр не равен нулю. Пусть это будет команда CMOVN. При наличии обеих команд мы уже на пути к полному условному выполнению. Представим оператор if с несколькими присваиваниями в части then и несколькими присваиваниями в части el se. Весь этот кусок программы можно транслировать в код, который будет устанавливать какой-нибудь регистр на 0, если условие не выполнено, и на какое-нибудь другое значение, если условие выполнено. Следуя установке регистров, присваивания в части then можно скомпилировать в последовательность команд CMOVN, а присваивания в части el se — в последовательность командCMOVZ.

Все эти команды, регистровая установка, CNOVN и CMOVZ формируют единый основной блок без условных переходов. Команды можно даже переупорядочить при компиляции или во время выполнения программы. Единственное требование при этом состоит в том, чтобы условие было известно к тому моменту, когда условные команды уже нужно помещать в выходные регистры (то есть где-то

428 Глава 5. Уровень архитектуры команд

в конце конвейера). Простой пример куска программы с then и el se приведен в листингах 5.13-5.15.

Листинг5.13.Операторif

if(Rl=0) { R2=R3; R4=R5;

} else { R6=R7: R8=R9:

}

Листинг 5.14. Код на ассемблере для листинга 5.13

CMP R1.0

BNE L1

MOV R2.R3

MOV R4.R5 BR L2

LI: MOV R6.R7 MOV R8.R9

L2:

Л и с т и н г 5 . 1 5 . Условное выполнение

CMOVZ R2.R3.R1

CMOVZ R4.R5.R1

CMOVN R6.R7.R1

CMOVN R8.R9.R1

Мы показали только очень простые условные команды (взятые из Pentium II), но в архитектуре IA-64 все команды предикатны. Это значит, что выполнение каждой команды можно сделать условным. Дополнительное 6-битное поле, о котором мы упомянули выше, выбирает один из 64 1-битных предикатных регистров. Следовательно, оператор i f может быть скомпилирован в код, который устанавливает один из предикатных регистров на 1, если условие истинно, и на 0, если условие ложно. Одновременно с этим данное поле автоматически устанавливает другой предикатный регистр на обратное значение. При использовании предикации машинные команды, которые формируют операторы then и el se, будут сливаться в единый поток команд, первый из них — с использованием предиката, а второй — с использованием его обратного значения.

Листинги 5.16-5.18 показывают, как можно использовать предикацию для устранения переходов. Команда CMPEQ сравнивает два регистра и устанавливает предикатный регистр Р4 на 1, если они равны, и на 0, если они не равны. Кроме того, команда устанавливает парный регистр, например Р5, на обратное условие. Теперь команды частей i f и then можно поместить одну за другой, причем каждая из них связывается с каким-нибудь предикатным регистром (регистр указывается в угловых скобках). Сюда можно поместить любой код, при условии что каждая команда предсказывается правильно.

Листинг5.16. Операторif

if(Rl==R2)

R3=R4+R5:

Else

R6=R4-R5

Intel IA-64 |

429 |

Листинг 5.17. Код на ассемблере для листинга 5.16

CMP R1.R2 BNEL1 MOV R3.R4 ADD R3.R5 BR L2

LI: MOV R6.R4 SUB R6.R5

L2:

Листинг 5.18. Выполнение с предикацией

CMPEQ R1.R2.P4 <Р4> ADD R3.R4.R5 <Р5> SUB R6.R4.R5

Вархитектуре IA-64 эта идея доведена до логического конца: здесь с предикатными регистрами связаны и команды сравнения, и арифметические команды, а также некоторые другие команды, выполнение которых зависит от какого-либо предикатного регистра. Команды с предикацией могут помещаться в конвейер последовательно без каких-либо проблем и простаиваний. Поэтому они очень полезны.

Вархитектуре IA-64 предикация происходит следующим образом. Каждая команда действительно выполняется, и в самом конце конвейера, когда уже нужно сохранять результат в выходной регистр, производится проверка, истинно ли предсказание. Если да, то результаты просто записываются в выходной регистр. Если предсказание ложно, то записи в выходной регистр не происходит. Подробно о предикации вы можете прочитать в книге [34].

Спекулятивная загрузка

Еще одна особенность IA-64 — наличие спекулятивной загрузки. Если команда LOAD спекулятивна и оказывается ложной, то вместо того чтобы вызвать исключение (exception), она просто останавливается и сообщает, что регистр, с которым она связана, недействителен. Если этот регистр будет использоваться позднее, то произойдет исключение (exception).

Компилятор должен перемещать команды LOAD в более ранние позиции относительно других команд с тем, чтобы они выполнялись еще до того, как они понадобятся. Поскольку выполнение этих команд начинается раньше, чем нужно, они могут завершиться еще до того, как потребуются результаты. Компилятор вставляет команду CHECK в том месте, где ему нужно получить значение определенного регистра. Если значение там уже есть, команда CHECK работает как NOP, и выполнение программы сразу продолжается дальше. Если значения в регистре еще нет, следующая команда должна простаивать.

Итак, машина с архитектурой IA-64 имеет несколько источников повышения скорости. Во-первых, это современная конвейеризированная трехадресная машина RISC типа загрузка/сохранение. Во-вторых, компилятор определяет, какие команды могут выполняться одновременно, не вступая в конфликт, и группирует эти команды в пучки. Таким образом, процессор может просто распределять пучок, не совершая никаких проверок. В-третьих, предикация позволяет сливать команды обоих переходов от оператора if, устраняя при этом условный переход, а также и само прогнозирование этого перехода. Наконец, спекулятивная загрузка позволя-

Вопросы и задания |

431 |

организацией, состоящую из нескольких десятков мегабайтов и содержащую такие команды,какMOVE,ADDиBEQ.

В большинстве современных компьютеров память организована в виде последовательности байтов, при этом 4 или 8 байтов группируются в слова. Обычно в машине имеется от 8 до 32 регистров, каждый из которых содержит одно слово.

Команды обычно имеют 1,2 или 3 операнда, обращение к которым происходит с помощью различных способов адресации: непосредственной, прямой, регистровой, индексной и т. д. Команды обычно могут перемещать данные, выполнять унарные и бинарные операции (в том числе арифметические и логические), совершать переходы, вызывать процедуры, осуществлять циклы, а иногда и выполнять некоторые операции ввода-вывода. Типичные команды перемещают слово из памяти в регистр или наоборот, складывают, вычитают, умножают или делят два регистра или регистр и слово из памяти, или сравнивают два значения в регистрах или памяти. Обычно в компьютере содержится не более 200 команд.

Для осуществления передачи управления на втором уровне используется ряд элементарных действий: переходы, вызовы процедур, вызовы сопрограмм, ловушки и прерывания. Переходы нужны для того, чтобы остановить одну последовательность команд и начать новую. Процедуры нужны для того, чтобы изолировать какой-то блок программы, который можно вызывать из различных мест этой же программы. Сопрограммы позволяют двум потокам управления работать одновременно. Ловушки используются для сообщения об исключительных ситуациях (например, о переполнении). Прерывания позволяют осуществлять процесс вводавывода параллельно с основным вычислением, при этом центральный процессор получает сигнал, как только ввод-вывод завершен.

Задачу «Ханойская башня» можно решить с использованием рекурсии. Наконец, архитектура IA-64 использует модель вычисления EPIC. Для повы-

шения скорости работы в этой архитектуре предусмотрены предикация и спекулятивная загрузка. IA-64 может иметь значительное преимущество над Pentium II, но она возлагает на компилятор огромное бремя параллелизма.

Вопросы и задания

1.В Pentium II команды могут содержать любое число байтов, даже нечетное.

ВUltraSPARC II все команды содержат четное число байтов. В чем преимущество системы Pentium II?

2.Разработайте расширенный код операций, который позволяет закодировать

в36-битной команде следующее:

•7 команд с двумя 32-битными адресами и номером одного 3-битного регистра;

•500 команд с одним 15-битным адресом и номером одного 3-битного регистра;

•50 команд без адресов и регистров.

4 3 2 Глава 5. Уровень архитектуры команд

3.Можно ли разработать такой расширенный код операций, который позволял бы кодировать в 12-битной команде следующее:

•4 команды с тремя регистрами;

•255 команд с одним регистром;

•16 команд без регистров.

(Размер регистра составляет 3 бита.)

4.В некоторой машине имеются 16-битные команды и 6-битные адреса. Одни команды содержат один адрес, другие — два. Если существует п двухадресных команд, то каково максимальное число одноадресных команд?

5.Имеется одноадресная машина с регистром-аккумулятором. Ниже приведены значения некоторых слов в памяти:

•слово 20 содержит число 40;

+слово 30 содержит число 50;

•слово 40 содержит число 60;

•слово 50 содержит число 70.

Какие значения следующие команды загрузят в регистр-аккумулятор?

•LOAD IMMEDIATE 20

•LOAD DIRECT 20

•LOAD INDIRECT20

•LOAD IMMEDIATE 30

•LOAD DIRECT30

•LOAD INDIRECT30.

6.Для каждого из четырех видов машин — безадресной, одноадресной, двухадресной и трехадресной — напишите программу вычисления следующего выражения:

X=(A+BxC)/(D-ExF).

7. В наличии имеются следующие команды:

• безадресные: PUSHМ

POP М

ADD

SUB

MUL

DIV

• одноадресные: LOADM

STORE M

ADD M