- •Тема 1. Математическое введение в цифровую технику.

- •Тема 2. Переходные процессы в rc-цепях.

- •Тема 3. Формирователи и генераторы импульсных сигналов.

- •Глава 8. Синтез комбинационных цифровых устройств различного назначения.

- •8.2. Микросхемы комбинационного типа малой степени интеграции и их применение при синтезе кцу.

- •8.3. Типовые кцу.

- •8.3.1 Дешифраторы и шифраторы.

- •8.3.2 Мультиплексоры и демультиплексоры.

- •8.3.3 Цифровые компараторы.

- •8.3.4 Сумматоры.

- •8.3.5 Преобразователи кодов.

- •Глава 9. Цифровые устройства последовательностного типа.

- •9.1. Триггеры.

- •9.2. Счетчики.

- •9.2.1. Двоичные счетчики.

- •9.2.2. Недвоичные счетчики.

- •9.3. Регистры.

- •9.3.1. Параллельные регистры.

- •9.3.2. Последовательные регистры.

- •9.3.3. Последовательно-параллельные регистры.

- •Глава 10. Аналого-цифровые и цифро-аналоговые преобразователи.

- •10.1. Дискретизация и квантование, характеристики ацп и цап.

- •10.2. Цифро-аналоговые преобразователи.

- •10.2.1. Цап с матрицей из взвешенных резисторов.

- •10.2.2. Цап с матрицей r-2r.

- •10.3. Аналого-цифровые преобразователи.

- •10.3.1. Ацп последовательного счета.

- •10.3.2. Интегрирующие ацп.

- •10.3.3. Ацп последовательного приближения.

- •10.3.4. Ацп параллельного действия.

- •Глава 11. Программируемые логические интегральные схемы.

- •11.1. Принципы структурной организации программируемых логических интегральных схем.

- •11.2. Особенности проектирования цифровых устройств на базе плис.

8.3.3 Цифровые компараторы.

Цифровой компаратор предназначен для сравнения двух n-разрядных двоичных чисел A={a1, a2, ..., an} и B={b1, b2, ..., bn}. В результате сравнения может установливаться одно из соотношений: =, ≠; >; <; ≥; ≤. Выходная функция F принимает единичное значение, если проверяемое соотношение выполняется или нулевое – если не выполняется. Цифровой компаратор позволяет реализовывать ту часть алгоритма измерения в цифровой измерительной технике, в которой заложена процедура сравнения неизвестного значения измеряемой величины с цифровой мерой. Рассмотрим синтез компаратора для реализации функции равенства двух n-разрядных двоичных кодов. Факты равенства, больше и меньше отдельных разрядов определим функциями f(A=B)i, f(A>B)i и f(A<B)i, заданной следующей таблицей истинности 8.9:

Таблица 8.9.

Входы |

Выходы |

|||

ai |

bi |

f(A=B)i |

f(A>B)i |

f(A<B)i |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

Тогда факт

неравенства разрядов будет определяться

инверсным значением функции

![]() .

Определим ФАЛ для f(A=B)i,

соответствующую приведенной таблице

истинности

.

Определим ФАЛ для f(A=B)i,

соответствующую приведенной таблице

истинности

![]() .

.

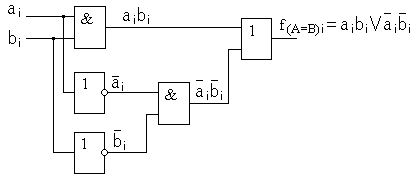

Синтезированная структурная схема в соответствии с формулой для f(A=B)i имеет вид, представленный рис. 8.22.

Рис. 8.22. Функциональная схема устройства сравнения одноразрядных кодов.

Выполним следующие преобразования над функцией f(A=B)i, используя тождества алгебры логики:

![]() ,

,

т.е. окончательно имеем инверсию функции исключающее ИЛИ.

Функция неравенства

одного разряда

тогда будет выражаться через прямое

значение функции Исключающее ИЛИ. Для

перехода от равенства (неравенства)

отдельных разрядов к функции равенства

F(A=B)

(неравенства

![]() )

всего n-разрядного

кода необходимо установить факт наличия

логических единиц во всех функциях

f(A=B)i

(

).

Это осуществляется n-входовым

элементом И. ФАЛ для функции F(A=B)

с учетом использования функции инверсии

исключающего ИЛИ имеет вид

)

всего n-разрядного

кода необходимо установить факт наличия

логических единиц во всех функциях

f(A=B)i

(

).

Это осуществляется n-входовым

элементом И. ФАЛ для функции F(A=B)

с учетом использования функции инверсии

исключающего ИЛИ имеет вид

![]() .

.

Функция f(A>B)i

одноразрядного числа согласно таблице

8.9 будет реализовываться двухвходовым

элементом И, на один вход которого будет

подаваться разряд ai

в прямом виде, а на второй – разряд

![]() в инверсном виде, т.е.

в инверсном виде, т.е.

![]() .

Несколько сложнее обстоит дело со схемой

сравнения n-разрядных

слов на «больше». Для этого анализ

неравенства должен выполняться

последовательно в направлении от старших

разрядов в сторону младших. Младшие

разряды сравниваются при условии

равенства старших. Тогда логика сравнения

на «больше» для двухразрядного слова

с учетом равенства/неравенства старшего

разряда может быть представлена в

следующем виде

.

Несколько сложнее обстоит дело со схемой

сравнения n-разрядных

слов на «больше». Для этого анализ

неравенства должен выполняться

последовательно в направлении от старших

разрядов в сторону младших. Младшие

разряды сравниваются при условии

равенства старших. Тогда логика сравнения

на «больше» для двухразрядного слова

с учетом равенства/неравенства старшего

разряда может быть представлена в

следующем виде

![]() .

.

Аналогично можно записать логику сравнения для трехразрядного числа

![]()

и четырехразрядного числа

![]() .

.

В общем случае функция сравнения на «больше» для произвольного n-разрядного числа можно выразить

![]()

Подставив минтермы функций f(A>B)i в переменных ai и bi и эквивалентные функциям f(A=B)i элементы исключающее ИЛИ-НЕ, можно реализовать представленную ФАЛ для F(A>B).

Функцию сравнения на «меньше» можно определить как

![]() ,

,

т.е. только если будет отсутствовать факт равенства F(A=B)=0 и факт больше F(A>B)=0, то схемой совпадения нулей (функцией ИЛИ) установится общий ноль, а инверсия этого нуля даст единичное значение функции F(A<B) как последнего оставшегося варианта сравнения.

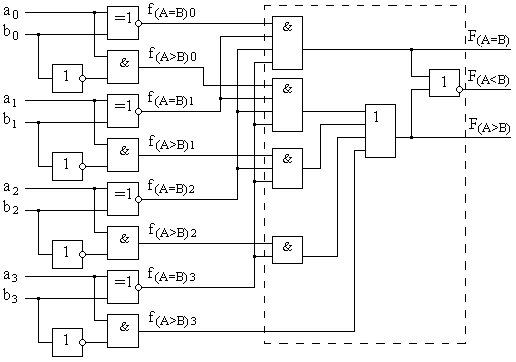

Пример схемы, реализующей рассмотренные выше функции F(A=B), F(A>B) и F(A<B) двух четырехразрядных чисел приведен на рис.8.23.

Рис.8.23. Функциональная схема компаратора, реализующего функции «равно», «больше», «меньше» двух четырехразрядных чисел.

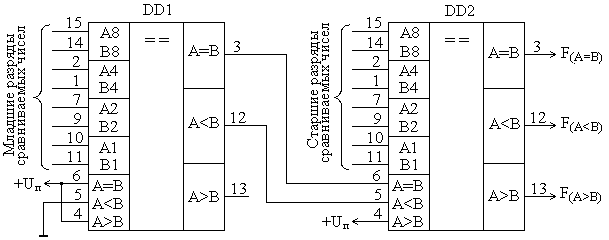

Из-за громоздкости структуры компараторов чисел большой разрядности и необходимости использования в этом случае логических элементов с большим количеством входов, в интегральном исполнении обычно реализуются компараторы, сравнивающие двоичные коды с разрядностью n не более 4 или 8 бит. Для повышения разрядности обрабатываемых кодов сравниваемые слова разбиваются на группы фиксированной разрядности с индивидуальными выходами функций сравнения на «равно» F(A=B)i и «больше» F(A>B)i в каждой группе. Тогда описанный выше метод применим и для анализа n-разрядных кодов. Для этого выходы функций равенства и больше компараторов отдельных групп объединяются в часть схемы рис.8.23, заключенную в пунктирную линию. В результате формируется результат сравнения кодов всей длины. В условном графическом обозначении функция компаратора задается символами «= =» или «COMP».

В качества примера можно привести микросхему четырехразрядного компаратора К561ИП2, реализующую функции сравнения на «больше», «меньше» и «равно». Эта микросхема может также применяться для сравнения кодов большей разрядности (рис.8.24). Для этого в ней предусмотрены входы переноса функций «меньше» и «равно», на которые подаются выходы одноименных функций группы младших разрядов. Вход «больше» в данной микросхеме избыточен, и на него в микросхемах всех групп необходимо постоянно подавать потенциал логической единицы. На вход «меньше» микросхемы самой младшей группы необходимо подать логический ноль, а на вход «равно» - логическую единицу. Такое же включение микросхемы должно быть и при использовании ее для сравнения четырехразрядных слов.

Рис.8.24. Включение микросхемы К561ИП2 при повышения разрядности сравниваемых слов.