- •Ответы к экзамену по курсу «Моделирование»

- •Общая методология моделирования. Принципы моделирования.

- •2.Категории языка gpss. Модельное время в gpss.

- •3.Операторы Generate и Terminate в gpss.

- •4. Равномерный, нормальный, биномиальный и пуассоновский законы распределения случайных величин.

- •5. Цепи текущих и будущих событий в gpss

- •7. Задание дискретных и непрерывных функций распределения в gpss.

- •8. Организация ветвлений в gpss.

- •17. Ансамбли и группы транзактов в gpss.

- •9.Стандартные числовые атрибуты.

- •10.Моделирование многоканальных устройств в gpss. Прерывание работы устройств в gpss

- •11. Приоритеты, недоступные состояния, проверка состояния в gpss.

- •12. Таблицы в gpss

- •13.Резидентное и транзитное время транзактов

- •14.Переменные, операции в gpss. Оператор Select.

- •15. Проверка числовых выражений в gpss. Изменение значений параметров в gpss.

- •16. Сохраняемые величины в gpss.

- •19.Составные части описания устройств в vhdl.

- •20. Типы данных в vhdl

- •21. Понятие сигнала в vhdl. Средство описания сигналов.

- •22.Операторы Process в vhdl.

- •24.Операторы if и Case.

- •25. Структурная и поведенческая модель в vhdl

- •27.Методы асинхронного и синхронного моделирования. Виды состязаний в цифровых схемах.

- •28.Методы выявления статических и динамических состязаний в цифровых схемах.

- •29.Основные понятия технической диагностики. Классы неисправностей цифровых схем.

- •30. Построение контролирующего теста. Метод тфн. Словарь неисправностей.

- •31. Построение контролирующего теста. D-алгоритм Рота.

- •32.Подходы, используемые при контроле последовательностных схем. Построение установочной последовательности.

- •33. Построение переводящей и диагностической последовательностей.

- •34. Построение контролирующего теста с использованием моделирования.

- •35. Самотестирующиеся схемы

22.Операторы Process в vhdl.

Оператор процесса

При описании несложных процессов моделирования можно ограничиться присваиванием значений физических сигналов. Однако при более сложном моделировании необходимо выполнить целую группу операторов. При этом выполнение этих операторов должно быть в рамках одного такта машинного времени, поэтому необходимо заключить в какую-то оболочку операторы, для которой необходимо заключить условия ее оптимизации. Всеми этими функциями управляет оператор процесса:

PROCESS (список чувствительности)

описание типов

описание констант

описание функций

описание процедур

BEGIN

<операторы>

ENDPROCESS

Внутри процесса нельзя описывать сигналы. Пример:

architecture DECODER.ARH of DECODER is

BEGIN

PROCESS (A, E)

VARIABLE V: BIT.VECTOR (0 to 3);

BEGIN

V(0):=not A(0) and not A(1) and E;

…

V(3):= A(0) and A(1) and E;

D<=V;

ENDPROCESS

END DECODER.ARH

24.Операторы if и Case.

Оператор условного перехода IF

IF <условие> Then <посл. оп-р 1>

Else < посл. оп-р 2>

ENDIF

В ряде случаев целесообразно использовать вложенные операторы:

If <условие 1> Then < посл. оп-р 1>

Elseif <условие 2> Then < посл. оп-р 2>

………………….

Elseif <условие n> Then < посл. оп-р n>

Endif

Последняя запись оператора IF может быть усилена, то есть после посл. оп-ра ELSEIF может быть поставлена конструкция ELSE <посл. услов.>, если не срабатывает ни одна из выше приведенных операций, то выполняется последовательность операторов записанных в Else. Пример:

Architecture DECODER.ARH of DECODER is

Begin

Process (A, E) – список чувствительности

Begin

If E=’0’ Then D<=”0000”;

Else if A=”00” Then D<=”0001”;

………………………………….

Else if A=”11” Then D<=”1000”;

Endif

End Process

End DECODER.ARH

Оператор CASE

В ряде случаев вместо операторов SELECT используется оператор CASE. Подобное использование разумно, если ключевое выражение состоит из одной переменной или сигнала. Данный подход всегда используется при моделировании автомата (управляющего устройства). Вводится переменная SOST (состояние) и по тому в какое состояние переходит автомат, реализуется операция.

CASE <ключевое выражение> is

When <вариант 1>=><имя сигнала 1><=<выражение 1>

When <вариант 2>=><имя сигнала 2><=<выражение 2>

When Other => <имя сигнала n><=<выражение n>

END CASE

Последовательно просматриваются строчки оператора на совпадение ключевого оператора и очередного варианта. При совпадении выполняется присваивание значению сигнала значение выбранной строки. Если не выполняется ни одно из условий, то выполняется Other. Пример:

Интерфейсный блок.

Architecture DECODER_ARH of DECODER is

Begin

Process (A, E)

Variable V: bit_vector (0 to 3);

Begin

Case A is

When “00”=> V := “0001”;

……………………

When “11”=> V := “1000”;

End Case

If E=’1’ Then D<=V

Else D<=”0000”

End if

End Process

End DECODER_ARH

25. Структурная и поведенческая модель в vhdl

Моделирование последовательных схем может проводится на 2-х уровнях:

На поведенческом уровне (с использованием операторов VHDL)

На структурном уровне, когда схема представляется как совокупность компонентов и связей между ними. При этом компоненты могут быть описаны как самим пользователем, так и взяты из библиотеки. Но в любом случае под компонентом понимается программа на VHDL.

Поведенческая модель

Моделирование RS триггера на поведенческом уровне:

ENTITY RS IS

PORT (SET, RESET: in bit;

d1,d2: out bit);

END RS

Architecture RS.ARX of RS IS

BEGIN

PROCESS (SET, RESET);

BEGIN

IF SET=’1’ and RESET=’0’ THEN d1<=’1’; d2<=’0’;

ELSIF SET=’0’ and RESET=’1’ THEN d1<=’0’; d2<=’1’;

ELSIF SET=’1’ and RESET=’1’ THEN <сообщение>;

ENDIF

ENDPROCESS

END RS.ARX

Язык VHDL позволяет задавать:

Задержки отдельных компонентов схемы

В поведенческой модели задержка может быть задана в любом операторе присвоения сигналов after <величина задержки> (целое число со своей аббревиатурой 20 нс)

Различают 2 вида задержек:

Транспортная задержка – это обычная задержка распространения сигнала по цепи.

Инерциальная. Как правило, связана с конкретной элементной базой.

Инерциальная задержка предполагает, что, если на вход элемента приходит импульс меньше задержки этого элемента, то он игнорируется, и элемент на него прореагировать не может. В VHDL предполагается по умолчанию инерциальная задержка. Если пользователь хочет испытать транспортную задержку, он должен указать это явно. Примеры:

y1 <= not (x1 and x2) after 20ns

y1 <= transport not (x1 and x2) after 20ns

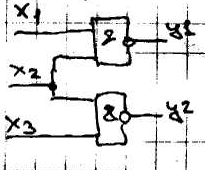

Структурная модель

Предполагает, что в явном или неявном виде пользователь даст описание компонентов структурной модели. Для описания компонент используются блоки:

COMPONENT <имя компонента>

GENERIS <список параметров>

PORT <описание входных и выходных цепей>

END COMPONENT

Конструкция GENERIS служит для передачи параметров в тело компонента. Это может быть время задержки компонентов, количество контактов и его мощность. Введение данной конструкции позволяет не меняя архитектурного тела наследовать поведение проектируемого устройства при разных задержках компонентов. Т.к. проектируемая схема представляет целую совокупность компонент, то все они должны быть описаны в архитектурном теле без конструкции BEGIN. Для создания полноценной схемы моделирования необходимо привязать интерфейсный блок любого элемента схемы с описанием портов компонента. Подобная привязка осуществляется с использованием описания порта в следующем виде:

P ort

map (список входов/выходов)

ort

map (список входов/выходов)

Entity Sx1 is

port (x1,x2,x3: in bit

y1,y2 : out bit);

end Sx1

architecture SX1.ARX of Sx1 is

COMPONENT AND2

port (a,b: in bit; c: out bit);

end AND2

BEGIN

A1:AND2

port map (x1, x2, y1)

A2:AND2

port map (x2, x3, y2)

END SX1.ARH

В ряде случаев данное позиционное описание компонентов может быть заменено явным описанием входов/выходов.

A1:AND2

port map (a=>x1,b=> x2,c=> y1)

A2:AND2

Port map (a=>x2, b=>x3, c=>y2)

END SX1.ARH

Данный подход, связанный с описанием компонентов является достаточно громоздким. Предпочтительно использовать стандартные библиотеки. Для работы с ней необходимо в 1-ой и 2-ой строчках программы дать ссылку на эту библиотеку.

LIBRARY ieee;

USE ieee.std_logic.all;

Данная конструкция позволяет подключать полную библиотеку. Однако, возможно подключить только часть:

USE ieee.std_logic.arith.’+’

В этом случае подключается библиотека с арифметическими компонентами, а именно +. Использование библиотеки преследует цель:

- удобство для пользователя

- адекватность моделирования

Т.к. реальные схемы при работе с шинными компонентами АЦ и ЦА сигналами, возникает ситуация, когда в одной точке сходится несколько сигналов различной мощности. В этом случае моделирование проводится в рамках 9-тизначного алфавита. Алфавит включает:

U – неинициализированное значение

X – неопределенное значение

W – слабая неопределенность

0 – сильный 0

L - слабый 0

1 – сильна 1

H – слабая 1

Z - импеданс

~ - безразличное значение

Расширение структурной модели

В приведенном примере модель мультиплексора:

entity MUX IS

port (x: in bit.vector (1 to 4);

A: in bit.vector (1 to 2);

y: out bit);

end MUX

интерфейсное тело одинаково, как и для поведенческой, так и для структурной модели.

architecture MUX_ARX of MUX is

signal ma: bit.vector (1 to 2)

signal my: bit.vector (1 to 4)

begin

C1:AND3

port map (x(1), ma(1), ma(2), my(1));

C2:AND3

port map (x(2), ma(1), A(2), my(2));

…

END MUX_ARX

Для выполнения моделирования необходимо описать функции, которые реализуются компонентами. Данное описание всегда следует после конструкции архитектуры и до описания сигналов.

COMPONENT AND3

port (a,b,c: in bit; z: out bit);

end AND3

Расшифровка осуществляется в полном соответствии с нотацией VHDL и состоит из архитектурного и интерфейсного тел.

entity AND3 is

port (a,b,c: in bit; z: out bit);

end AND3

architecture AND3.ARX of AND3 is

begin

process (a,b,c)

begin

z<= a and b and c;

end process

end AND3.ARX

Аналогично описание для OR4 и инверторов. На практике для описания структурных схем обычно используем библиотеки компонентов. В этом случае пользователь рисует на экране структурную схему (см. выше) и запускает описание на трансляцию. Компилятор выбирает из библиотеки соответствующее описание на VHDL и автоматически формирует общую структуру схемы на VHDL. Как правило, библиотеки создаются по иерархическому принципу (в соответствии архитектурной схеме однократно ставится УГО). В современных системах уровень иерархии не ограничен.