- •ОрГэвм - Ответственные

- •1. Развитие и классификация однопроцессорных архитектур компьютеров.

- •2.Конвейерная обработка команд

- •3. Cуперскалярная обработка команд.

- •4. Классификация архитектуры sisd

- •5. Cisc и risc-архитектуры микропроцессоров.

- •6. Vliw-архитектура компьютера и epic-концепция.

- •Vliw-архитектура

- •7. Simd-архитектура. Способы её реализации.

- •8. Многоядерные структуры процессора и многопотоковая обработка команд.

- •9. Технические и эксплуатационные характеристики эвм Производительность компьютера

- •Энергоэффективность процессора

- •10.Энергоэффективность процессора.

- •11. Классификация эвм по назначению и функциональным возможностям.

- •12. Функциональные возможности, пути развития, современные разработки супер эвм и мэйнфреймов

- •Особенности и характеристики современных мэйнфреймов

- •13.Назначение, классификация, структурная организация серверов. Серверы

- •Блейд-серверы

- •14.Классификация, структурная организация персональных компьютеров.

- •15.Функциональные возможности, назначение, платформы рабочих станций.

- •16.Типы данных интеловских процессоров.

- •Данные типа указатель

- •Теги и дескрипторы.

- •17. Структура и форматы команд эвм

- •18.Способы адресации информации в эвм.

- •Базирование способом суммирования:

- •Относительная адресация с совмещением составляющих aи:

- •Индексная адресация

- •Стековая адресация:

- •19.Принципы организации системы прерывания программ.

- •21.Стратегия развития процессоров Intel.

- •22.Особенности процессорной микроархитектуры Intel Core.

- •23.Микроархитектура Intel Nehalem. Микроархитектура Intel Nehalem

- •Усовершенствования вычислительного ядра

- •Новая структура кэш-памяти

- •Реализация многопоточности

- •Интегрированный в процессор контроллер памяти

- •Новая процессорная шина qpi

- •Модульная структура процессора

- •Управление питанием и Turbo-режим

- •Технология Turbo Boost

- •Процессоры Nehalem

- •Технология txt – (Trusted Execution Technology, ранее известная как LaGrande) – защищает информацию, хранящуюся в виртуальных вычислительных средах.

- •24.Семейство процессоров Intel Westmere.

- •25. Иерархическая структура памяти эвм.

- •26.Способы организации кэш-памяти.

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •27.Принципы организации оперативной памяти.

- •28.Методы повышения пропускной способности оп. Методы повышения пропускной способности оп

- •29. Методы управления памятью

- •30.Организация виртуальной памяти.

- •31.Общая характеристика и классификация интерфейсов эвм.

- •32.Способы организации передачи данных.

- •Программно-управляемая передача данных

- •Передача по запросу прерывания от пу

- •Прямой доступ к памяти (пдп)

- •33. Системная организация компьютеров на базе современных чипсетов

- •34.Архитектуры вычислительных систем. Сильносвязанные и слабосвязанные многопроцессорные системы. Архитектуры вычислительных систем

- •Сильносвязанные многопроцессорные системы

- •Архитектура smp

- •Слабосвязанные многопроцессорные системы

17. Структура и форматы команд эвм

Все возможные преобразования дискретной информации могут быть сведены к четырем основным видам:

передача информации в пространстве (из одного блока ЭВМ в другой);

передача информации во времени (хранение);

логические (поразрядные) операции;

арифметические операции.

Обработка информации (решение задач) в ЭВМ осуществляется автоматически путем программного управления. Программа представляет собой алгоритм обработки информации (решение задачи), записанный в виде последовательности команд.

По характеру выполняемых операций различают следующие основные группы команд:

а) команды арифметических операций над числами с фиксированной и плавающей точками;

б) команды десятичной арифметики;

в) команды логических операций и сдвигов;

г) команды передачи кодов;

д) команды операций ввода-вывода;

е) команды передачи управления;

ж) команды векторной обработки;

з) команды задания режима работы машины и др.

Команда в общем случае состоит из операционной и адресной частей.

В свою очередь, эти части, что особенно характерно для адресной части, могут состоять из нескольких полей.

Операционная часть содержит код операции, который задает вид операции (сложение, умножение и др.). Адресная часть содержит информацию об адресах операндов и результате операции.

Структура команды определяется составом, назначением и расположением полей в команде.

Форматом команды называют ее структуру с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием числа бит в определенных полях.

18.Способы адресации информации в эвм.

Принципы поиска операндов в памяти

Ассоциативный поиск операнда предполагает просмотр содержимого всех ячеек памяти для выявления кодов, содержащих заданный командой ассоциативный признак (тег).

Эти коды и выбираются из памяти в качестве искомых операндов.

Применяется из кэш-памяти.

Адресный поиск операнда предполагает, что искомый операнд извлекается из ячейки, номер которой формируется на основе информации в адресном поле команды.

Далее рассматривается ТОЛЬКО адресный поиск операнда:

АК – адресный код, информация об адресе операнда, содержащаяся в команде

АИ – адресный исполнительный адрес, номер ячейки памяти к которой производится фактическое обращение.

Абсолютные способы, предполагают, что операнд или адрес его ячейки памяти (Аи – исполнительный адрес операнда) может быть получен напрямую из адресного поля команды, или косвенно из другой ячейки памяти, без каких-либо преобразований.

Непосредственная адресация операнда:

Операнд располагается в адресном поле команды и выбирается вместе с командой. Обращения к регистровой или оперативной памяти не производится.

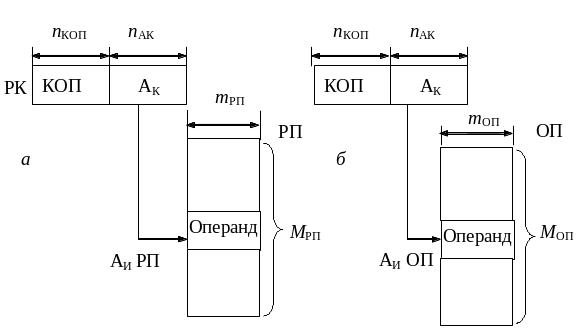

Прямая адресация операндов:

Операнд может находиться в РП или в ОП, адресация происходит с помощью адресного кода (Ак) в поле адреса команды, который равен исполнительному адресу. (Ак = Аи)

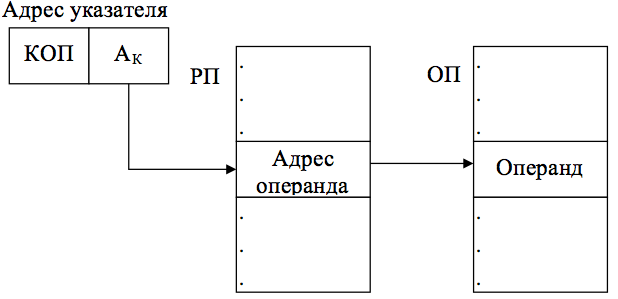

Косвенная адресация операндов:

Операнд находится в ОП. Адресация происходит с помощью адреса команды, по которому мы получаем исполнительный адрес из РП, уже по которому мы выберем операнд из ОП.

Относительные способы формирования исполнительных адресов ячеек памяти.

Данные способы формирования АИ предполагают, что двоичный код адреса ячейки образуется из нескольких составляющих:

Б – код базы

И – код индекса

С – код смещения

Которые используются в сочетаниях (Б и С), (И и С), (Б, И и С).

При относительной адресации применяются два способа вычисления адреса АИ:

Суммирование кодов составляющих адреса

Совмещение (конкатенация) кодов составляющих адреса

Суммирование кодов составляющих производится для случаев:

АИ = Б + С

АИ = И + С

АИ = Б + И + С