- •1. Основные понятия и задачи микроэлектроники.

- •2. Интегральные микросхемы. Классификация и маркировка.

- •4. Аналоговые интегральные микросхемы. Классификация, применение.

- •5. Операционные усилители, схемы на основе операционных усилителей.

- •6.Схемы на основе операционных усилителей:

- •7. Интегратор тока.

- •8.Стабилизатор напряжения.

- •9.Система термостабилизации.

- •11. Цифроаналоговые преобразователи.

- •12. Аналого-цифровые и преобразователи

- •13. Цифровые интегральные микросхемы.

- •14. Электронные ключи.

- •16. Логические элементы ттл и ттлш

- •17. Логические элементы эсл

- •19. Шифраторы.

- •20. Дешифраторы (декодеры, dc).

- •21.Сумматоры

- •22. Триггеры.

- •26. Счётчики импульсов.

- •27. Регистры.

- •28. Цифровые запоминающие устройства

- •29. Оперативные запоминающие устройства (озу, ram).

- •30.Пзу и рпзу

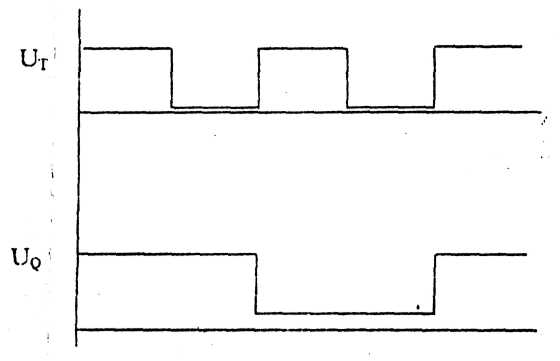

19. Шифраторы.

Комбинационные цифровые устройства.

Комбинационными называются такие логические устройства, выходные сигналы которых однозначно определяются входными сигналами (в отличие от последовательностных, состояние которых зависит от предыстории их работы).

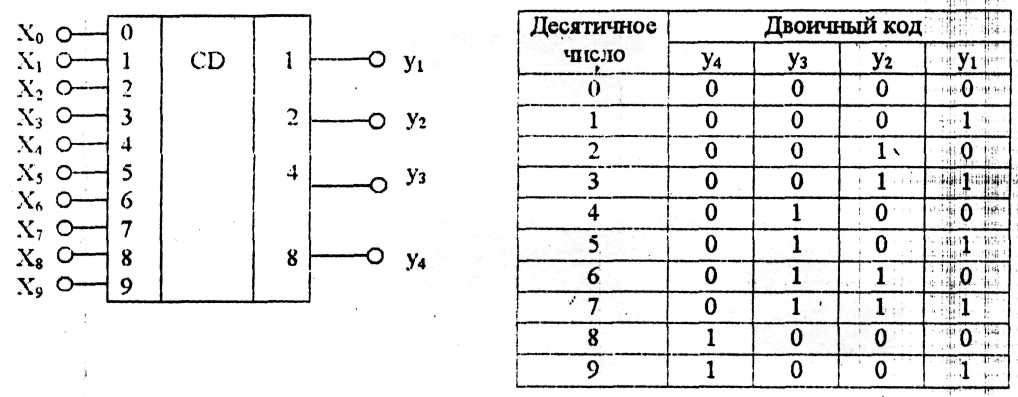

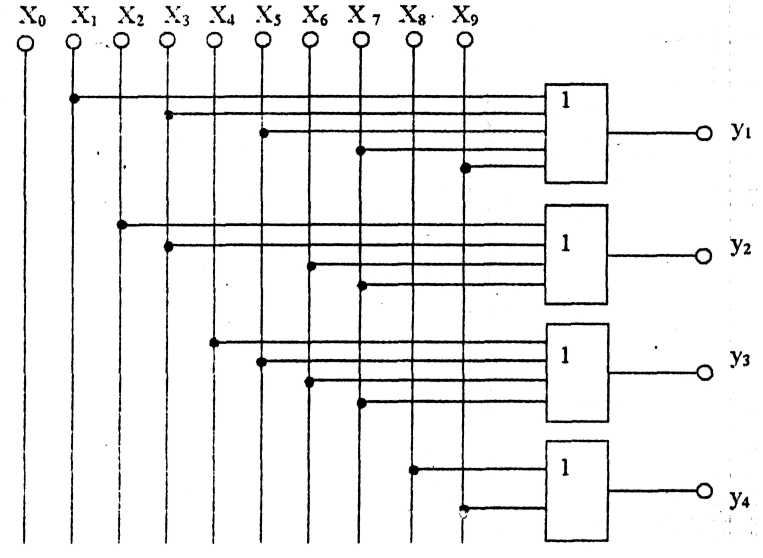

Шифраторы (кодеры, CD).

Устройство, преобразующее десятичные числа в двоичную систему счисления. Рассмотрим на примере шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. Условное обозначение такого шифратора и таблица соответствия выглядит следующим образом:

Основное назначение такого шифратора - преобразование номера источника сигнала например, номера нажатой кнопки клавиатуры в двоичный код.

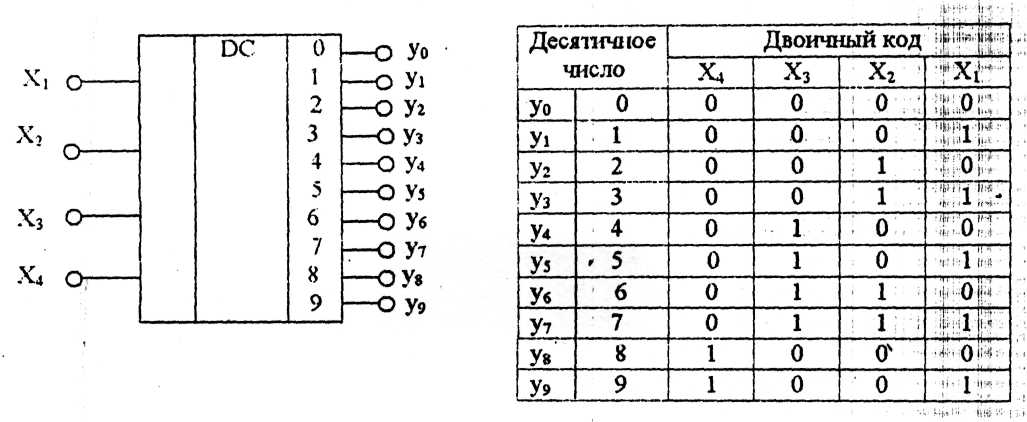

20. Дешифраторы (декодеры, dc).

Устройства, преобразующие двоичный код в соответствующее десятичное число (логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду). Условное обозначение и таблица соответствия выглядит следующим образом:

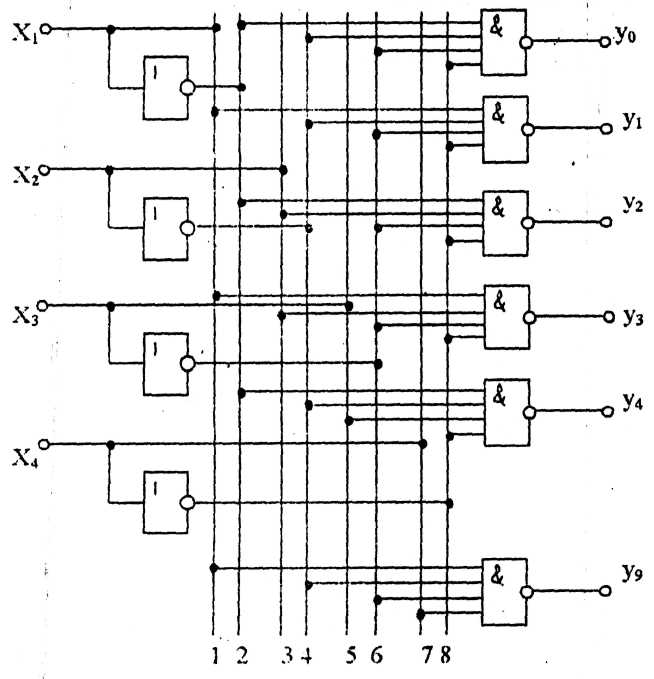

В таблице соответствия указаны десятичные числа, соответствующие поступившему на вход (Xi - Х4) двоичному коду и выходы (y1 - у9) на которых в этом случае появляется нужный сигнал. Такой дешифратор возможно построить, используя элементы И-НЕ и ИЛИ-НЕ.

21.Сумматоры

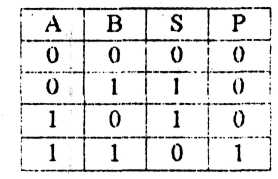

Устройства, предназначенные для сложения чисел. В простейшем случае рассматривается сложение двух одноразрядных двоичных чисел А и В. Таблица истинности (сложения выглядит в этом случае следующим образом:

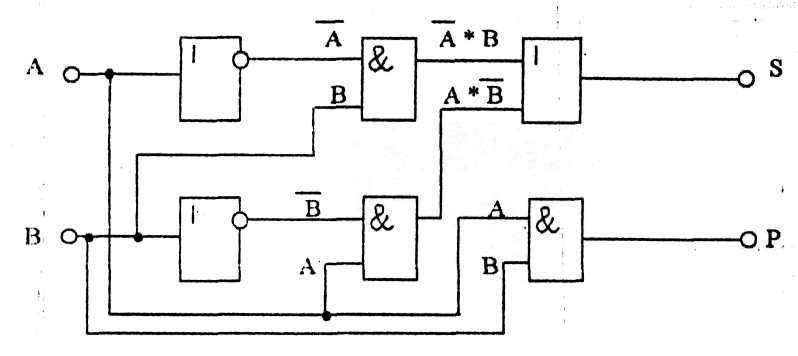

Например, в младшем разряде 0+0=0, 1+0=1,0+1=1,1+1=2 0 в двоичном коде, в младшем разряде 0, перенос 1 в старший разряд). Аналогично в следующем разряде - 0+0=0, 2+0=2 (1 Р),; 0+2=2 (1 0), 2+2=4 (1 0 0) и Т.Л. Как видно из таблицы, S * А*В + А*В , Р = А ♦ В . Устройство, реализующее такую логическую функцию, может быть построено следующим образом

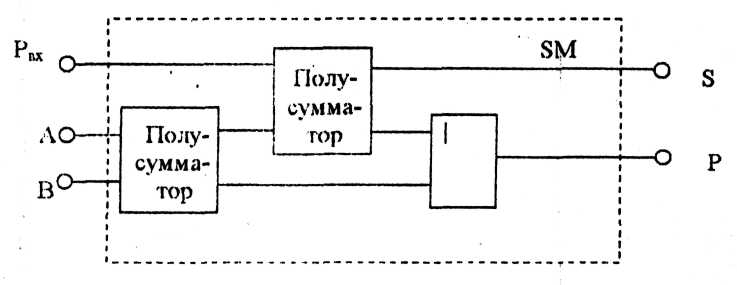

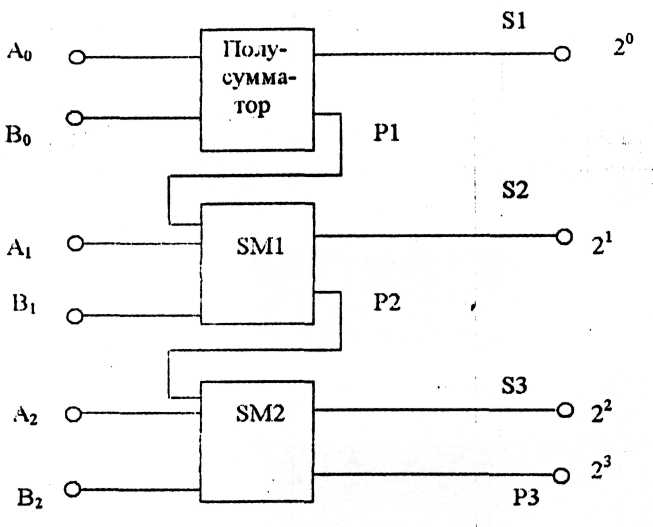

Устройство имеет только два входа, поэтому может использоваться только в младшем разряде (не имеет входа переноса из предыдущего разряда). Обычно называется полусумматором. При суммировании многоразрядных чисел для каждого разряда (кроме младшего) необходимо иметь устройство, имеющее дополнительный вход, на который подаётся сигнал переноса младшего (предыдущего) разряда. Такое устройство (полный сумматор SM) можно собрать из двух полусумматоров:

Соединяя между собой полусумматоры и полные сумматоры, получают устройство для сложения многоразрядных двоичных чисел:

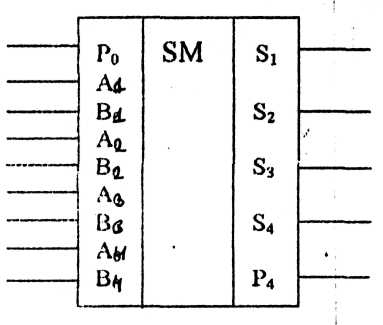

Сумматоры выпускаются в виде микросхем. Микросхема К155ИМЗ является сумматором для сложения четырехразрядных двоичных чисел.

Для наращивания разрядности суммируемых чисел микросхемы соединяют последовательно, для чего выход переноса микросхемы младших разрядов соединяют с входом переноса микросхемы старших. У микросхемы, суммирующей младшие разряды, вход переноса «зануляют».

22. Триггеры.

Последовательностные цифровые устройства.

Последовательностными называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти. К таким устройствам относятся триггеры, счётчики импульсов, регистры.

Триггеры.

Триггер - простейшее Последовательностное устройство, которое может длительно находится в одном из двух возможных устойчивых состояний и переходить из одного в -другое под воздействием входных сигналов. Применяются в качестве элементов памяти, системах задержки, счётных устройствах. Является базовым элементом цифровой техники.

Триггеры подразделяются на асинхронные и синхронные (тактируемые). Состояние асинхронных триггеров изменяется при поступлении сигналов на информационные входы. В синхронном триггере имеется тактовый вход, состояние такого триггера может измениться только после появления на этом входе тактирующего импульса. По функциональным возможностям триггеры подразделяются на классы и обозначаются RS, RST,JK,D,T

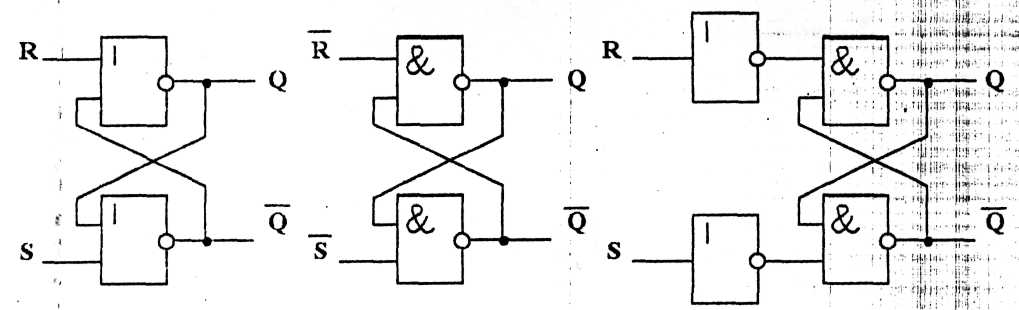

Асинхронный триггер, имеющий только два входа и два (или один) выхода.

Простейший RS - триггер состоит из двух элементов ИЛИ - НЕ или И - НЕ, охваченных обратной связью. Условное обозначение RS ~ триггера:

![]()

Проанализируем работу триггера, состоящего из элементов ИЛИ - НЕ. Пусть на_вход S (Set - установка) подан сигнал 1, а на вход R (Reset - сброс) - 0. Тогда на выходе! Q т 0, а на Q - 1. Изменению сигнала на входе S теперь не приведёт к изменению сигнала на выходе (память), для изменения состояния триггера необходимо подать <<1» на вход R при нуле ном сигнале ни S. Аналогично работает триггер из двух элементов И - НЕ, однако изменение состояния проиходится сигналом «О».

RST-триггер.

Синхронный триггер имеет дополнительный вход С (clock - фиксация времени) для подачи синхронизирующих импульсов. Получается добавлением к RS триггеру двух логических элементов И или И - НЕ.

![]()

![]()

Входные сигналы «1» проходят через элементы И и И - НЕ только в те моменты времени когда на вход «С» поступают синхронизирующие импульсы, то есть моменты смены'' состояния задаются синхронизирующими импульсами. Условное обозначение RST триггера:

![]()

Рассмотренный триггер имеет прямой статический вход синхронизации, то есть его состояние меняется при подаче на вход «С» логической единицы. Существует статические триггеры с инверсным входом (реагирующие на «О»), а так же динамические триггеры, изменяющие свое состояние при перепаде (изменении) сигнала на входе «С» от О к 1 (прямой динамический вход С, обозначается / ), или от 1 к 0 (обратный динамический вход С, обозначается \ ).

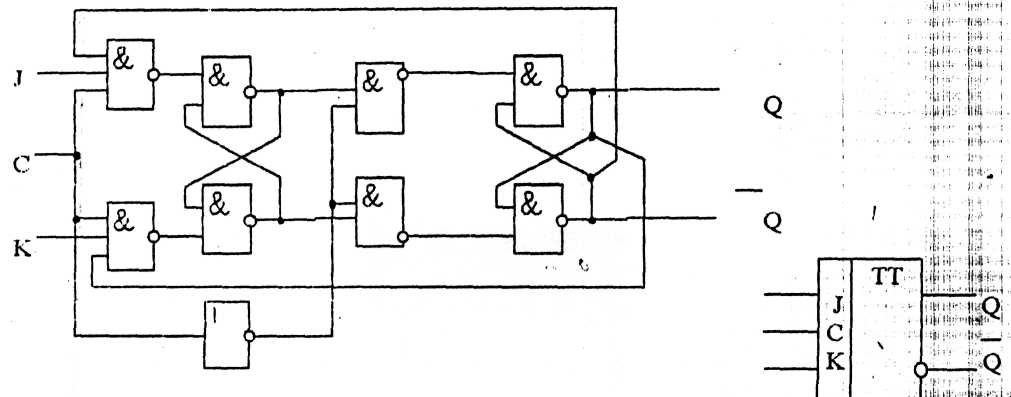

23. JK – триггер

Синхронный триггер JK, при появлении логических единиц на обоих информационных входах (J и К) которого происходит изменение состояния. Состоит из двух RS триггеров, соединённых по схеме ведущий - ведомый. На входе триггера включены трехвходовые элементы И - НЕ

Таблица истинности JK триггера аналогична таблице истинности RS триггера, но не имеет определенных состояний. JK триггер может снабжаться дополнительными входами, которые служат для установки его в состояние «О» или «1» независимо, от сигналов на информационных входах.

24.D-триггер.

Синхронный триггер, имеет только один информационный вход D. Предназначен для запоминания (задерживания - delay - задержка) логического сигнала, своё состояние меняет только при поступлении синхронизирующего импульса. Может быть построен из синхронного RST триггера и логического элемента НЕ.;

![]()

Обозначение![]()

25. Т-триггер.

Счётный триггер. Меняет своё состояние на противоположное при поступлении каждого синхронизирующего импульса. В качестве Т триггера используется JK триггер, на информационные входы которого подаются логические сигналы J=K=1. Как видно из структуры JK триггера, в этом случае синхронизирующий импульс пройдёт через тот входной элемент ЗИ-НЕ, на который подаётся сигнал «1» с выхода триггера, что приведёт к изменению этого сигнала на противоположный. Обозначение Т- триггера:

![]()

Т триггер применяется в качестве элемента счётчика импульсов и в качестве делителя частоты. Поскольку сигнал на выходе триггера меняется на противоположный при поступлении «1» на вход, частота на выходе триггера в два раза меньше, чем на входе.