Лабораторная работа 2 / reportLab2

.docМинистерство образования РФ

Санкт-Петербургский государственный

Электротехнический университет «ЛЭТИ»

Кафедра ВТ

Отчет

по лабораторной работе N2

по Языкам проектирования аппаратуры

Вариант 3

Выполнил: Гладилин Г.А.

Группа: 3371

Проверил: Мурсаев А. Х.

Санкт-Петербург

2007

Цель работы: изучение правил описания модулей, предназначенных для объединения их в произвольные структуры, а также правил и способов их объединения.

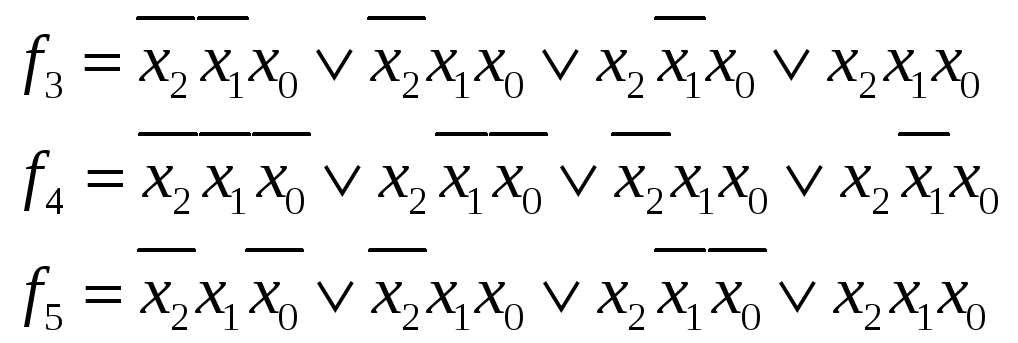

Задание: необходимо добавить в программу фрагменты, связанные с объявлением и конфигурацией компонентов OR. Необходимо ввести в программу описание включения элементов OR так, чтобы воспроизводились три функции из следующей таблицы (соответствующие вариантам 3,4,5):

|

Входной код |

Числовой эквивалент |

f3 |

f4 |

f5 |

|

000 |

0 |

0 |

1 |

0 |

|

001 |

1 |

1 |

0 |

1 |

|

010 |

2 |

0 |

0 |

0 |

|

011 |

3 |

1 |

1 |

0 |

|

100 |

4 |

0 |

1 |

1 |

|

101 |

5 |

1 |

1 |

1 |

|

110 |

6 |

0 |

0 |

0 |

|

111 |

7 |

1 |

0 |

1 |

Порядок выполнения работы.

В работе предполагается проектирование устройства, реализующего семейство логических функций одних и тех же переменных в соответствии со структурой, приведенной на рис. 1. Здесь дешифратор DC реализует все полные конъюнкции заданного числа переменных, а выходные функции воспроизводятся объединением по логике ИЛИ выходов дешифратора, на которых единица вырабатывается на кодах, которым соответствует единичное значение данной функции.

|

|

|

Исходный код:

COMP2_L2.VHD

library ieee;

use IEEE.std_logic_1164.all;

use work.util_1164.all;

entity decod is

generic( num_outputs: integer; delay:time);

port( input:in integer range 0 to num_outputs-1;

output: out std_logic_vector ( 0 to num_outputs-1));

end decod;

architecture behave of decod is

begin process(input)

begin

for i in 0 to num_outputs-1 loop

if (i=input) then output(i)<= '1' after delay;

else output(i)<='0' after delay;

end if;

end loop;

end process;

end behave;

library ieee;

use IEEE.std_logic_1164.all;

use work.util_1164.all;

entity or4 is

port ( in1,in2,in3,in4 :in std_logic; -- in

hit:out std_logic); -- out

end or4;

architecture behave of or4 is

begin

process (in1,in2,in3,in4)

begin

hit<=in1 or in2 or in3 or in4;

end process;

end behave;

library ieee;

use IEEE.std_logic_1164.all;

use work.util_1164.all;

entity zero is

port (n: out std_logic);

END zero;

architecture behave of zero is

begin

n<='0';

end behave;

LABA2.VHD

library work;

library ieee;

use ieee.std_logic_1164.all;

use work.util_1164.all;

entity laba2 is

port (input: in integer range 0 to 7;

z1, z2, z3: out std_logic);

end laba2;

architecture arc01 of laba2 is

constant num_terms: integer := 8;

component decod --import decodera

generic(num_outputs: integer; delay: time);

port(input: in integer range 0 to num_terms-1;

output: out std_logic_vector (0 to num_terms-1));

end component;

for all:decod use entity work.decod(behave);

component or4 --takim je makarom mi importiruem ILI-element

port (in1,in2,in3,in4 :in std_logic; hit:out std_logic);

end component;

for all:or4 use entity work.or4(behave);

signal y: std_logic_vector (0 to num_terms-1);

signal zero: std_logic := '0';

begin

u1: decod

generic map(num_terms, 5 ns)

port map(input,y);

u2: or4

port map(y(1),y(3),y(5),y(7),z1);

u3: or4

port map(y(0),y(3),y(5),y(4),z2);

u4: or4

port map(y(1),y(4),y(5),y(7),z3);

end arc01;

TESTLAB2.VHD

LIBRARY ieee;

LIBRARY work;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY tlab2 IS

END tlab2;

ARCHITECTURE test OF tlab2 IS

SIGNAL stim_integer: integer:=0;

SIGNAL y0,y1,y2:std_logic;

component laba2

port (input: in integer range 0 to 7; -- in

z1, z2, z3: out std_logic); -- out

end component;

-- for all:laba2 use entity work.laba2(arc01);

BEGIN

u1: laba2

port map(stim_integer,y0,y1,y2);

stimulator:

PROCESS BEGIN

for i in 0 to 7 loop

stim_integer <=i;

Wait for 50 ns;

end LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note; --failure

WAIT;

END PROCESS;

END test;

Временная диаграмма