Лабораторная работа 3 / reportLab3

.docМинистерство образования РФ

Санкт-Петербургский государственный

Электротехнический университет «ЛЭТИ»

Кафедра ВТ

Отчет

по лабораторной работе N3

по Языкам проектирования аппаратуры

Вариант 3

Выполнил: Гладилин Г.А.

Группа: 3371

Проверил: Мурсаев А. Х.

Санкт-Петербург

2007

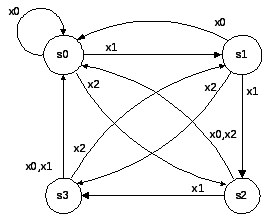

Задание: описать в языке VHDL и выполнить моделирование автомата Мили, заданного таблицей переходов и выходов в соответствии с таблицей.

Исходноесостояние и вход |

состояние перехода и выход автомата Мили |

||

|

3 |

|||

|

S(t) |

x(t) |

S(t+1) |

y(t+1) |

|

S0 |

x0 |

S0 |

Y0 |

|

S0 |

x1 |

S1 |

Y1 |

|

S0 |

x2 |

S2 |

Y1 |

|

S0 |

x3 |

- |

- |

|

S1 |

x0 |

S0 |

Y0 |

|

S1 |

x1 |

S2 |

Y1 |

|

S1 |

x2 |

S3 |

Y0 |

|

S1 |

x3 |

- |

- |

|

S2 |

x0 |

S0 |

Y0 |

|

S2 |

x1 |

S3 |

Y1 |

|

S2 |

x2 |

S0 |

Y0 |

|

S2 |

x3 |

- |

- |

|

S3 |

x0 |

S0 |

Y0 |

|

S3 |

x1 |

S0 |

Y1 |

|

S3 |

x2 |

S1 |

Y1 |

|

S3 |

x3 |

- |

- |

|

|

x0 |

x1 |

x2 |

x3 |

|

s0 |

s0 |

s1 |

s2 |

-- |

|

s1 |

s0 |

s2 |

s3 |

-- |

|

s2 |

s0 |

s3 |

s0 |

-- |

|

s3 |

s0 |

s0 |

s1 |

-- |

|

|

x0 |

x1 |

x2 |

x3 |

|

s0 |

y0 |

y1 |

y1 |

-- |

|

s1 |

y0 |

y1 |

y0 |

-- |

|

s2 |

y0 |

y1 |

Y0 |

-- |

|

s3 |

y0 |

y1 |

y1 |

-- |

Исходный код:

st_mash.vhd

LIBRARY ieee;

LIBRARY work;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

use work.p_l3.all;

ENTITY lab3 IS

port( x:in st_m_in; y:out st_m_out);

END lab3;

ARCHITECTURE st_mash OF lab3 IS

SIGNAL s: state;

BEGIN process

variable i:integer;

begin

s<=S0;

loop

wait until (p_clk='1' and not p_clk'stable);

-----------------changing states-----------------------------------------

case S is

when S0 => if (x=x0) then s<=s0;

elsif (x=x1) then s<=S1;

else s<=S2;

end if;

when S1 => if x=x0 then s<=S0;

elsif x=x1 then s<=S2;

else s<=S3;

end if;

when S2 => if (x=x0) or (x=x2) then s<=S0;

else s<=S3;

end if;

when S3 => if (x=x0) or (x=x1) then s<=S0;

else s<=S1;

end if;

end case;

-----------------form output--------------------------------------------

if (x=x0) then y<=y0;

elsif (x=x1) then y<=y1;

elsif ((s=s0) or (s=s3)) then y<=y1;

else y<=y0; end if;

end loop;

end process;

end st_mash;

p_l3.vhd

library IEEE;

USE ieee.std_logic_1164.ALL;

use work.util_1164.all;

PACKAGE p_l3 IS

FUNCTION buffer_inv(input:std_logic_vector;en:std_logic )

RETURN std_logic_vector;

signal p_clk:std_logic;

type state is (s0,s1,s2,s3);--,s3,s4,s5,s6,s7);

type st_m_out is (y0,y1); --,y2,y3);

type st_m_in is (x0,x1,x2,x3);

Function input_to_vector( inp:st_m_in;k:integer) return std_logic_vector;

Function output_to_vector( y:st_m_out;k:integer) return std_logic_vector;

END p_l3;

PACKAGE BODY p_l3 IS

FUNCTION buffer_inv(input:std_logic_vector;en:std_logic) return std_logic_vector IS

VARIABLE result:std_logic_vector(input'range);

BEGIN

FOR i IN input'RANGE LOOP

if en='1'then

IF input(i) = '1' THEN

result(i) := '0';

ELSE

result(i) := '1';

END IF;

else result(i):='Z';

end if;

END LOOP;

RETURN result;

END buffer_inv;

Function input_to_vector( inp:st_m_in;k:integer) return std_logic_vector IS

variable i,j:integer;

begin

i:=0;

for l in st_m_in loop

if inp=l then j:=i; end if;

i:=i+1;

end loop;

return to_vector(j,k);

end input_to_vector;

Function output_to_vector(y :st_m_out;k:integer) return std_logic_vector IS

variable i,j:integer;

begin

j:=0;

for l in st_m_out loop

if y=l then j:=i; end if;

i:=i+1;

end loop;

return to_vector(j,k);

end output_to_vector;

END p_l3;

tb_l3.vhd

LIBRARY ieee;

LIBRARY work;

USE ieee.std_logic_1164.ALL;

USE work.p_l3.ALL;

USE STD.textio.ALL;

ENTITY tb_l3 IS

END tb_l3;

ARCHITECTURE test OF tb_l3 IS

CONSTANT clk_start : time := 50 ns;

CONSTANT clk_period : time := 50 ns;

CONSTANT continue_time : time := 100 ns;

CONSTANT Width_i: integer:= 2 ;-- assign your value

constant width_o: integer:= 2 ;-- assign your value

COMPONENT lab3

port( x:in st_m_in; y:out st_m_out);

end COMPONENT;

FOR ALL:lab3 USE ENTITY WORK.lab3(st_mash);

SIGNAL aut_stim: st_m_in ;

SIGNAL aut_out: st_m_out ;

SIGNAL inp_code: std_logic_vector(width_i-1 DOWNTO 0);

signal out_code: std_logic_vector(width_o-1 DOWNTO 0);

signal done:boolean;

BEGIN

u1: lab3

PORT MAP(aut_stim,aut_out);

-- clk <= p_clk;

stimulator:

PROCESS

VARIABLE i : integer;

BEGIN

for i in 0 to 16 loop -- assign your number of test steps

wait until (p_clk='0'and not p_clk'stable);

case i is

when 0 | 6 | 8| 16 => aut_stim <= x0;

when 1 | 2 | 3 | 4 | 5 | 9 | 12| 14 => aut_stim <= x1;

when 7 | 10| 11| 13| 15 => aut_stim <= x2;

end case;

end loop;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

done <= true;

WAIT;

END PROCESS;

clock:

PROCESS

BEGIN

p_clk <= '0';

WAIT for clk_start;

WHILE not done loop

p_clk <= '1';

WAIT for clk_period/2;

p_clk <= '0';

WAIT for clk_period/2;

END LOOP;

END PROCESS;

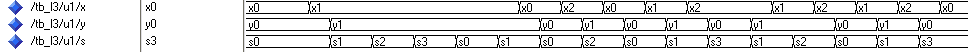

Тест: X0 X1 X1 X1 X1 X1 X0 X2 X0 X1 X2 X2 X1 X2 X1 X2 X0

S: S0 S0 S1 S2 S3 S0 S1 S0 S2 S0 S1 S3 S1 S2 S0 S1 S3 S0

Y: Y0 Y1 Y1 Y1 Y1 Y1 Y0 Y1 Y0 Y1 Y0 Y1 Y1 Y0 Y1 Y0 Y0

Временная диаграмма