Лабораторная работа 5 / reportLab5

.docМинистерство образования РФ

Санкт-Петербургский государственный

Электротехнический университет «ЛЭТИ»

Кафедра ВТ

Отчет

по лабораторной работе N5

по Языкам проектирования аппаратуры

Вариант 3

Выполнил: Гладилин Г.А.

Группа: 3371

Проверил: Мурсаев А. Х.

Санкт-Петербург

2007

Целью проекта является изучение процесса реализации проекта в ПЛИС по исходному описанию на языке VHDL . Реализации подлежит комбинационная логическая схема, после отладки проект может быть загружен в ПЛИС учебного стенда. При создании проекта используется САПР QuartusII фирмы Altera.

PART1

-

Открыть пакет Quartus II 6.0.

-

Установить вид меню (рекомендуется MAX+PLUSII: Tools/ Customize-выбор, но по желанию можно использовать «стандартный» вид QuartusII).

-

В текстовом редакторе создать описание схемы в соответствии с индивидуальным заданием (см. раздел II). Имя файла вершины проекта должно совпадать с именем ENTITY.

LAB5.VHDL

entity TranScriber is

port (

inBinary: in bit_vector(3 downto 0);

outHamming: out bit_vector(2 downto 0);

inEN: in bit

);

end Transcriber;

-------------------------------------------------------------

architecture Behave of TranScriber is

begin

process (inEN,inBinary)

begin

if inEN = '1' then

case inBinary is

when "0000"=>outHamming <= "000";

when "0001"=>outHamming <= "011";

when "0010"=>outHamming <= "110";

when "0011"=>outHamming <= "101";

when "0100"=>outHamming <= "111";

when "0101"=>outHamming <= "100";

when "0110"=>outHamming <= "001";

when "0111"=>outHamming <= "010";

when "1000"=>outHamming <= "101";

when "1001"=>outHamming <= "110";

when "1010"=>outHamming <= "011";

when "1011"=>outHamming <= "000";

when "1100"=>outHamming <= "010";

when "1101"=>outHamming <= "001";

when "1110"=>outHamming <= "100";

when "1111"=>outHamming <= "111";

end case;

else outHamming <= "000"; end if;

end process;

end Behave;

-

Сохранить файл в директории, где будет отлаживаться проект – File/ Save.

-

Создать новый проект – File/ New Project Wizard, его месторасположение тот директорий, где сохранен исходный файл.

-

Выполнить «условную» компиляцию проекта (Processing/ Analyze Current File) Устранить возможные ошибки описания.

-

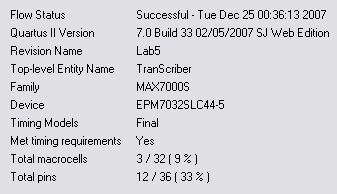

Установить в качестве целевой микросхемы (Assignments/ Device) микросхему семейства MAX7000S минимальной сложности (например, EPM7032SLC44-5). Назначение (расположение) внешних контактов проекта оставить «по умолчанию». Компилировать проект (Processing/ Start Compilation либо MAX+PLUS II / compilation).

-

Создать символ для проектируемого модуля – File/ “Create/ Update”/ Create Symbol File.

-

Оценить затраты на реализацию проекта Processing / Compilation Report.

-

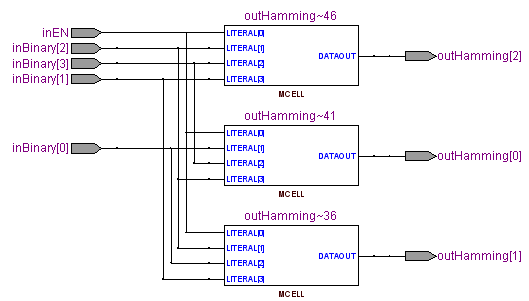

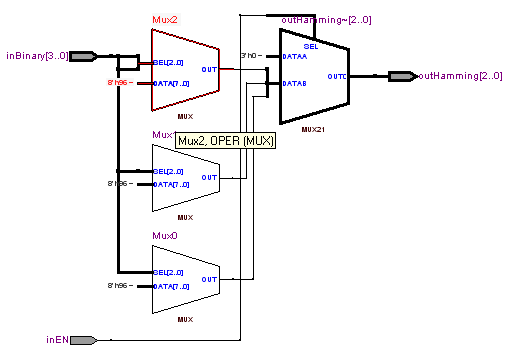

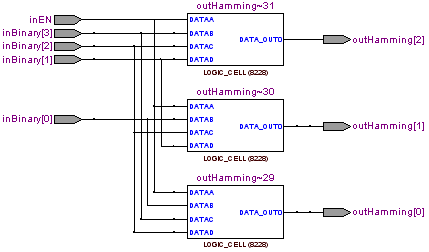

Просмотреть RTL вид проекта – Tools / Netlist Viewer/ RTL Viewer – Tools / Technology Map View.

-

Оценить временные характеристики реализации проекта – MAX+PLUS II/timing analyzer

-

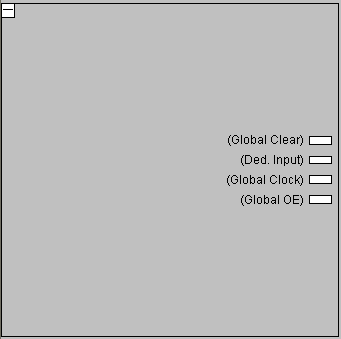

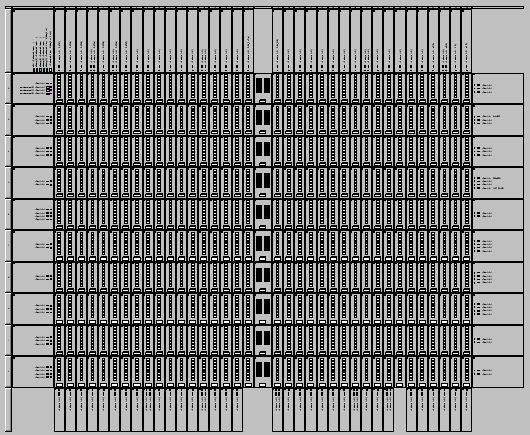

Просмотреть расположение проекта в заданной ИС – MAX+PLUS II/ Floorplan Editor.

-

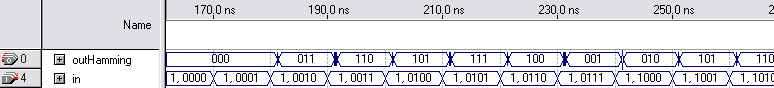

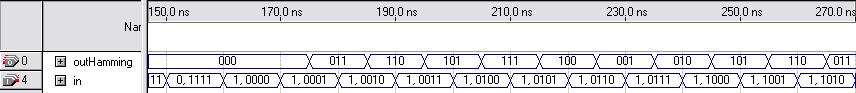

Моделировать поведение разработанной схемы – вызвать редактор MAX+PLUS II / Waveform Editor, установить время моделирования, установить шаг моделирования, сохранить файл с именем проекта. Вызвать сохраненный проект, вставить имена контролируемых и управляющих сигналов, задать поведение для входных управляющих сигналов, запустить на моделирование – MAX+PLUS II/ Simulation, либо Processing/ Start Simulation. Убедиться в правильности функционирования.

PART2

-

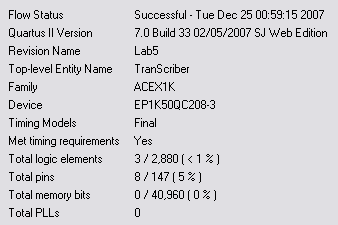

Установить в качестве целевой микросхемы (Assignments/ Device) микросхему семейства ACEX (EP1K50QC208-3). Назначение (расположение) внешних контактов проекта оставить «по умолчанию». Компилировать проект (Processing/ Start Compilation либо MAX+PLUS II / compilation).

-

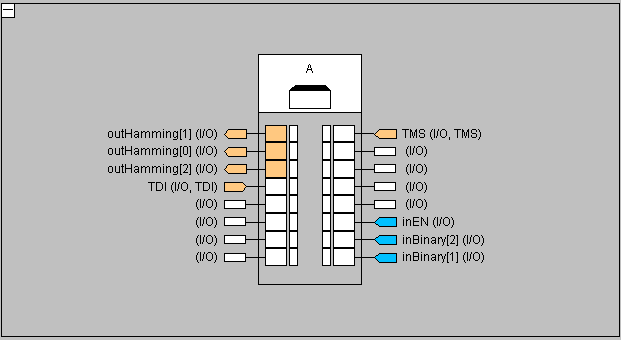

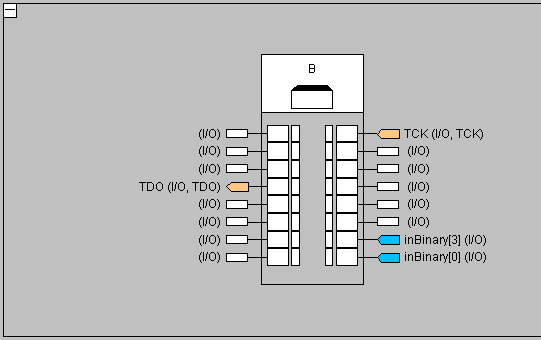

Создать символ для проектируемого модуля – File/ “Create/ Update”/ Create Symbol File.

-

Оценить затраты на реализацию проекта Processing / Compilation Report.

-

Просмотреть RTL вид проекта – Tools / Netlist Viewer/ RTL Viewer – Tools / Technology Map View.

-

Оценить временные характеристики реализации проекта – MAX+PLUS II/timing analyzer

-

Просмотреть расположение проекта в заданной ИС – MAX+PLUS II/ Floorplan Editor.

-

Моделировать поведение разработанной схемы – вызвать редактор MAX+PLUS II / Waveform Editor, установить время моделирования, установить шаг моделирования, сохранить файл с именем проекта. Вызвать сохраненный проект, вставить имена контролируемых и управляющих сигналов, задать поведение для входных управляющих сигналов, запустить на моделирование – MAX+PLUS II/ Simulation, либо Processing/ Start Simulation. Убедиться в правильности функционирования.