- •Лекция 7. Некоторые виды оперативной памяти эвм.

- •1. Основные модули оперативной памяти.

- •1.1. Sip модули

- •Simm модули.

- •1.2. История simm.

- •1.3. Dimm модули.

- •1.3.1. Разновидности dimm.

- •2. Основные типы оперативной памяти.

- •2.1. Статическая оперативная память с произвольным доступом (sram).

- •2.2. Динамическая оперативная память с произвольным доступом (dram).

- •2.2.1. Устройство и принцип действия dram.

- •Регенерация памяти.

- •2.2.2. Характеристики памяти dram.

- •2.2.3. Типы dram.

- •2.2.3.1. Страничная память.

- •2.2.3.2. Быстрая страничная память.

- •2.2.3.3. Edo dram — память с усовершенствованным выходом.

- •2.2.3.4. Sdram — синхронная dram.

- •2.2.3.6. Пакетная edo ram

- •Характеристики чипов

- •Спецификация модулей памяти

Регенерация памяти.

В отличие от быстрой, но дорогой статической памяти типа SRAM ( static random access memory), которая является конструктивно более сложным и более дорогим типом памяти и используется в основном в кэш-памяти, медленная, но дешёвая память DRAM изготавливается на основе конденсаторов небольшой ёмкости, которые быстро теряют заряд, поэтому информацию приходится обновлять через определённые промежутки времени во избежание потерь данных. Этот процесс называется регенерацией памяти. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации, в DRAM перезаписывается целая строка ячеек, и через 8-64 мс обновляются все строки памяти.

Процесс регенерации памяти в классическом варианте существенно тормозит работу системы, поскольку в это время обмен данными с памятью невозможен. Регенерация, основанная на обычном переборе строк, в современных типах DRAM не применяется. Существует несколько более экономичных вариантов этого процесса — расширенный, пакетный, распределённый; наиболее экономичной является скрытая (теневая) регенерация.

Среди новых технологий регенерации — PASR ( Partial Array Self Refresh), применяемый компанией Samsung в чипах памяти SDRAM с низким уровнем энергопотребления. Регенерация ячеек выполняется только в период ожидания в тех банках памяти, в которых имеются данные.

Параллельно с этой технологией реализуется метод TCSR ( Temperature Compensated Self Refresh), который предназначен для регулировки скорости процесса регенерации в зависимости от рабочей температуры.

Интерфейс памяти

В интерфейсе памяти существуют линии адреса и линии данных. Линии адреса служат для выбора адреса ячейки памяти, а линии данных - для чтения и для записи ее содержимого. Необходимый режим работы определяется состоянием специального вывода Write Enable (Разрешение Записи).

Низкий уровень сигнала WE готовит микросхему к считыванию состояния линий данных и записи полученной информации в соответствующую ячейку, а высокий, наоборот, заставляет считать содержимое ячейки и "выдать" его значения в линии данных.

Совмещение выводов микросхемы увеличивает скорость обмена с памятью, но не позволяет осуществлять чтение и запись одновременно (однако размещенные внутри кристалла процессора микросхемы кэш-памяти, имеют раздельные линии, таким образом, возможен одновременный процесс считывания из одной ячейку во время записи другой).

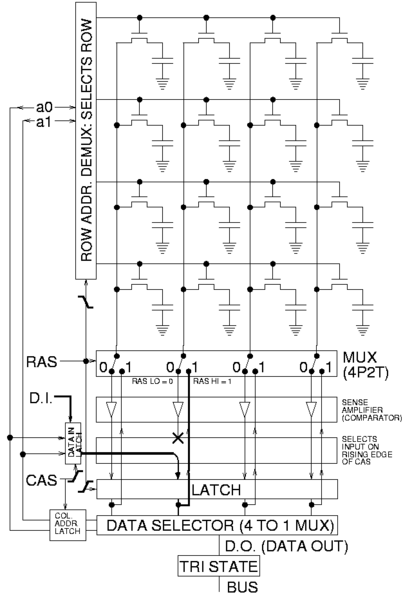

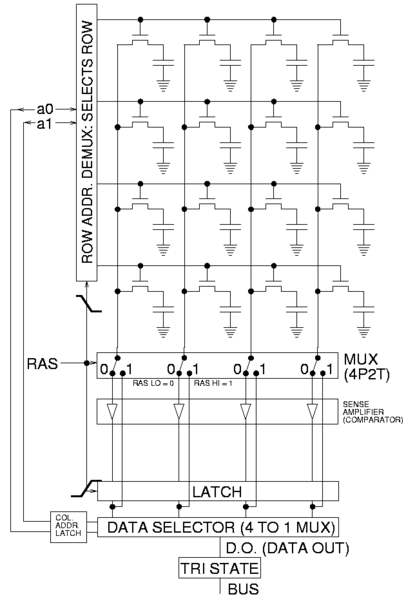

Столбцы и строки матрицы памяти тем же самым способом совмещаются в единых адресных линиях. В случае квадратной матрицы количество адресных линий сокращается вдвое, но и выбор конкретной ячейки памяти отнимает вдвое больше тактов, ведь номера столбца и строки приходится передавать последовательно. Причем, возникает неоднозначность, что именно в данный момент находится на адресной линии: номер строки или номер столбца? А, быть может, и вовсе не находится ничего? Решение этой проблемы потребовало двух дополнительных выводов, сигнализирующих о наличии столбца или строки на адресных линиях и окрещенных RAS (от row address strobe - строб адреса строки) и CAS (от column address strobe - строб адреса столбца) соответственно. В спокойном состоянии на обоих выводах поддерживается высокий уровень сигнала, что говорит микросхеме: никакой информации на адресных линиях нет и никаких действий предпринимать не требуется.

Когда возникает необходимость прочесть содержимое некоторой ячейки памяти, контроллер преобразует физический адрес в пару чисел - номер строки и номер столбца, а затем посылает первый из них на адресные линии. Дождавшись, когда сигнал стабилизируется, контроллер сбрасывает сигнал RAS в низкий уровень, сообщая микросхеме памяти о наличии информации на линии. Микросхема считывает этот адрес и подает на соответствующую строку матрицы электрический сигнал. Все транзисторы, подключенные к этой строке, открываются и бурный поток электронов, срываясь с насиженных обкладок конденсатора, устремляется на входы чувствительного усилителя. Чувствительный усилитель декодирует всю строку, преобразуя ее в последовательность нулей и единиц, и сохраняет полученную информацию в специальном буфере. Все это (в зависимости от конструктивных особенностей и качества изготовления микросхемы) занимает от двадцати до сотни наносекунд, в течение которых контроллер памяти выдерживает терпеливую паузу. Наконец, когда микросхема завершает чтение строки и вновь готова к приему информации, контроллер подает на адресные линии номер колонки и, дав сигналу стабилизироваться, сбрасывает CAS в низкое состояние. Затем микросхема и преобразует номер колонки в смещение ячейки внутри буфера. Остается всего лишь прочесть ее содержимое и выдать его на линии данных. Это занимает еще какое-то время, в течение которого контроллер ждет запрошенную информацию. На финальной стадии цикла обмена контроллер считывает состояние линий данных, дезактивирует сигналы RAS и CAS, устанавливая их в высокое состояние, а микросхема берет определенный тайм-аут на перезарядку внутренних цепей и восстановительную перезапись строки.

Рис.8. Принцип действия записи DRAM для простого массива 4 на 4

Рис.9. Принцип действия чтения DRAM для простого массива 4 на 4