ГОСУДАРСТВЕННОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ

ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

«ВОРОНЕЖСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

(ГОУВПО «ВГТУ»)

Факультет автоматики и электромеханики

Кафедра «Автоматизированные и вычислительные системы»

Специальность «Вычислительные машины, комплексы, системы и сети»

Лабораторная работа №6

по дисциплине «Теория автоматов»

по теме «Исследование алгоритмов функционирования триггерных схем»

Разработал А.А.Печенкин

Подпись, дата Инициалы, фамилия

Руководитель Ю. С. Акинина

Подпись, дата Инициалы, фамилия

Защищена _______________ Оценка _______________

Дата

Воронеж 2011

ЦЕЛЬ: закрепление теоретических основ формального синтеза элементарных автоматов с памятью. Получение практических навыков по реализации простейших триггерных схем в различных элементарных базисах, а также проверки работоспособности реализованных триггеров средствами пакета схемотехнического моделирования EWB.

ЗАДАНИЕ: Исследовать работоспособность триггерных схем средствами пакета схемотехнического моделирования EWB.

КРАТКИЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Автомат обладает полной системой переходов, если для каждой пары его внутренних состояний zi и zj найдётся хотя бы один сигнал xk, который переведёт автомат из состояния zi в zj .

Автомат обладает полной системой выходов, если для каждого zi вырабатывается сигнал yi, отличный от всех других выходных сигналов, соответствующий другим состояниям автомата.

Среди всех

возможных автоматов с полной системой

переходов и выходов элементарными

полными автоматами являются такие,

которые имеют всего два устойчивых

состояния и два выходных сигнала. Такие

элементарные автоматы называют

элементарными автоматами Мура или

триггерами. Граф элементарного автомата

Мура представлен на рис.1.

Рис1 Граф элементарного автомата Мура.

где Z1 – первое состояние автомата;

Z2 – первое состояние автомата;

X1 – входной сигнал, переводящий автомат из состояния Z1 в состояние Z2;

X2 – входной сигнал, переводящий автомат из состояния Z2 в состояние Z1;

Y1 – выходной сигнал, формируемый автоматом в состоянии Z1;

Y2 – выходной сигнал, формируемый автоматом в состоянии Z2.

Как видно из рис.1 элементарный полный автомат Мура является асинхронным, так как каждое его состояние является устойчивым.

Разновидности триггеров, используемых в практической цифровой схемотехнике, иллюстрирует рис.2.

Рис. 2 Разновидности триггеров.

Рассмотрим перечисленные разновидности триггеров [4,6,9].

RS-триггеры – триггеры с двумя установочными входами, при подаче активного сигнала на вход R (от англ. Reset – сбрасывать) происходит установка триггера в 0, а на вход S (от англ. Set - устанавливать) – установка триггера в 1.

T-триггеры – триггеры с одним счетным входом (от англ. Time - время), состояние которых изменяется на инверсное с приходом каждого импульса на его счетный вход.

D-триггеры – триггеры, осуществляющие прием информации по одному входу D (от англ. Delay - задержка), поэтому их еще называют триггерами задержки.

JK- триггеры – универсальные триггеры, при подаче активного сигнала на вход J (от англ. Jump -прыгать) происходит установка триггера в 1; а на вход K (от англ. Keep –хранить) – установка триггера в 0; при J=K=1 осуществляется поочерёдная установка триггера в 0 и в 1.

Особенностью комбинированных триггеров является то, что наряду с наличием у них синхронно управляемых входов, присутствуют также и входы асинхронной установки (S и R) триггеров в единичное “1” и нулевое “0” состояния. Входы асинхронной установки необходимы для приведения триггеров в некоторые исходные (начальные) состояния, которые в совокупности соответствуют начальному состоянию синтезируемого синхронного управляющего автомата. Сигнал, подаваемый на входы асинхронной установки триггеров для приведения их в начальные состояния, принято называть сигналом сброса (Reset) или начальной установки (Н.У.). Сигнал начальной установки должен воздействовать только на один из асинхронных входов (S или R) каждого триггера. Более подробно комбинированные триггерные схемы и их разновидности рассмотрены в [9].

Асинхронные триггеры – это триггеры, которые изменяют свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры – это триггеры, реагирующие на информационные сигналы только после подачи соответствующего сигнала на вход синхронизации С (от англ. Clock - часы). Вход С обозначают еще терминами «такт» и «строб».

Одноступенчатые (однотактные) триггеры – триггеры, содержащие один элемент памяти, в который сразу заносится входная информация.

Двухступенчатые (двухтактные) триггеры – триггеры с двумя элементами памяти, управляемыми с помощью сигналов синхронизации таким образом, что вначале информация заносится в первый элемент, а затем во второй.

Триггеры, управляемые статическими входами – это триггеры, управляемые потенциалами (уровнями напряжения 0 или 1).

Триггеры, управляемые динамическими входами – это триггеры, управляемые перепадами потенциалов (фронтом или срезом сигнала).

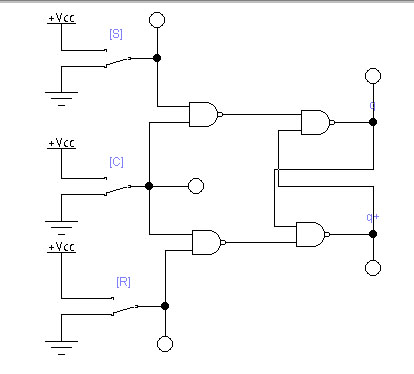

Синхронный однотактный RS-триггер

Недостатком однотактного асинхронного RS-триггера является то, что на его основе трудно реализовать надежно работающий блок памяти, содержащий большое количество триггеров данного типа, так как между сигналами, поступающими на информационные входы триггеров неизбежно существуют гонки (состязания). Для устранения данного недостатка были разработаны однотактные синхронные RS-триггеры.

Уравнение для однотактного синхронного RS- триггера:

На рис.3 а представлена схема однотактного синхронного RS- триггера, а его УГО на рис.3 б.

А Б

Рисунок 3 Однотактный синхронный RS-триггер

С |

R |

S |

Q(t) |

Q(t+1) |

|

|

0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

1 |

1 |

||

0 |

0 |

1 |

0 |

0 |

|

|

0 |

0 |

1 |

1 |

1 |

||

0 |

1 |

0 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

1 |

||

0 |

1 |

1 |

0 |

0 |

|

|

0 |

1 |

1 |

1 |

1 |

||

1 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

|

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

* |

|

|

1 |

1 |

1 |

1 |

* |

|

|

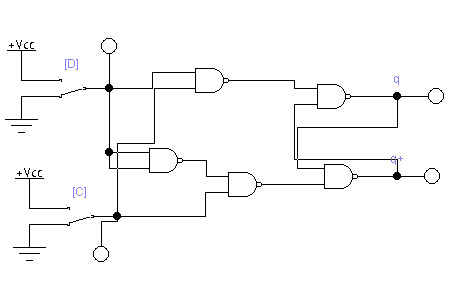

Синхронный однотактный d-триггер.

Для управления синхронным однотактным RS-триггером необходимо 3 входных сигнала (2-информационных; 1- управляющий). В то же время сигналы R и S никогда не должны быть одновременно активными, т.е. они должны быть в противофазе. Данное обстоятельство позволило построить еще одну разновидность триггерных схем, которые получила название D-триггер.

Уравнение однотактного асинхронного RS- триггера:

С |

D |

Q(t) |

Q(t+1) |

|

|

0 |

0 |

0 |

0 |

|

|

0 |

0 |

1 |

1 |

||

0 |

1 |

0 |

0 |

|

|

0 |

1 |

1 |

1 |

||

1 |

0 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

||

1 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

1 |

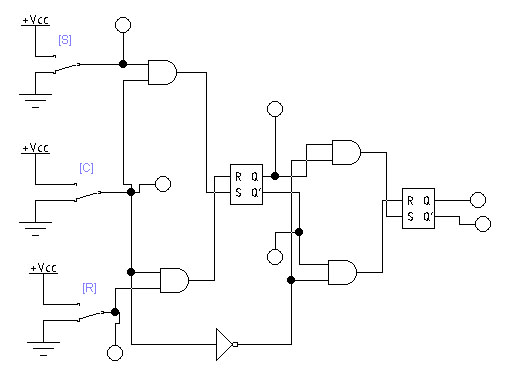

Синхронный двухтактный rs-триггер

Рассмотренные разновидности однотактных триггерных схем не позволяют реализовать так называемый режим счета (деление) входной тактовой частотой. Но именно данный режим работы триггерных схем является очень важным при построении различных вычислительных устройств.

При построении триггерных схем из обычных радио-электронных компонентов режим счета легко реализуется, т.к. очень просто построить дифференциирующую RC-цепи с требуемой постоянной времени, способной формировать очень короткие сигналы управления триггером. Однако в интегральной схемотехнике реализовывать дифференциирующую RC-цепь экономически не выгодно. Именно данное обстоятельство потребовало построения двухтактных триггерных схем.

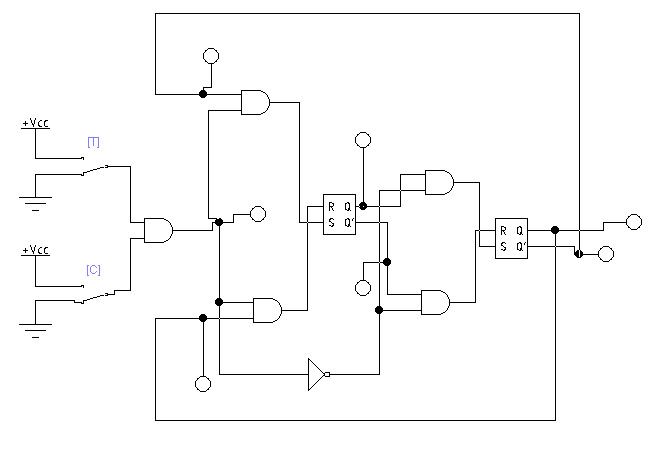

Асинхронный двухтактный т-триггер

Это счетный триггер. У асинхронного Т-триггера имеется только 1 вход. После поступления на этот вход импульса, состояние тригера меняется на прямо противоположное.

Т |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Т-триггеры можно синтезировать из любого двухступенчатого триггера, в данном случае мы взяли RS-триггеры. Двухступенчатые триггеры используются для того, чтобы избежать самовозбуждение схемы.

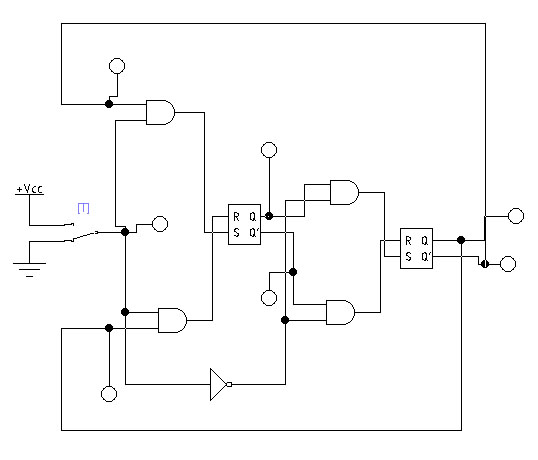

Синхронный двухтактный т-триггер

Синхронный Т-триггер отличается от асинхронного, наличием сигнала синхранизации.

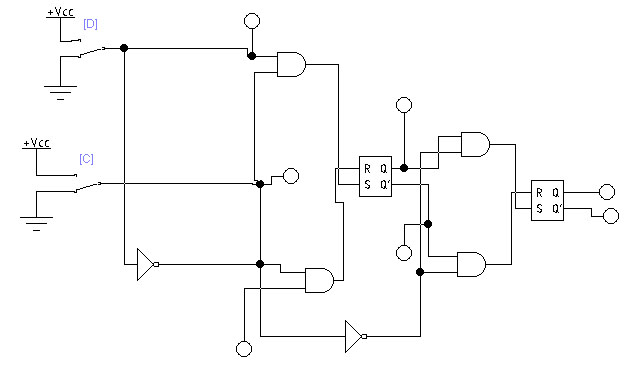

Синхронный двухтактный д-триггер

D-триггеры является результатом устранения недостатка RS-триггера- наличия запрещенных комбинаций. D-триггер по просту не используются.D-триггер является одной из универсальных триггерных схем.

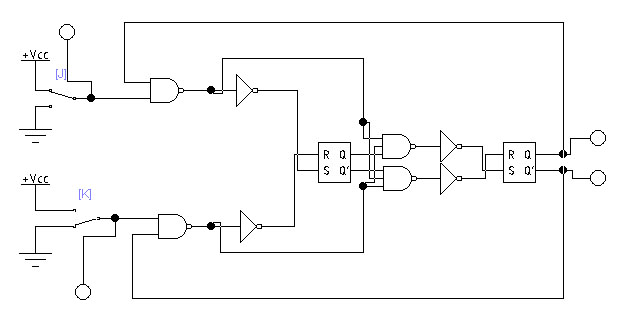

Асинхронный двухтактный jk-триггер

JK-триггер явяляется еще одним представителем класса универсальных триггерных схем. Как и D-триггер является результатом работы над устранением недостатка RS-триггера, но в отличии от предыдущего при подаче на информационные входы триггера логических единиц, триггер переходит в другое состояние. При такой комбинации сигналов JK-триггер работает как Т-триггер.

J |

K |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |