- •Глава7 программируемая логика и ее применение в микропроцессорных системах

- •7.1. Общие сведения, классификация

- •7.1.1. Уровень интеграции интегральных схем (ис) и его влияние на качество цифровой аппаратуры и ее проектирование.

- •7. 1. 4. Области применения микросхем с программируемой логикой

- •7.2. Первые поколениямикросхем с программируемой структурой

- •7.2.1. Программируемые логические матрицы и программируемая матричная логика

- •7.2.2. Базовые матричные кристаллы

- •7.3. Типичные фрагменты схемотехники ис пл. Общие свойства ис пл

- •7.3.1. Типичные схемотехнические решения

- •7.3.2. Свойства ис пл, важные для их применения в составе систем

- •7.4. Fpga-программируемые пользователем вентильные матрицы

- •7.4.1. Архитектура и блоки fpga

- •7.4.2. Популярные fpga фирмы «xilinx»

- •7.5. Cpld - сложные программируемые логические устройства

- •7.5.1. Архитектура и блоки cpld

- •7.5.2. Популярные cpld фирмы «altera»

- •7.6. Сбис пл комбинированной архитектуры

- •7.6.1. Общие сведения

- •7.6.2. Сбис пл комбинированной архитектуры flex10k

- •7.7. Сбис программируемой логики типа «система на кристалле»

- •7.7.1. Общие сведения

- •7.7.2. Сбис пл с конфигурируемостью всех областей кристалла

- •7.7.3. Сбис пл класса «система на кристалле» с блочной архитектурой

- •7.8. Конфигурирование бис/сбис программируемой логики

- •7.9. Методика оценки параметров ис пл

- •7.9.1. Вводные замечания

- •7.9.2. Об оценке сложности микросхем программируемой логики

- •7.9.3. Об оценке быстродействия микросхем программируемой логики

- •7.9.4. Параметры популярных семейств микросхем программируемой логики

- •7.10. Аналоговые программируемые микросхемы

- •7.10.1 Общие сведения

- •7.10.2. Практические разработки

7.5.2. Популярные cpld фирмы «altera»

Фирма «Altera» наряду с фирмой «Xilinx» принадлежит к крупнейшим разработчикам ИС ПЛ и занимает 30-40 % мирового рынка этой продукции. Преобладающей линией деятельности фирмы «Altera» является разработка именно CPLD, к которым далее добавились микросхемы комбинированной архитектуры и типа «система на кристалле».

Классическим представителем CPLD является семейство МАХ7000 (МАХ - аббревиатура от Multiple Array Matrix), выпускаемое фирмой «Altera». Микросхемы этого семейства имеют память конфигурации типа EEPROM, т. е. программируются введением зарядов в плавающие затворы ЛИЗМОП-транзисторов. При снятии питания конфигурация сохраняется. Стирание содержимого памяти конфигурации производится электрическими

сигналами в специальном режиме.

На рис. 7.19 показан фрагмент микросхемы семейства МАХ7000. Показан один ярус, содержащий логические блоки ЛБ и блоки ввода/вывода БВВ. У разных представителей семейства схемы составляются из разного числа ярусов: у младшего представителя всего один ярус, у старшего — восемь, соответственно этому у младшего представителя два ЛБ, у старшего -16. Логические блоки имеют по 16 макроячеек (МЯ), получающих термы от локальных программируемых матриц И (ЛПМИ). Программируемая матрица соединений ПМС обеспечивает межсоединения логических блоков таким образом, что на любой вход Л Б может быть подан сигнал от любого выхода Л Б или контакта ввода/вывода.

ПМС организована так, что на пути сигнала нет программируемых ключей и сигналы передаются через конъюнкторы, открытые по второму входу единичным сигналом, там, где это предусмотрено при конфигурировании микросхемы. Такое решение ускоряет передачу сигналов по линиям связи (рис. 7.20).На вход ЛБ может быть подан сигнал с любой непрерывной по длине вертикальной линии ПМС.

Все ЛБ связаны со своими блоками ввода/вывода, имеющими от 6 до 12 контактов (КП - контактная площадка). Так как в блоке 16 макроячеек, не все они могут иметь внешний вывод. Часть макроячеек может быть использована только для выработки сигналов обратной связи, передаваемых в ПМС. Это решение обосновано тем, что при построении ряда узлов многие логические функции нужны только для использования внутри схемы.

ПМС получает от каждого ЛБ 16 сигналов обратной связи, от блоков ввода/вывода - от 6 до 12 сигналов и четыре специализированных сигнала. К специализированным сигналам относятся глобальные (т. е. единые для всех одноименных блоков схемы) сигналы тактирования (GCLK1, GCLK2) и сброса (GCLR), а также сигналы разрешения выходов ОЕ. Из ПМС поступает по 36 сигналов для каждого ЛБ и еще шесть сигналов, которые прямо или инверсно передаются через мультиплексор MUX3 для глобальной шины разрешения выходов БВВ.

Схема макроячейки показана на рис. 7.21. Из матрицы элементов И в матрицу распределения термов МРТ поступает пять основных термов (на рисунке слева). МРТ дает возможность использовать эти термы для сборки по ИЛИ с последующей подачей результата на элемент сложения по модулю 2 для образования комбинационной функции, а также для управления триггером по входам сброса (CLRn) и установки (PRn). Терм t может быть использован для тактирования триггера или разрешения тактирования в зависимости от программирования мультиплексора MUX2.

Триггер имеет гибкую систему управления записью данных. Он может тактироваться от глобального сигнала GCLK, причем такое тактирование может сопровождаться индивидуальным управлением от сигнала разрешения ENA. Возможно тактирование и от локального сигнала t.

Разнообразные варианты тактирования предоставляют удобство построения автоматов с памятью разных типов (синхронных, апериодических, асинхронных).

Установка и сброс триггера возможны от асинхронных сигналов PRn и CLRn, кроме того, возможен сброс от глобального сигнала GCLR при соответствующем программировании мультплексора MUX3.

В зависимости от программирования мультиплексора MUX1 на вход триггера поступает значение функции, выработанное логическими схемами макроячейки, или же триггер загружается от внешнего вывода по цепи быстрого ввода.

Мультиплексор MUX4 позволяет подавать на выход макроячейки (к блоку ввода/вывода) либо непосредственно комбинационную функцию, либо хранимую в триггере (регистровый выход).

Если для реализации требуемой функции макроячейке не хватает термов, можно воспользоваться ресурсами логических расширителей ЛР. Первый тип ЛР, называемый общим (разделяемым), образуется за счет терма пятой линии, который вводится в матрицу И и становится доступным для всех макроячеек. Так как в логическом блоке 16 макроячеек, общий ЛР может иметь до 16 линий (рис. 7.21).

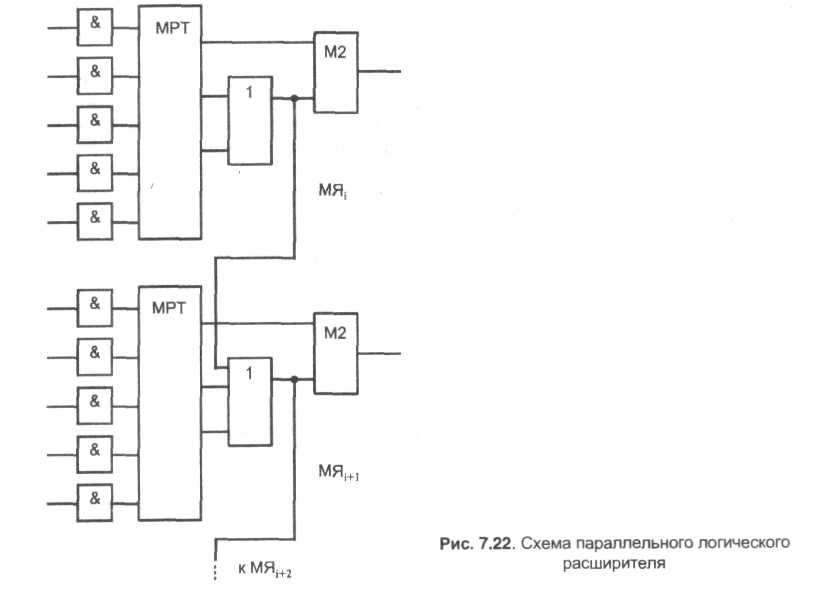

Параллельный ЛР образуется с помощью коммутации термов, передаваемых от предшествующих макроячеек в последующие как по цепочке (рис. 7.22).Допускается образование цепочек длиною до 8 звеньев.

Блок ввода/вывода (рис. 7.23) позволяет гибко управлять состоянием выходного буфера. ПМС формирует для этой цели шесть глобальных сигналов разрешения выхода ОЕ, каждый из выводов благодаря программированию мультиплексора MUX может подключаться к любому из шести сигналов. У некоторых микросхем семейства МАХ7000 предусмотрена возможность запрограммировать выход с открытым стоком. Кроме того, программируется и скорость изменения выходных напряжений буферов (крутизна фронтов в вариантах быстрая/медленная; полезность этой возможности обсуждалась ранее.