- •Часть 2. Синтез и анализ цифровых схем мп сау омт.

- •Глава 4. Синтез и анализ комбинационных логических схем мп сау.

- •4.1 Классификация вычислительных средств для объектов морской техники

- •4.2 Формы и способы представления информации в мп сау.

- •4.2.1 Параллельный способ обмена информацией.

- •4.3 Основные этапы синтеза комбинационных логических схем.

- •4.3.1 Пример синтеза простейшей комбинационной логической схемы.

- •6 Этап синтеза: численная оценка компонент критерия синтезируемой схемы.

- •4.4 Синтез специальных комбинационных логических схем ( клс), используемых в мп сау.

- •4.4.1 Синтез схемы для выполнения функции контроля нечётности двоичных кодов.

- •Лабораторный практикум №1.1.

- •Логическая схема на элементах или-не

- •Логическая схема на элементах и-не

- •Лабораторный практикум №1.2.

- •4.5 Преобразователи кодов во внешних и внутренних каналах связи в мп сау.

- •4.5.1 Преобразователь кода Грея в простой двоичный код.

- •Преобразователь двоичного кода в циклический код.

- •Лабораторный практикум №1.3.

- •4.6 Синтез преобразователя внутренних кодов на примере дополнительного кода.

- •4.6.1 Аппаратная реализация преобразователя с использованием элементов м2 и или.

- •4.7 Синтез клс для выполнения операции сравнения n – разрядных двоичных кодов.

- •Лабораторный практикум № 1.4.

- •4.7.1 Схемная реализация отношения равенства (эквивалентности).

- •Лабораторный практикум №1.5

6 Этап синтеза: численная оценка компонент критерия синтезируемой схемы.

Минимум аппаратных затрат может быть оценен суммарным числом выходов и входов используемых в схеме логических элементов:

MINA = ВХ i + ВЫХ j =6+3=9

Оценка быстродействия связана с количеством каскадов (ступеней) используемых для построения схемы:

MAXБ = 2

4.4 Синтез специальных комбинационных логических схем ( клс), используемых в мп сау.

При использовании критериев min аппаратных затрат и max быстродействия в задаче синтеза специальных логических схем , необходимо обосновать выбор элементной базы, обеспечивающей сопряжение синтезируемых схем с аппаратурой, для которой они предназначены. Часто затраты на устройство сопряжения превышают затраты на разработку собственно КЛС. Это и является причиной, мотивирующей создание специальных КЛС. Как правило, назначение этих схем специализировано, но решаемые ими задачи могут быть многократно востребуемы в МП САУ.

4.4.1 Синтез схемы для выполнения функции контроля нечётности двоичных кодов.

В качестве элементной базы, в зависимости от принципов построения МП САУ, на которые ориентируется синтезируемая схема, могут использоваться:

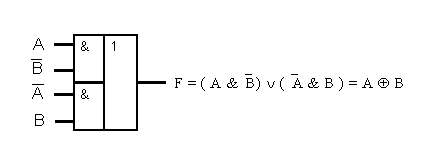

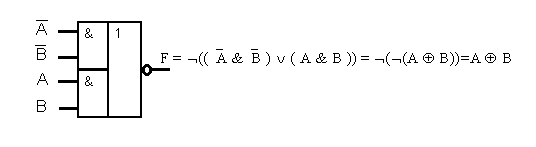

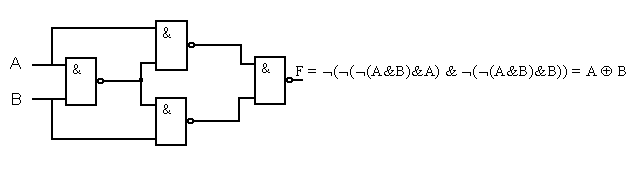

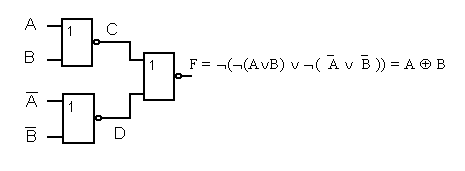

Логические элементы суммирования по модулю 2 ( М2) см. рис.4.7:

Рис.4.7 Логическая схема сложения по модулю 2.

Эти элементы имеют только два входа и предполагают использование параллельно-последовательных или параллельных схем их соединения при реализации функции нечетности.

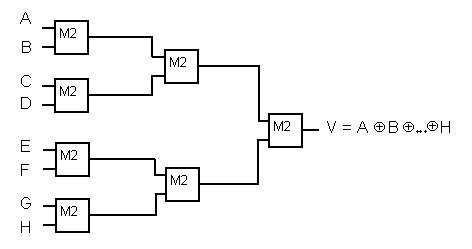

В случае четного числа разрядов контролируемого кода предпочтительнее использование параллельной схемы (рис.4.8), обеспечивающей min критерию аппаратных затрат (4.3).

Рис.4.8 Параллельная логическая схема контроля нечетности двоичного кода.

КА = ВХ i + ВЫХ j =14+7=21 (4.3)

КВ1 =3*М2

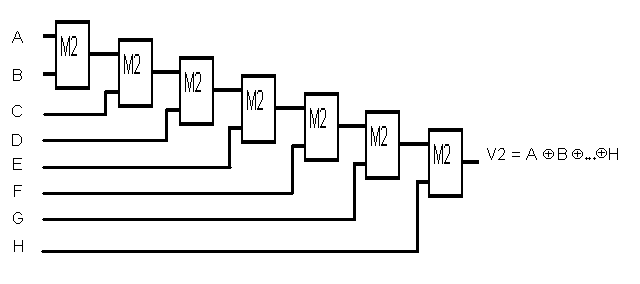

При произвольном числе разрядов контролируемого кода возможно использование параллельно-последовательной

схемы (рис.4.9) на элементах M2.

Рис.4.9 Параллельно-последовательная логическая схема контроля нечетности двоичного кода.

КА 2 =14+7=21

КА 1 = КА 2

КБ 2 =7*М2

При использовании произвольной элементной базы необходимо выполнить этапы синтеза, перечисленные ранее. Рассмотрим эту последовательность этапов для 3-х разрядного кода:

СДНФ:

F(A,B,C) = (A &B & C) (A & B & C) (A &B &C) (A & B & C)

Таблица 4.4

Десятичный эквивалент |

А В С |

F(А,В,С) |

0 1 2 3 4 5 6 7 |

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 |

0 1 1 0 1 0 0 1 |

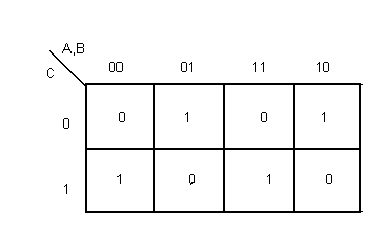

Преобразуем F к минимальной форме, используя графоаналитический метод .Графоаналитический метод бесполезен для случая табл.4.5. С его помощью нельзя получить минимальную форму логической функции.

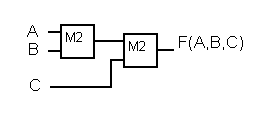

Преобразуем исходную функцию, используя дистрибутивные законы (4.4) и постоим схему (рис.4.10).

F(A,B,C) = (((A & B)(A &B))&C) (((A &B)(A & B))& C)= ((A B)&C) ((A B)& C )= A B C (4.4)

Таблица 4.5

Рис.4.10 Синтезированная логическая схема

В зависимости от элементов, на которых построена основная система, синтезируемая схема может использовать:

Элементы И-ИЛИ :

Активные элементы И-ИЛИ-НЕ :

3. Элементы И-НЕ (штрих Шеффера):

4. Элементы ИЛИ-НЕ (стрелка Пирса):

Используя перечисленные элементы ,решим задачу контроля кодированной информации в МП САУ.