- •Глава_5 Синтез последовательностных схем (элементов памяти), используемых в качестве элементной базы в мп сау.

- •5.1 Синтез асинхронных триггеров.

- •5.1.1 Синтез первой минимальной формы для запоминающего элемента.

- •5.2 Синтез второй минимальной формы при построении запоминающего элемента.

- •Лабораторный практикум №5.1.

- •Лабораторный практикум №5.2.

- •Лабораторный практикум №5.3

- •5.3 Синхронные элементы памяти, используемые в мп сау.

- •5.3.1 Синтез двухступенчатого элемента памяти, работающего в парафазном коде.

- •5.4 Синхронные элементы памяти для последовательных регистров (d - триггеры).

- •5.5 Синтез двухступенчатого т - триггера.

- •5.5.1. Синхронный т - триггер на элементах и-не.

- •5.5.2. Синтез комбинированного rst – триггера

- •Лабораторный практикум № 5.4.

- •5.6 Универсальные элементы памяти. Принцип организации специальных элементов памяти на базе универсальных.

- •5.6.1 Синтез универсального jk – триггера.

- •Лабораторный практикум №5.5.

- •Вопросы для самоконтроля знаний по материалам главы 5.

Лабораторный практикум №5.3

Задание:

Синтезировать асинхронный ЗЭ в соответствии с четвертой минимальной формой на элементах И-ИЛИ-НЕ.

Таблица 5.10

-

Sn , Rn

Qn

00 01 11 10

0

1

0

0

1

1

1

0

0

1

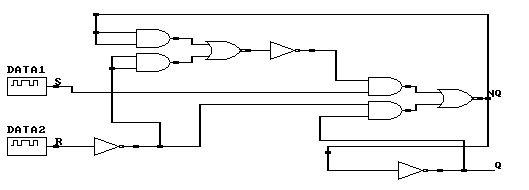

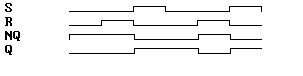

Синтезированный асинхронный ЗЭ.

Временная диаграмма асинхронного ЗЭ

5.3 Синхронные элементы памяти, используемые в мп сау.

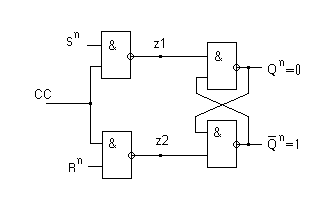

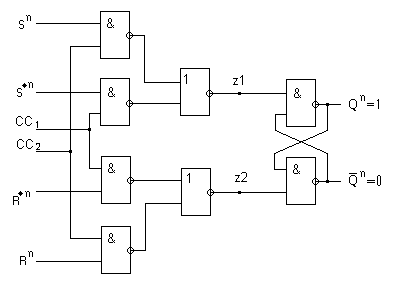

Рассмотрим синхронный RS-триггер, построенный на элементах И-НЕ (рис.5.7) и запишем уравнение, организующее переключение триггера, при воздействии информационных и синхронизирующих сигналов.

Рис.5.7 Схема синхронного RS -триггера

СС-сигнал синхронизации.

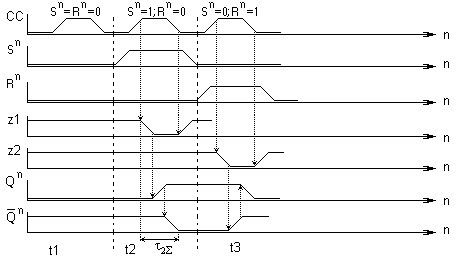

Динамика переключения информационных сигналов во входной логике и на элементе памяти триггера имеет вид (рис.5.8):

рассмотрим на

тестирующей временной диаграмме:

Рис.5.8 Временная диаграмма синхронного RS –триггера.

На первом интервале тестирования t1 значения управляющих сигналов z1 и z2 определяются соотношением:

и не приводят к изменению исходного установившегося состояния элемента памяти.

(Qn+1 , Qn+1 ~ Qn , Qn)

Оценка динамических свойств синхронных элементов памяти позволяет предъявить требования к запаздыванию в компонентах элементной базы, используемых для построения синтезируемого устройства.

2 min

Выполнение этого условия позволяет синтезировать элемент с максимальным быстродействием, с точки зрения переходных процессов синтезируемой схемы.

5.3.1 Синтез двухступенчатого элемента памяти, работающего в парафазном коде.

Использование парафазного кода позволяет исключить из цикла работы цифрового устройства (рис.5.9) фазу его установки исходного состояния и таким образом повысить быстродействие устройства минимум на один такт автоматного времени.

В качестве элементной базы выберем элементы: И-НЕ, ИЛИ-НЕ, И.

Рис.5.9 Схема восприятия триггером парафазного кода.

Установка запоминающего элемента в единичное состояние осуществляется управляющим сигналом z1 при обязательном выполнении условия не совпадения во времени синхронизирующих сигналов 1 и 2. Нулевое состояние памяти синхронизируется сигналом z2.

5.4 Синхронные элементы памяти для последовательных регистров (d - триггеры).

Синхронный двухступенчатый D триггер(рис.5.10) может быть построен с использованием RS - триггеров, управляемых одновременно информационным и синхронизирующим сигналом.

Рис.5.10Двухступенчатый синхронный D –триггер.

Переключение синхронного D - триггера определяется временными соотношениями между информационным Dn и синхронизирующим сигналом. Установка первой ступени RS1 в установившееся состояние, заканчивается в момент окончания действия сигнала синхронизации. Временные соотношения между Dn и СС такие же, как и у рассматриваемого синхронного RS - триггера.

Состояние ступени RS1 переписывается в ступень RS2, только после завершения действия на схему сигнала синхронизации, что обеспечивает устойчивый сдвиг информационного сигнала на один такт сигнала синхронизации.

Временная диаграмма работы D – триггера.

Возможны и другие принципы построения D - триггеров, а именно, перевод универсальных запоминающих элементов в режим работы специализированных элементов памяти.

С позиции однородности структуры устройств, использующие эти элементы , второй подход предпочтительней. При построении специальных вычислителей, он приводит к недопустимо большим аппаратным затратам.

Различают универсальные и специализированные элементы для запоминающего устройства. К первым относятся универсальные JK, DF и другие триггеры, которые обладают аппаратной избыточностью и предоставляют разработчику возможность построения запоминающего устройства однородной структуры, что приемлемо при отсутствии ограничений на потребляемую мощность и габаритные характеристики. Если же подобные ограничения существуют, что характерно для специализированных запоминающих устройств, то предпочтительнее в качестве их элементов использовать специальные триггеры.