- •Глава 6. Синтез узлов и устройств для мп сау омт .

- •6.1 Синтез управляющих схем для многофункциональных регистров.

- •6.1.1 Формирование прямого и обратного парафазных кодов на параллельном регистре.

- •6.2 Поразрядная обработка машинных слов с использованием параллельных регистров.

- •Лабороторный практикум № 6.1

- •Парафазном коде”.

- •6.3 Маскирование машинных слов для выделения составляющих их кодов.

- •6.4 Выполнение на параллельных регистрах операции сравнивания кодов.

- •6.5 Синтез последовательных регистров на различной элементной базе.

- •6.5.1 Использование последовательных регистров парафазного кода.

- •6.5.2 Реализация сдвига с использованием регистра на т-триггерах.

- •Лабороторный практикум № 6.2

- •6.5.3 Двухступенчитый регистр сдвига, использующий парофазный код.

- •Лабороторный практикум № 6.3

- •6.5.4 Регистры сдвига с перекрёстными связями на rs-триггерах.

- •Лабороторный практикум № 6.4

- •6.5.5 Регистры сдвига на синхронных элементах памяти

- •6.6 Использование универсальных запоминающих элементов для построения последовательных регистров

- •6.6.1 Реверсивный регистр сдвига на jk-триггерах

- •6.6.2 Циклический регистр сдвига

- •6.7 Синтез дешифраторов на базе клс

- •6.7.1 Помехоустойчивость линейных дешифраторов

- •6.8 Пирамидальные дешифраторы

6.8 Пирамидальные дешифраторы

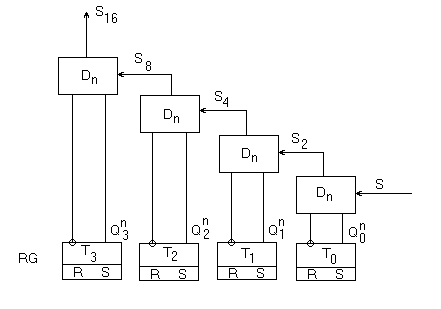

Источником входной информации для пирамидальных дешифраторов (рис.6.20) являются параллельные и последовательные регистры, в последнем случае циклические, формирующие, как правило, входные слова в виде параллельного кода, отображаемого потенциальными сигналами.

Рис.6.20 Схема пирамидального дешифратора.

.

Управляющая информация, представленная

здесь символами S,

является импульсной и, начиная с

выходов S2,

преобразуется в выходную информацию

дешифратора. Оценим аппаратные затраты

пирамидального дешифратора: количество

схем И, входящих в Dn

, что можно описать как

,

где n

– разрядность входного слова. Суммарное

число входов в элементах Dn

равно 2n,

а быстродействие оценивается как

,

где n

– разрядность входного слова. Суммарное

число входов в элементах Dn

равно 2n,

а быстродействие оценивается как

.

.

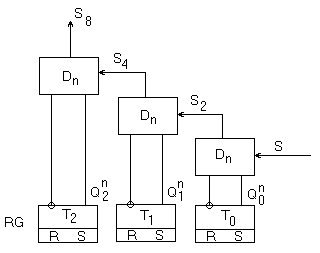

Спроектируем пирамидальный дешифратор для n=3,структура которого представлена на рис.6.21:

Рис.6.21 Структура пирамидального дешифратора

Для 3-х битного входного слова.

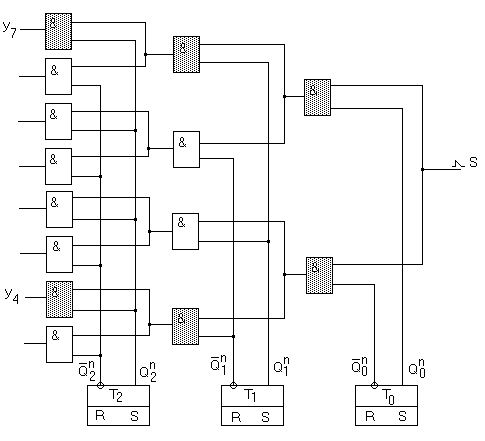

Рис.6.22 Пирамидальный дешифратор, построенный на элементах И, имеющих только два входа.

Пусть

входное слово имеет вид :

, тогда получим сигнал на выходе y4.

, тогда получим сигнал на выходе y4.

Пусть

входное слово имеет вид :

, тогда получим сигнал на выходе y7.

, тогда получим сигнал на выходе y7.

Схемы дешифраторов выполняют двойную роль в цифровых системах: с одной стороны они используются для преобразования параллельных кодов в управляющие сигналы, которые осуществляют адресную выборку информации; с другой стороны они могут выполнять роль мультиплексора, распределяющего входную информацию по выбранным каналам.

Сочетание управляющих схем и схем, преобразующих цифровую информацию , позволяет строить специальные микропроцессорные устройства для систем автоматического управления (САУ) объектов морской техники (ОМТ).

Вопросы самоконтроля знаний по материалам главы 6.

1.Перечислите основные функции параллельного регистра?

2.Что дает использование парафазного кода в параллельных регистрах МП?

3.За счет чего повышается быстродействие параллельного регистра, работающего с парафазными кодами?

4.