- •1.Основні логічні елементи

- •2.Математичний(логічний) опис логічних схем.

- •3.Правила і закони алгебри-логіки

- •Комбінаційні закони

- •Правило поглинання

- •Правило склеювання

- •4.Логічний елемент виключне або.Застосування

- •5.Мінімізація логічних схем

- •6.Карти Карно

- •7.Теореми де.Моргана

- •8.Синтез схем на логічних елементах

- •9.Карти Карно для більш ніж 5 змінних

- •10.Схема контролю на парність(непарність)

- •11.Швидкодія мікросхем,час перемикань елемента чи логічної схеми

- •12.Навантажувальна здатність мікросхем

- •13.Завадостійкість мікросхем

- •14.Комбінаційні послідовнісні схеми

- •15.Арифметичний суматор,додавання двійкових кодів

- •16.Півсуматор,повний суматор, таблиця станів

- •17.Віднімання двійкових кодів

- •18.Множення двійкових кодів.Блок-схема перемножувала кодів

- •19.Арифметично-логічні пристрої

- •20.Шифратори та дешифратори

- •21.Тригерні пристрої,класифікація,застосування

- •26.Двійкові лічильники,режими роботи лічильників

- •27.Регістри

- •28.Принципи побудови озп і пзп

- •29.Базові схеми ттл технології

- •30.Базові схеми кнон

- •31.Мультиплексори,Демультиплексори

- •32.Цифрові комператори(порівнювані)

21.Тригерні пристрої,класифікація,застосування

Тригерні пристрої є найбільш поширеними функціональними елементами цифрових систем. Найбільше застосування тригери знаходять в лічильниках, регістрах, елементах пам'яті, розподільниках сигналів, що накопичують суматора і ін Тригери мають і самостійне застосування, наприклад в приладах управління, виконуючи функції логічного перетворення та зберігання інформації.

Тригерами (trigger або flip - flop) (тригерними пристроями, системами) називають великий клас електронних пристроїв, що володіють двома і більше стійкими станами електричної рівноваги, здатних під дією зовнішніх (керуючих, перемикаючих) сигналів перемикатися в будь-яке з цих станів і перебувати в них як завгодно довго після припинення їх дії. Стан тригера - це значення, яке в ньому зберігається в даний час.

Якщо таких стійких станів два, то тригери називаються бістабільні. Тригери з числом станів більше двох називаються многостабільнимі. У бістабільних тригерах кожне стан легко помітна за рівнями напруг на його виходах. Бістабільні тригери, як правило, мають два виходи (плеча): прямий вихід позначається Q і інверсний вихід позначається . Тригер з двома виходами називається парафазного тригером. Ряд тригерів має один вихід. Такі тригери називаються однофазними.

Прийнявши один зі станів тригера за 1 (тобто Q = 1), друге за 0 (тобто Q = 0), можна вважати, що тригер зберігає один біт інформації, записаної в двійковому коді. При цьому залежно від того, яка форма сигналу приймається за 1 і 0, тобто в залежності від способу кодування станів, всі тригери поділяються на тригери з потенційним і імпульсним кодуванням. Відмінною особливістю тригерів з потенційним кодуванням є те, що кожному стану тригера ставиться у відповідність наявність сигналу постійної амплітуди високого (близького до напруги живлення) та низького (близького до нуля) логічних рівнів. При цьому, якщо сигнал на виході тригера Q відповідає високому рівню напруги, кажуть, що тригер знаходиться в стані 1 (Q = 1), а якщо низького, то в стані 0 (Q = 0).

Тригер з імпульсним кодуванням стану характеризується наявністю імпульсів певної амплітуди і тривалості, якщо він знаходиться в стані 1, і відсутністю імпульсів, якщо він знаходиться в стані 0.

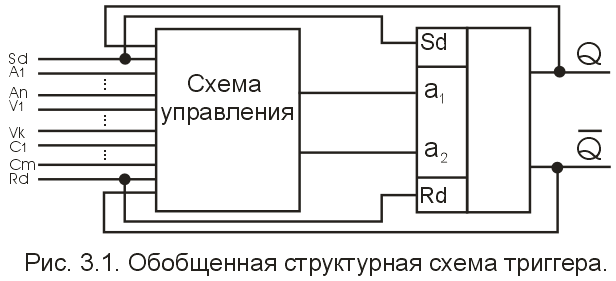

Тригери з імпульсним кодуванням широко застосовувалися на початковому етапі розвитку обчислювальної техніки, коли електронні лампи, а потім транзистори були основними компонентами електронних пристроїв. В даний час вони не знаходять застосування і тому надалі будемо розглядати тригери з потенційним кодуванням. Узагальнена структурна схема такого тригера показано на рис. 1.

Рис. 1 Узагальнена структурна схема тригера

Схема тригера складається з елементу пам'яті (як правило, власне тригера з двома стійкими станами) і схеми управління з низкою входів .

Схема управління перетворює надходить на її входи інформацію в одну з комбінацій сигналів 00,01,10,11 діють безпосередньо на входи власне тригера. Входи , На які надходить записувана інформація, називають інформаційними або логічними. Окрім логічних схема тригера може мати тактові входи або входи синхронізації ( ), Що дозволяють (управляючі) входи , А також входи Sd, Rd безпосередньої установки тригера - установочні входи. Слід підкреслити, що все різноманіття застосовуваних тригерів визначається організацією схеми управління, яка сама може містити додаткові елементи пам'яті, і її зв'язками з виходами тригера Q і .

Можливі й більш прості схеми тригерних пристроїв, наприклад такі, в яких відсутні дозвільні V або тактові входи C, виключено пристрій управління або відсутні зв'язку з виходів Q і на входи пристрою управління.

Цифрова схема, яка містить тригери, називається послiдовнiсних схем, оскільки значення сигналу на її виході в якийсь момент часу залежить не тільки від сигналів, що є на вході схеми в цей момент часу, але так само і від попередньої послідовності значень сигналів, які були на її вході раніше. Іншими словами, послідовних схема має пам'ять (memory) по відношенню до подій відбувалися раніше.

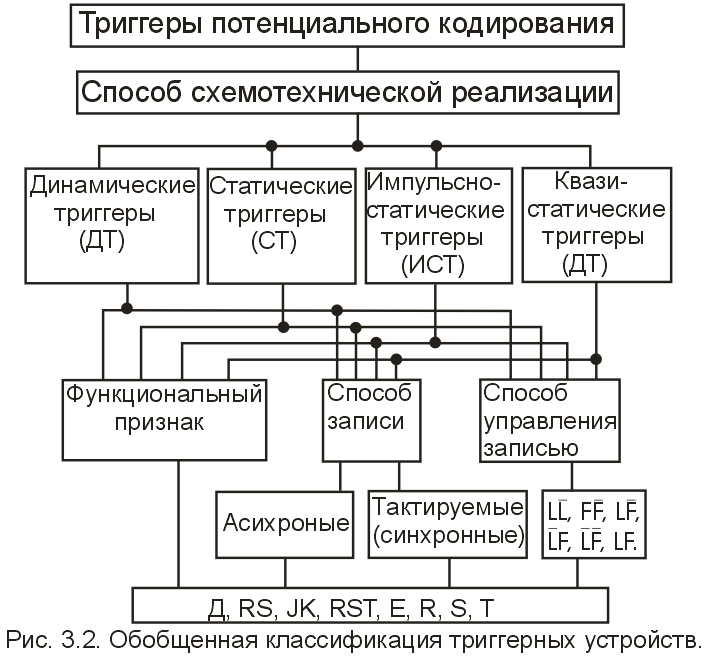

Рис. 2 Узагальнена класифікація тригерних пристроїв

В основу класифікації покладено такі ознаки:

спосіб схемної реалізації;

функціональний ознака;

спосіб запису інформації в тригер;

спосіб управління записом інформації.

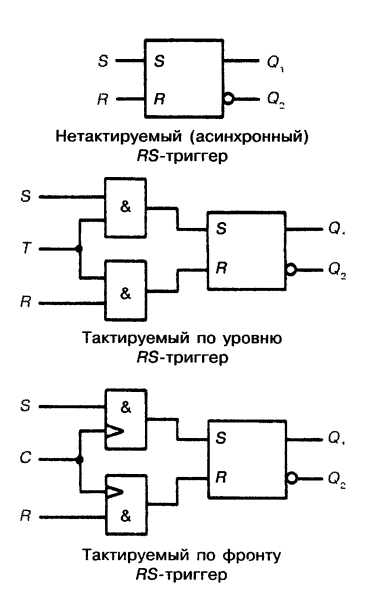

22. RS- тригер

Нетактовний RS-тригер (див. рис. 7.27) перетворюється за допомогою двох И-елементів, підключених до тригера відповідно до рис. 7.29, в тактований RS-тригер. Якщо обидва ці елементи замінити імпульсними елементами, то отримують тактований фронтально керований RS-тригер (рис. 7.50). Тригер переключається при переході сигналу синхронізації з 0 на 1, тобто з переднім фронтом імпульсу. Умовне позначення цього тригера наведено на рис. 7.51. Для позначення входу синхронізації (тактуючого входу) використовується буква С (від англ. Clock - годинники). С-вхід впливає на обидва входи тригера і тому зображається в середині.

Якщо використовують імпульсні елементи іншого виду, то отримують RS-тригер, який переключається заднім фронтом імпульсу (рис. 7.52). Потрібні два додаткові елементи НЕ або ще можна застосувати тригер на елементах І-НЕ, показаний на рис. 7.26.

Схеми, що застосовуються в області інтегральних мікросхем, є в основному більш складними. Розробники прагнуть отримати більшу завадостійкість при можливо більш високої робочої швидкості.

Розглянутий тактований по фронту RS-тригер називається також керованим по одному фронту RS-тригером.

Rs-трігер використовується для створення сигналу з позитивним і негативним фронтами, окремо керованими за допомогою стробів, рознесених в часі. Також rs-трігері часто використовуються для виключення так званого явища брязкоту контактів.

23.T-тригер математичний опис застосування

T тригер — це рахунковий тригер. В T тригера є лише один вхід. Після вступу на цей вхід імпульсу, стан T тригера міняється на прямо протилежне. Рахунковим він називається тому, що він як би підраховує кількість імпульсів, що поступили на його вхід. Шкода лише, що рахувати цей тригер уміє лише до одного. Під час вступу другого імпульсу T тригер знову скидається у вихідний стан. T тригери будуються лише на базі двоступінчатих тригерів, подібних розглянутому раніше D тригеру. Використання двох тригерів дозволяє уникнути невизначеного стану схеми при вирішуючому потенціалі на вході синхронізації "C", оскільки рахункові тригери будуються за допомогою схем із зворотним зв'язком T тригер можна синтезувати з будь-якого двоступінчатого тригера. Розглянемо приклад синтезу T тригера з динамічного тригера D. Для того, щоб перетворити D тригер в рахунковий, необхідно ввести ланцюг зворотного зв'язку з інверсного виходу цього тригера на вхід як показано на малюнку 1.

Малюнок 1. Схема T тригера, побудована на основі D тригера

Т-трігері використовуються при побудові схем різних лічильників, тому в складі БІС різного призначення зазвичай є готові модулі цих тригерів.

24.D-тригер застосування

D-тригери також називають тригерами затримки.

D-трігер (D від англ. delay — затримка або від data - дані) — запам'ятовує стан входу і видає його на вихід. D-трігері мають, як мінімум, два входи: інформаційний D і синхронізації С. После приходу активного фронту імпульсу синхронізації на вхід З d-трігер відкривається. Збереження інформації в d-трігерах відбувається після спаду імпульсу синхронізації С. Так як інформація на виході залишається незмінною до приходу чергового імпульсу синхронізації, d-трігер називають також тригером із запам'ятовуванням інформації або тригером-клямкою. Міркуючи чисто теоретично, парафазний (двофазний) d-трігер можна утворити з будь-яких RS- або jk-трігерів, якщо на їх входи одночасно подавати взаємно інверсні сигнали.

D-трігер в основному використовується для реалізації клямки. Так, наприклад, для зняття 32 біт інформації з паралельної шини, беруть 32 d-трігері і об'єднують їх входи синхронізації для управління записом інформації в клямку, а 32 D входу під'єднують до шини.

У одноступінчатих d-трігерах під час прозорості всі зміни інформації на вході D передаються на вихід Q. Там, де це небажано, потрібно застосовувати двоступінчаті (двухтактниє, Master-slave, MS) d-трігері.

25.JK-тригер застосування

Jk-трігер працює так само як rs-трігер, з одним лише виключенням: при подачі логічної одиниці на обидва входи J і K стан виходу тригера змінюється на протилежний. Вхід J (від англ. Jump — стрибок) аналогічний входу S в rs-трігера. Вхід K (від англ. Kill — убити) аналогічний входу R в rs-трігера. При подачі одиниці на вхід J і нуля на вхід K вихідний стан тригера стає рівним логічній одиниці. А при подачі одиниці на вхід K і нуля на вхід J вихідний стан тригера стає рівним логічному нулю. Jk-трігер на відміну від rs-трігера не має заборонених перебувань на основних входах, проте це ніяк не допомагає при порушенні правил розробки логічних схем.

На практиці застосовуються лише синхронні jk-трігері, тобто стани основних входів J і K враховуються лише у момент того, що тактує, наприклад по позитивному фронту імпульсу на вході синхронізації. На базі jk-трігера можливо побудувати d-трігер або Т-трігер. Як можна бачити в таблиці істинності jk-трігера, він переходить в інверсний стан кожного разу при одночасній подачі на входи J і K логічною 1. Ця властивість дозволяє створити на базі jk-трігера Т-трігер, об'єднавши входи J і K логічною 1. Ця властивість дозволяє створити на базі jk-трігера Т-трігер, об'єднавши входи J і K.

Алгоритм функціонування jk-трігера можна представити формулою

![]()