- •1.Основні логічні елементи

- •2.Математичний(логічний) опис логічних схем.

- •3.Правила і закони алгебри-логіки

- •Комбінаційні закони

- •Правило поглинання

- •Правило склеювання

- •4.Логічний елемент виключне або.Застосування

- •5.Мінімізація логічних схем

- •6.Карти Карно

- •7.Теореми де.Моргана

- •8.Синтез схем на логічних елементах

- •9.Карти Карно для більш ніж 5 змінних

- •10.Схема контролю на парність(непарність)

- •11.Швидкодія мікросхем,час перемикань елемента чи логічної схеми

- •12.Навантажувальна здатність мікросхем

- •13.Завадостійкість мікросхем

- •14.Комбінаційні послідовнісні схеми

- •15.Арифметичний суматор,додавання двійкових кодів

- •16.Півсуматор,повний суматор, таблиця станів

- •17.Віднімання двійкових кодів

- •18.Множення двійкових кодів.Блок-схема перемножувала кодів

- •19.Арифметично-логічні пристрої

- •20.Шифратори та дешифратори

- •21.Тригерні пристрої,класифікація,застосування

- •26.Двійкові лічильники,режими роботи лічильників

- •27.Регістри

- •28.Принципи побудови озп і пзп

- •29.Базові схеми ттл технології

- •30.Базові схеми кнон

- •31.Мультиплексори,Демультиплексори

- •32.Цифрові комператори(порівнювані)

16.Півсуматор,повний суматор, таблиця станів

Півсуматор є найпростішою рахунковою схемою.

Півсуматор може складати два двійкові числа.

Діють наступні правила:

Цифра, що додається, позначається змінною А. Другая цифра, що додається, позначається змінною В. Схема повинна мати два виходи. Вихід з вагою 2° назвемо Z, вихід з вагою 21 назвемо U (перенесення). Якщо двійкове число 0 ставиться у відповідність стану 0 і двійкове число 1 ставиться у відповідність стану 1, то виходить таблиця істинності на мал. 14.1.

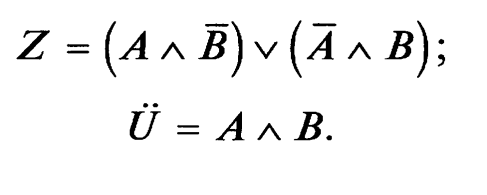

З таблиці істинності легко можуть бути визначені через нормальні форми АБО логічні функції півсуматора. Повні кон'юнкції виділені сірим на мал. 14.1. Півсуматор позначається знаком підсумовування (DIN 40900, частина 12).

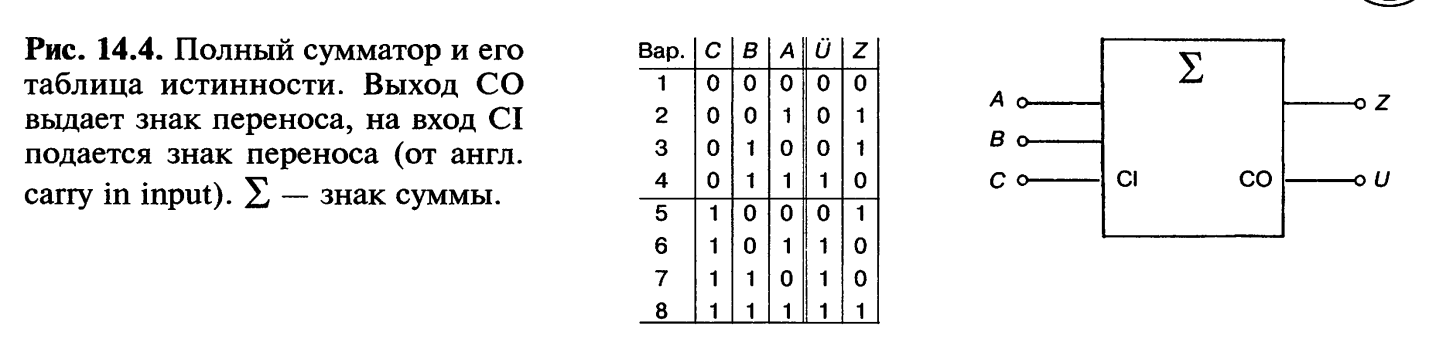

Для побудови повних суматорів потрібні схеми, які можуть складати три двійкові числа, оскільки при складанні двох двійкових чисел необхідно уміти складати перенесення.

Повним суматором називаєтса схема, яка може складати три двійкові числа

Схема повного суматора проектується по правилах синтезу схем (див. гл. 5). Повний суматор має три входи — для кожного двійкового числа, що складається. Назвемо їх А, В і С. Виходи називаються, як і в півсуматорі, Z і U.

17.Віднімання двійкових кодів

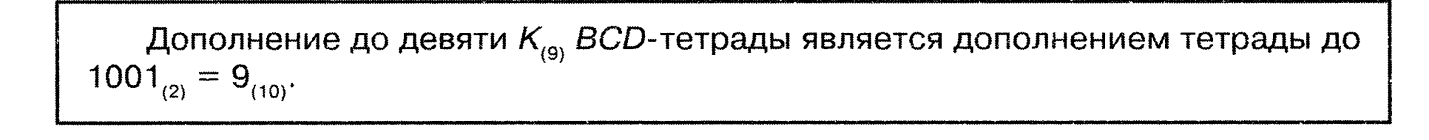

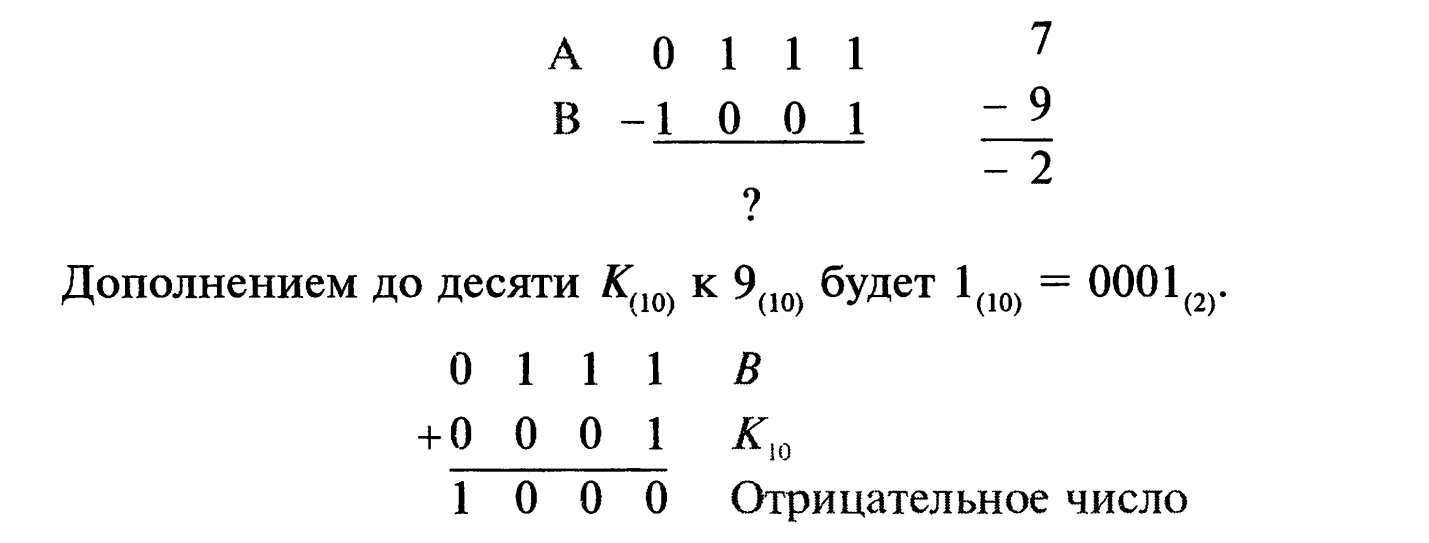

Віднімання в двійково-десятковому коді виробляється збільшенням доповнення.

Розрізняють доповнення до дев'яти і доповнення до десяти

Негативні BCD числа мають бути розпізнавані як негативні. Якщо при відніманні виходить негативне число, це повинно бути відразу зрозуміло. Потрібна особлива ознака.

Якщо при складанні точного доповнення до десяти зі ВСО-тетрадою не утворюється перенесення в 5-й розряд, то результат є негативним числом.

18.Множення двійкових кодів.Блок-схема перемножувала кодів

----------------------

19.Арифметично-логічні пристрої

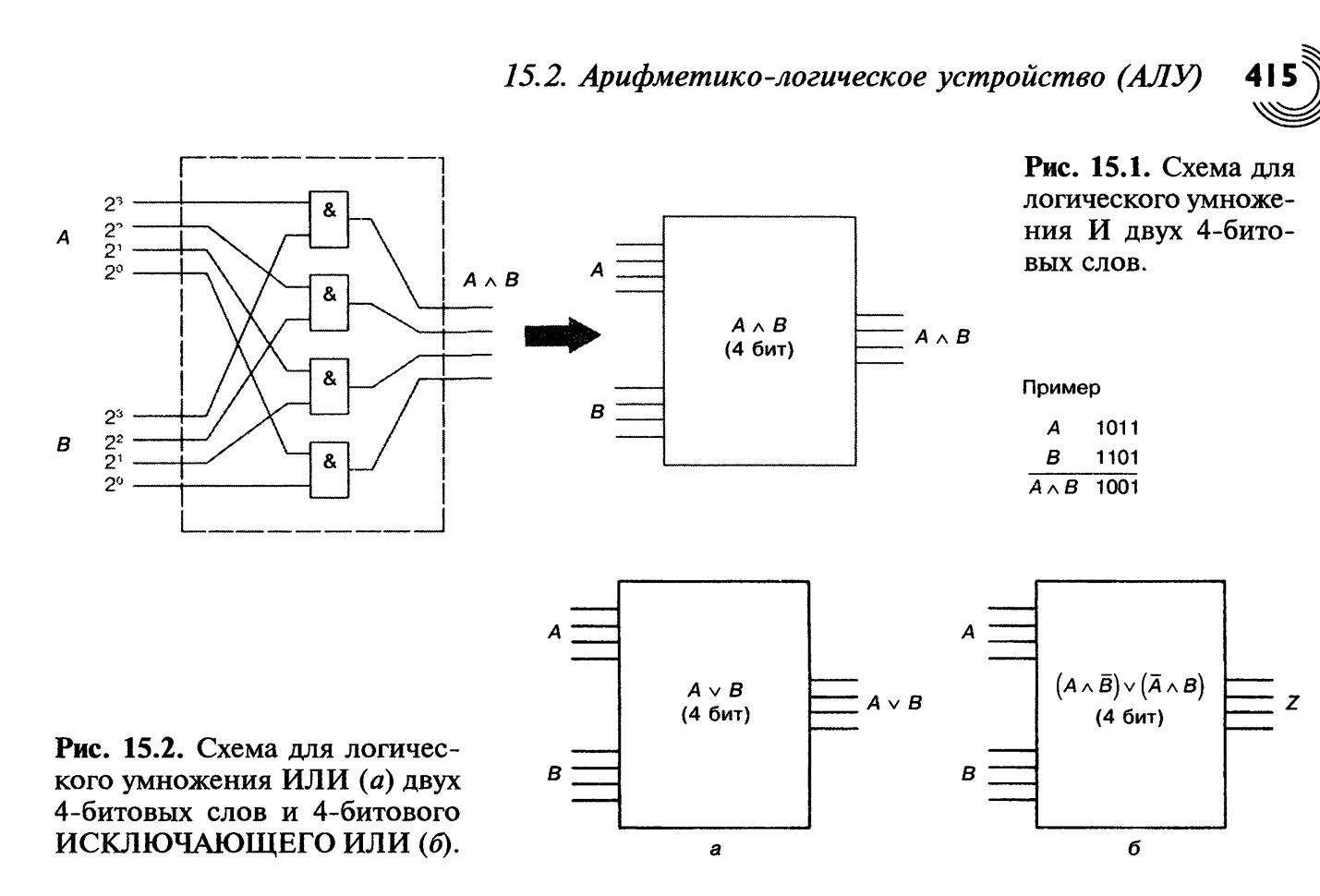

При розробці універсальних схем доцільно брати за основу розширені 4-бітові суматори-вичітателі (див. рис. 14.23), які були розглянуті в попередньому розділі. З цією схемою вхідні сигнали А і В за вибором можуть складатися і відніматися. Додатково потрібно, щоб з сигналами А і В можна було проводити операції:

логічного множення І;

логічного складання АБО;

ВИКЛЮЧАЄ АБО.

Схема для проведення 4-бітового І-множення показана на рис. 15.1. Також зображені схеми для 4-бітових АБО, і 4-бітових виключає Або, логічних функцій (рис. 15.2).

Схема, яка може складати і віднімати два N-бітових слова, а також проводити над ними операції логічного множення І, логічного складання АБО і виключає АБО, називається арифметико-логічний пристрій (АЛП).

20.Шифратори та дешифратори

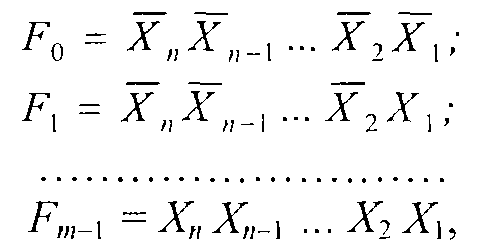

Дешифратором називається функціональний вузол комп'ютера, призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал тільки на одному зі своїх виходів. У загальному випадку дешифратор має n однофазних входів (іноді 2n парафазних) і m= 2n виходів, де n - розрядність (довжина) дешіфріруемого коду. Дешифратор з максимально можливим числом виходів m= 2n називається повним. Функціонування повного дешифратора описується системою логічних виразів виду:

де Х1 ……, Хn - вхідні двійкові змінні; F0, F1, … Fm-1 - вихідні логічні функції, які становлять минтерм (конституенти 1) n змінних. Індекс функції F1 визначає номер обраного виходу і відповідає десятковому еквіваленту вхідного коду. Вихід, на якому з'являється керуючий сигнал, називається активним. Якщо значення сигналу на активному виході з'являється лог. 1, то на інших пасивних виходах встановлюється лог. 0. Двійковий код, що включає завжди тільки одну одиницю, а решта - нулі, називається унітарною. Тому дешифратор є перетворювачем вхідного позиційного коду в унітарний вихідний код.

Шифратори класифікують за такими ознаками: 1.способу структурної організації - одноступінчасті (лінійні) і багатоступінчасті, в тому числі пірамідальні і прямокутні (матричні);

2.формату вхідного коду - двійкові, двійково-десяткові;

3.розрядності дешіфріруемого коду - 2, 3,…, n 4.формі подачі вхідного коду - з однофазними і парафазним входами;

5.кількістю виходів - повні і неповні дешифратори;

6.увазі вхідних стробирующих сигналів - в прямому чи інверсному значеннях; 7.типу використовуваних логічних елементів - І, НЕ, АБО, НЕ І, НЕ АБО і т. д.

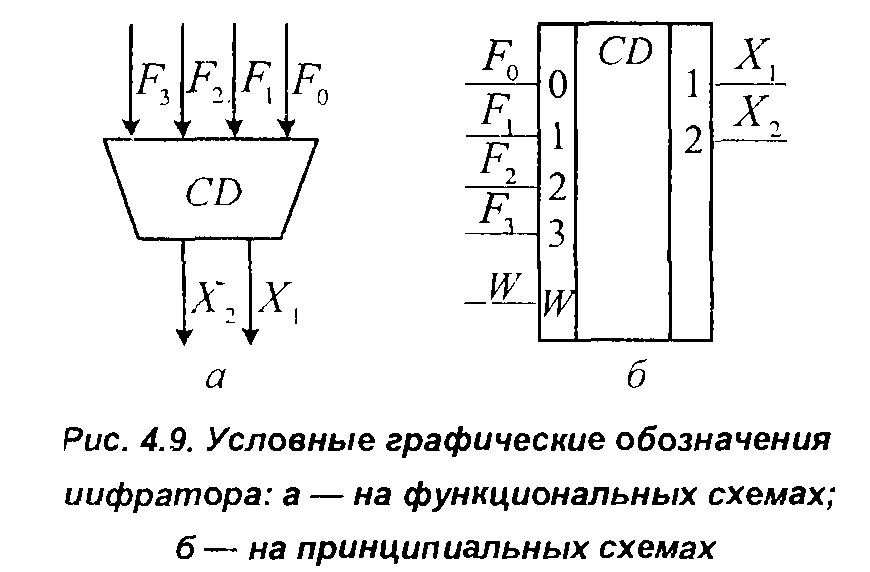

Шифратором називається функціональний вузол комп'ютера, призначений для перетворення вхідного m-розрядного унітарного коду у вихідний n-розрядний двійковий позиційний код. Двійкові шифратори виконують функцію, зворотну функції дешифратора. При активізації однієї з вхідних ліній дешифратора на його виходах формується код, що відображає номер активного входу. Повний двійковий шифратор має m= 2n входів і п виходів. Умовні графічні позначення шифраторів на схемах показані на рис. 4.9.

Функція шифратора позначається буквами CD (coder). Входи шифратора нумеруються послідовними десятковими цифрами 0, 1, m-1 а мітки виходів відображають ваги вихідних двійкових змінних 1,…. 2n-1 У цифрових пристроях шифратори використовуються для наступних операцій: перетворення унітарної вхідного коду у вихідний двійковий позиційний код; введення десяткових даних з клавіатури; вказівки старшої одиниці в слові; передачі інформації між різними пристроями при обмеженому числі ліній зв'язку.