- •1.Основні логічні елементи

- •2.Математичний(логічний) опис логічних схем.

- •3.Правила і закони алгебри-логіки

- •Комбінаційні закони

- •Правило поглинання

- •Правило склеювання

- •4.Логічний елемент виключне або.Застосування

- •5.Мінімізація логічних схем

- •6.Карти Карно

- •7.Теореми де.Моргана

- •8.Синтез схем на логічних елементах

- •9.Карти Карно для більш ніж 5 змінних

- •10.Схема контролю на парність(непарність)

- •11.Швидкодія мікросхем,час перемикань елемента чи логічної схеми

- •12.Навантажувальна здатність мікросхем

- •13.Завадостійкість мікросхем

- •14.Комбінаційні послідовнісні схеми

- •15.Арифметичний суматор,додавання двійкових кодів

- •16.Півсуматор,повний суматор, таблиця станів

- •17.Віднімання двійкових кодів

- •18.Множення двійкових кодів.Блок-схема перемножувала кодів

- •19.Арифметично-логічні пристрої

- •20.Шифратори та дешифратори

- •21.Тригерні пристрої,класифікація,застосування

- •26.Двійкові лічильники,режими роботи лічильників

- •27.Регістри

- •28.Принципи побудови озп і пзп

- •29.Базові схеми ттл технології

- •30.Базові схеми кнон

- •31.Мультиплексори,Демультиплексори

- •32.Цифрові комператори(порівнювані)

28.Принципи побудови озп і пзп

ОЗП(RAM)

Абревіатурою RAM позначаються оперативні пристрої, що запам'ятовують, на базі напівпровідникових технологій. Вони мають певну кількість елементів пам'яті. Кожен елемент пам'яті має встановлений об'єм пам'яті. Вона може приймати інформацію певної довжини. Кожен елемент пам'яті має індивідуальну адресу. По цих адресах здійснюється доступ до елементів пам'яті. Тобто RAM є пам'яттю з довільною вибіркою.

Позначення RAM є скороченням від Random Access Memory, англ. — пам'ять з довільною вибіркою. Елементи пам'яті вибираються по своїх адресах. У вічках зберігається записана інформація. Для виведення даних вічка також вибираються за своєю адресою. Прочитування даних не стирає вміст вічка. Якщо інформація більше не потрібна, вона може бути видалена, а в елемент пам'яті записана нова інформація.

ОЗП випускаються виключно у вигляді інтегральних мікросхем. Розрізняють статичні RAM і динамічні ОЗП. У статичному ОЗП вічка складаються з тригерів. Кожен біт записується в один з тригерів. У динамічному ОЗП для зберігання інформації використовуються внутрішні ємкості. Кожен біт записується в маленький конденсатор. Оскільки мають місце струми витоку, то виникає втрата заряду, тому ємкості періодично треба піддавати процесу регенерації (відновлення вихідних рівнів сигналу).

Статичні і динамічні ОЗП є енергозалежними. При від ключенії живлення інформація втрачається.

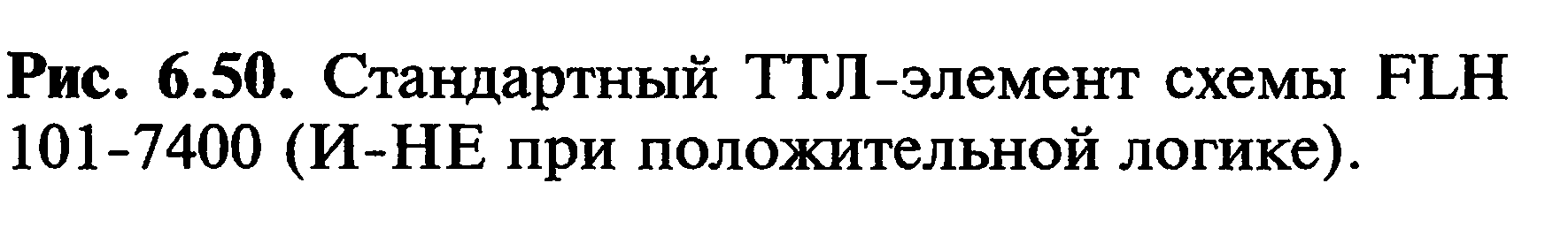

ПЗП(ROM)

ПЗП (ROM) містять невитирну і незмінну інформацію. Поняття ROM є скороченням від Read Only Memory. ПЗП можна порівняти з книгою. Занесена в неї інформація є доступною у будь-який час. Проте неможливо замінити або змінити інформацію. У ПЗП зберігають часто використовувані відомості, наприклад команди, програми і таблиці. В міру необхідності можуть бути лічені окремі елементи таблиці.

Для організації ПЗП застосовують двох типів елементів, що запам'ятовують. Елементи першого типа, що запам'ятовують, повинні завжди містити значення 1. Елементи другого типа, що запам'ятовують, повинні завжди містити значення 0.

Представлення даних в пам'яті і організація пам'яті ПЗП схожі на ОЗУ. Матриця, що запам'ятовує, складається з рядків і стовпців. Окремі елементи пам'яті вибираються адресацією (мал. 12.29).

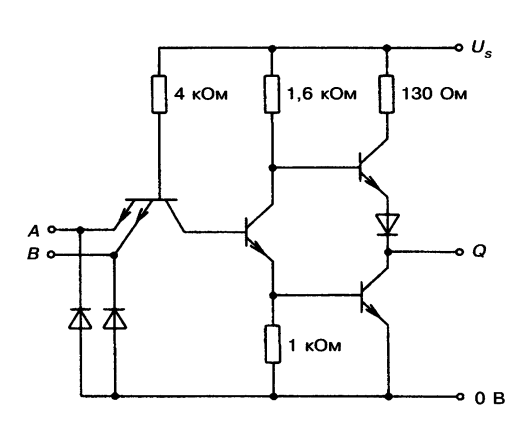

29.Базові схеми ттл технології

Скорочення ТТЛ позначає транзисторно-транзисторна логіка. Логічні елементи схем цього сімейства будуються виключно на біполярних транзисторах. Лише для зрушення рівня і відведення напруги застосовуються діоди. Опори служать як дільники напруги і обмежувачів струму.

ТТЛ-елементі виробляються виключно у вигляді інтегральних мікросхем.

Для ТТЛ-схем відкритий вхід прирівнюється до входу з високим H -уровнем.

Мультіеміттерний транзистор дуже швидко перемикається з прямого режиму в інверсний і навпаки, оскільки носіям зарядів в базі при перемиканні не потрібно розсмоктуватися.

ТТЛ-сімейство ділиться на ряд дрібніших підродин. Схеми окремих підродин розрізняються між собою перш за все вжитком потужності і швидкодією, а також перешкодостійкістю.

Підродину «стандартні ТТЛ» грає велику роль в схемотехніці. Типова схема із стандартних ТТЛ показана на мал. 6.50. Елемент виробляє при позитивній логіці логічну операцію І-НЕ.