Лабораторная работа 31 / Лабораторная работа3

.docСанкт-Петербургский государственный электротехнический университет «ЛЭТИ»

Кафедра САПР.

Отчет по лабораторной работе

по дисциплине «Микросхемотехника»

«Управление семисегментным дисплеем».

Выполнил:

Студент группы 4322

Факультет КТИ

Миненков Д.В.

Проверил: Фахми Ш.С.

СПб 2007.

Краткие теоретические сведенья

Логическое проектирование во многом определяет качество разрабатываемой схемы. Именно на этом этапе предусмотрена минимизация схемы – оптимизация количества логических элементов, реализующих схему устройства.

Наиболее простым и наглядным из методов минимизации является метод минимизирующих карт Карно и в частности метод диаграмм Вейча.

Основное ограничение метода – небольшое число входных сигналов (3-6).

Кроме этого метод предполагает специальное задание входных сигналов в виде таблицы - КАРТЫ.

Карта заполняется также как и таблица истинности:

-

«1» соответствует набору входных переменных, на, котором функция принимает значение «1»;

-

«0» для «нулевых» значений функции.

На рис 1 приведен пример заполнения карты.

_

А А

-

1

b

d

1

d

b

1

1

1

d

_ _

_ _

С С С

С С С

Рис. 1. Пример заполнения карты для функции

_ _ _ _ __ __ _

ABCD+ABCD+ABCD+ABCD+ABCD

Минимизация осуществляется на основании анализа расположения «единичных» элементов в карте.

Существует следующий набор правил минимизации:

-

Объединяются смежные элементы (в строке или столбце);

-

Объединяются элементы, занимающие крайнее положение (в строке или столбце).

При объединении работают следующие правила минимизации:

-

можно объединить 2, 4, 8, 16 и т.д. элементов;

-

при объединении происходит сокращение (минимизация) количества входных переменных. Правила сокращения числа переменных сведены в табл.1.

Табл.1.

|

№ п\п |

Число смежных элементов |

Число сокращаемых переменных |

Число сокращаемых элементов |

|

1 |

2 |

1 |

1 |

|

2 |

4 |

2 |

3 |

|

3 |

8 |

3 |

7 |

|

4 |

16 |

4 |

15 |

При этом наряду с сокращением количества входных переменных происходит сокращение числа самих элементов. Так для примера , приведенного на рис1. в ходе выполнения минимизации будет получена следующая функция:

_ _ __ _

ABC+ABC+ABCD.

Техническое задание.

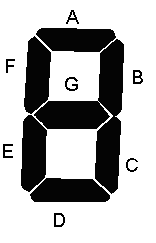

Синтезировать схему, реализующую работу семисегментного дисплея:

Рис. 1. Семисегментный дисплей.

Вариант задания и таблица истинности сведены в таблице 1:

Таблица 1.

|

Задание |

Входные сигналы |

Выходные сигналы |

|||||||||||

|

Символ |

|

№ |

x1 |

x2 |

x3 |

x4 |

ya |

yb |

yc |

yd |

ye |

yf |

yg |

|

0 |

X |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

1 |

X |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

2 |

X |

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

3 |

|

3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

4 |

X |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

5 |

|

5 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

6 |

X |

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

7 |

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

8 |

X |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

9 |

X |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

A |

|

10 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

B |

X |

11 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

C |

X |

12 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

D |

|

13 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

E |

|

14 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

F |

|

15 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1.Найдем функции, соответствующие СДНФ, для каждого сегмента:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

2. По функциям из пункта 1 составим минимизирующие карты Карно:

a b c

|

ab\cd |

00 |

01 |

11 |

10 |

|

ab\cd |

00 |

01 |

11 |

10 |

|

Ab\cd |

00 |

01 |

11 |

10 |

|

00 |

1 |

|

|

1 |

|

00 |

1 |

1 |

|

1 |

|

00 |

1 |

1 |

|

|

|

01 |

|

|

|

1 |

|

01 |

1 |

|

|

|

|

01 |

1 |

|

|

1 |

|

11 |

1 |

|

|

|

|

11 |

|

|

|

|

|

11 |

|

|

|

|

|

10 |

1 |

1 |

|

|

|

10 |

1 |

1 |

|

|

|

10 |

1 |

1 |

1 |

|

d e f

|

ab\cd |

00 |

01 |

11 |

10 |

|

ab\cd |

00 |

01 |

11 |

10 |

|

ab\cd |

00 |

01 |

11 |

10 |

|

00 |

1 |

|

|

1 |

|

00 |

1 |

|

|

1 |

|

00 |

1 |

|

|

|

|

01 |

|

|

|

1 |

|

01 |

|

|

|

1 |

|

01 |

1 |

|

|

1 |

|

11 |

1 |

|

|

|

|

11 |

1 |

|

|

|

|

11 |

1 |

|

|

|

|

10 |

1 |

1 |

1 |

|

|

10 |

1 |

|

1 |

|

|

10 |

1 |

1 |

1 |

|

g

|

ab\cd |

00 |

01 |

11 |

10 |

|

00 |

|

|

|

1 |

|

01 |

1 |

|

|

1 |

|

11 |

|

|

|

|

|

10 |

1 |

1 |

1 |

|

3 .В

результате анализа расположения единиц

на картах Карно получаим следующие

логические функции:

.В

результате анализа расположения единиц

на картах Карно получаим следующие

логические функции:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

4. Таким образом, задача сводится к проектированию схемы, реализующей функции, полученные в п.2. Для этого воспользуемся одним из языков описания систем на кристалле – VHDL. Будем использовать САПР Xilinx ISE 9.1.

Создадим новый проект ( File – New Project) со следующими свойствами:

Рис. 1. Свойства проекта.

Далее, щелкнув в области Sources правой кнопкой мыши, создаём новый файл (New Source…), выбрав из предлагаемого списка VHDL - Module.

Напишем следующий код:

entity vh is

Port ( X : in STD_LOGIC_VECTOR (3 downto 0);

Y : out STD_LOGIC_VECTOR (6 downto 0));

end vh;

architecture Behavioral of vh is

begin

process(X)

begin

case X is

when "0000" =>Y<="1111110";

when "0001" => Y<="0110000";

when "0010" => Y<="1101101";

when "0011" => Y<="0000000";

when "0100" => Y<="0110011";

when "0101" => Y<="0000000";

when "0110" => Y<="1011111";

when "0111" => Y<="0000000";

when "1000" => Y<="1111111";

when "1001" => Y<="1111011";

when "1010" => Y<="0000000";

when "1011" => Y<="0011111";

when "1100" => Y<="1001110";

when "1101" => Y<="0000000";

when "1110" => Y<="0000000";

when "1111" => Y<="0000000";

when others => null;

end case;

end process;

end Behavioral;

Для проверки правильности написания, воспользуемся инструментом Check Syntax из группы Synthesize в области Processes. Если на вкладке Console области Transcript в нижней части экрана нет сообщений об ошибках, можно переходить к построению временной диаграммы.

Временная диаграмма показывает зависимость сигнала на выходе схемы от сигналов на входе и служит для проверки соответствия схемы требованьям, указанным в техническом задании.

Чтобы построить ВД, на вкладке Source области Sources щелкнем правой кнопкой по созданному VHDL-файлу, выберем пункт меню «New source…» и, выбрав из предложенного списка “Test Bench WaveForm” зададим значения входных сигналов. После сохранения, выделив файл с ВД в области Sources, выберем в области Processes действие Simulate Behavioral Model. Полученная Временная диаграмма на рисунке 3:

Рис. 3. Временная диаграмма.

Из сравнения временной диаграммы с таблицей истинности видно, что схема собрано правильно.