- •Введение

- •Преобразователи

- •1.1. Назначение и виды цифро- аналоговых преобразователей

- •1.2. Основные параметры цап

- •1.3. Принципы построения цап

- •Выходное напряжение для схемы, приведенной на рис.1.3, определяется формулой

- •Напряжение на выходе операционного усилителя определяется выражением

- •1.4. Серийные микросхемы цап

- •Характеристики интегральных микросхем цап

- •Контрольные вопросы:

- •Преобразование сигналов

- •2.1. Принципы аналого-цифрового преобразования сигналов

- •Для сигналов с ограниченным спектром теорема отсчетов имеет вид

- •2.2. Основные характеристики ацп

- •2.3. Принципы построения ацп

- •Контрольные вопросы:

- •3.4. Представление дробных чисел в двоичном коде с

- •3.5. Представление чисел в двоичном коде с плавающей

- •3.2. Знаковые обратные двоичные коды

- •3.3. Знаковые дополнительные двоичные коды

- •3.4. Представление дробных чисел в двоичном коде с фиксированной запятой

- •3.5. Представление чисел в двоичном коде с плавающей запятой

- •3.6. Запись десятичных чисел

- •3.7. Суммирование двоично- десятичных чисел

- •3.8. Арифметико-логические устройства

- •4.1. Функции микропроцессорных систем и микро-эвм

- •4.2. Принципы построения микропроцессорных систем и

- •4.2. Принципы построения микропроцессорных систем и микро-эвм

- •4.3. Структура и функционирование микропроцессорных систем

- •4.4. Микроконтроллеры

- •4.5. Микропроцессорные комплекты и микро-эвм

- •(Intel 8085a)

- •5.3. Синхронизация и последовательность действий мп

- •5.4. Система прерываний

- •5.2. Блок регистров

- •5.3. Синхронизация и последовательность действий мп

- •5.4. Система прерываний

- •6. Команды микропроцессора

- •7.1. Понятие системной шины микропроцессора

- •7.2. Адресное пространство микропроцессорного

- •7.3. Способы расширения адресного пространства

- •7.2. Адресное пространство микропроцессорного устройства

- •7.3. Способы расширения адресного пространства микропроцессора

- •8. Параллельный порт

- •9. Последовательный порт

- •9.1. Синхронный последовательный порт

- •9.2. Асинхронный последовательный порт

- •9.1. Синхронный последовательный порт

- •9.2. Асинхронный последовательный порт

- •10. Статические оперативные запоминающие устройства

- •11. Постоянные запоминающие устройства

- •11.1. Пзу на основе мультиплексора

- •11.2. Масочные пзу

- •11.3. Программируемые пзу

- •11.4. Пзу с ультрафиолетовым стиранием

- •11.5. Электрически стираемые ппзу

- •11.6. Flash - пзу

- •12. Подключение внешних устройств к микропроцессору

- •13. Шинные формирователи

- •14. Принципы построения таймеров

3.3. Знаковые дополнительные двоичные коды

От перечисленных недостатков свободны дополнительные коды. Эти коды позволяют непосредственно суммировать положительные и отрицательные числа, не анализируя знаковый разряд и при этом получать правильный результат. Все это становится возможным благодаря тому, что дополнительные числа являются естественным кольцом чисел, а не искусственным образованием как прямые и обратные коды. Кроме того, немаловажным является то, что вычислять дополнение в двоичном коде чрезвычайно легко. Для этого достаточно к обратному коду добавить 1:

Рис. 3.4.

Диапазон чисел, которые можно записать таким кодом: -128 ... +127. Для шестнадцатиразрядного кода этот диапазон будет: -32768 .. +32767. В восьмиразрядном процессоре для хранения такого числа используется две ячейки памяти, расположенные в соседних адресах.

В обратных и дополнительных кодах наблюдается интересный эффект, который называется эффект распространения знака. Он заключается в том, что при преобразовании однобайтного числа в двухбайтное достаточно всем битам старшего байта присвоить значение знакового бита младшего байта. То есть для хранения знака числа можно использовать сколько угодно старших бит. При этом значение кода совершенно не изменяется.

Использование для представления знака числа двух бит предоставляет интересную возможность контролировать переполнения при выполнении арифметических операций.

Рассмотрим несколько примеров.

Пример 3.1. Просуммируем числа 12 и 5:

В этом примере видно, что в результате суммирования получается правильный результат. Это можно проконтролировать по флагу переноса C, который совпадает со знаком результата (действует эффект распространения знака).

Пример 3.2. Просуммируем два отрицательных числа -12 и -5:

В этом примере флаг переноса C тоже совпадает со знаком результата, то есть переполнения не произошло и в этом случае

Пример 3.3. Просуммируем положительное и отрицательное числа -12 и 5:

В этом примере при суммировании положительного и отрицательного числа автоматически получается правильный знак результата. В данном случае знак результата отрицательный. Флаг переноса совпадает со знаком результата, поэтому переполнения не было.

Пример 3.4. Просуммируем положительное и отрицательное числа 12 и -5:

В данном примере знак результата положительный. Флаг переноса совпадает со знаком результата, поэтому переполнения не было и в этом случае.

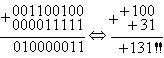

Пример 3.5. Просуммируем числа 100 и 31:

В этом примере видно, что в результате суммирования произошло переполнение восьмибитовой переменной, т.к. в результате операции над положительными числами получился отрицательный результат. Однако если рассмотреть флаг переноса, то он не совпадает со знаком результата. Эта ситуации является признаком переполнения результата и легко обнаруживается при помощи операции "исключающее ИЛИ" над старшим битом результата и флагом переноса C. Большинство процессоров осуществляют эту операцию аппаратно и помещают результат во флаг переполнения OV.

В этом примере результате операции над отрицательными числами в результате суммирования произошло переполнение восьмибитовой переменной, т.к. получился положительный результат. И в этом случае если рассмотреть флаг переноса C, то он не совпадает со знаком результата. Отличие от предыдущего случая только в комбинации этих бит. В примере 5 говорят о переполнении результата (комбинация 01), а в примере 6 об антипереполнении результата (комбинация 10).