- •Содержание

- •Реферат

- •Введение

- •Постановка задачи

- •Операционный автомат

- •1.2 Управляющий автомат типа п с естественной адресацией

- •1.3 Алгоритмы выполняемых операций

- •1.3.1 Алгоритм умножения целых двоичных беззнаковых чисел, начиная с младших разрядов множителя, со сдвигом суммы частичных произведений вправо:

- •1.3.2 Алгоритм деления целых двоичных беззнаковых чисел без восстановления остатка:

- •1.4 Объединенная граф схема алгоритма

- •2. Проектирование операционного автомата

- •3. Проектирование управляющего автомата

- •4. Проектирование процессорного модуля

- •4.1 Схема объединения операционного и управляющего автоматов

- •4.2 Результаты тестирования

1.3 Алгоритмы выполняемых операций

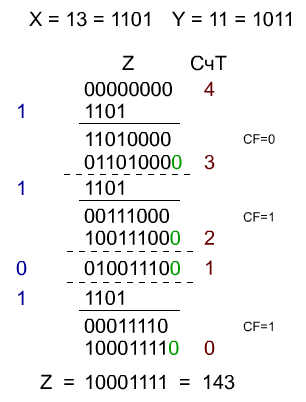

1.3.1 Алгоритм умножения целых двоичных беззнаковых чисел, начиная с младших разрядов множителя, со сдвигом суммы частичных произведений вправо:

1. Исходное значение суммы частичных произведений (СЧП) принимаем равным 0 и значение счетчика тактов (СчТ) устанавливаем равным n - количеству разрядов множимого.

2. Анализируется младшая разрядная цифра множителя. Если она равна 1, то к СЧП прибавляется множимое совмещенное по старшим разрядам. Если анализируемый разряд равен 0, то сложение не производится.

3. Производится сдвиг множителя и СЧП вправо на один разряд. Содержимое СчТ уменьшается на 1.

4. Анализируется содержимое СчТ. Если оно не равно 0, то переход к п. 2, если равно, то к п. 5.

5. Умножение закончено, младшая часть произведения находится на месте множителя, а старшая - на месте СЧП.

Рис. 1.3 Умножения целых двоичных беззнаковых чисел, начиная с младших разрядов множителя, со сдвигом суммы частичных произведений вправо

1.3.2 Алгоритм деления целых двоичных беззнаковых чисел без восстановления остатка:

1. Исходное значение частного полагается равным 0. Счетчику тактов (СчТ) присваивается значение n. Исходное значение частичного остатка полагается равным старшим n разрядам делимого.

2. Выполняется пробное вычитание делителя из исходного значения частичного остатка. Если результат больше 0, то это указывает на то, что частное будет превышать n-разрядную сетку. Выполняется прерывание. Если результат меньше 0, то можно выполнять деление.

3. Частичный остаток удваивается путем сдвига на 1 разряд влево. При этом в освобождающийся при сдвиге младший разряд заносится очередная цифра делимого.

4. Из частичного остатка вычитается делитель, если остаток больше 0, или к частному остатку прибавляется делитель, если остаток меньше 0.

5. Сдвигается частное, в младший разряд которого заносится очередная цифра частного: 1 - если остаток больше 0, и 0 - если остаток меньше 0. Счетчик тактов уменьшается на 1.

6. Пункты 3-5 последовательно выполняются для получения всех цифр частного (пока значение счетчика тактов не станет равно 0).

7. Если полученный последний остаток от деления отрицательный, то восстанавливается предыдущий положительный остаток, который и будет остатком от деления.

Рис 1.4 Деления целых двоичных беззнаковых чисел без восстановления остатка

1.4 Объединенная граф схема алгоритма

Рис 1.5 Объединенная ГСА

2. Проектирование операционного автомата

1) Список операций:

y1: A (2n : 0) : = 0. D1 (2n-1 : 0)

y2: B (n : 0) : = 0. D2 (n-1 : 0)

y 3:

A (2n : n) : = A (2n : n) + B (n : 0) + 1

3:

A (2n : n) : = A (2n : n) + B (n : 0) + 1

y4: TgA : = A (2n)

y5: A (2n :0) : = L1 (A (2n -1 : 0). 0)

y6: C (n-1 : 0) : = 0

y7: CnT (m-1 : 0) : = n

y8: A (2n :n) : = A (2n :n) + B (n : 0)

y 9:

C (n-1 : 0) : = L1 (C (n-2 : 0). A (2n))

9:

C (n-1 : 0) : = L1 (C (n-2 : 0). A (2n))

y10: CnT : = CnT-1

y11: R1 (n-1 : 0) : = C (n-1 : 0)

y 12:

R2 (n-1 : 0) : = A (2n-1 : n)

12:

R2 (n-1 : 0) : = A (2n-1 : n)

y13: IRQ1 : = 1

y14: IRQ2 : =1

y15: A (n+1 : 0) : = 00.D1 (n-1 : 0)

y16: B (n-1 : 0) : = D2 (n-1 : 0)

y17: A (n+1 : 0) : = L1 (A (n : 0 ). 0)

y 18:

C (n+1 : 0) : = C (n+1 : 0) + A (n+1 : 0)

18:

C (n+1 : 0) : = C (n+1 : 0) + A (n+1 : 0)

y19: C (n+1 : 0) : = C (n+1 : 0) + A (n+1 : 0) + 1

y20: B (n-1 : 0) : = R2 (C (1 : 0). B (n-1 : 2))

y21: C (n+1 : 0) : = R2 ( C (n+1). C (n+1). C (n+1 : 2))

y22: R (2n-1 : 0) : = C (n-1 : 0). B (n-1 : 0)

x1: F=1

x2: B=0

x3: A(2n)

x4: TgA

x5: CnT = 0

x6:

![]()

x7:

![]()

x8:

![]()

x9: C (n+1)

2) A(2n:0), B(n:0), C(n+1), CnT(m-1:0), TgA, R(2n-1:0), R1(n-1:0), R2(n-1:0), IRQ1,IRQ2

3) YA = {y1, y3, y5, y8, y15, y17};

YB = {y2, y16, y20} ;

YC = {y6, y9, y18, y19, y21} ;

YCnT = {y7, y10} ;

YTgA = {y4} ;

YR = {y22} ;

YR1= {y11} ;

YR2= {y12} ;

YIRQ1 = {y13} ;

YIRQ2 = {y14}

4) KA1 = {y1, y15} ; KA2 = {y3, y8} ; KA3 = {y5}; KA4={y17} ; KB1 = {y2, y16} ;

KB2 ={y20} ; KC1 = {y18, y19} ; KC2 = {y6} ; KC3 = {y9} ; KC4 = {y21} ;

5)

![]() A:= F1,

где

A:= F1,

где

![]()

![]() А:= A+F2+F3,

где

А:= A+F2+F3,

где

![]()

![]()

![]() B:= F4,

где

B:= F4,

где

![]()

![]() C:= C+F5+F6,

где

C:= C+F5+F6,

где

![]()

![]()

Рис. 2.1 Структурная схема операционного автомата I