- •Студент __________________ учебная группа___________ дата _____________

- •Задание 2. Логические элементы

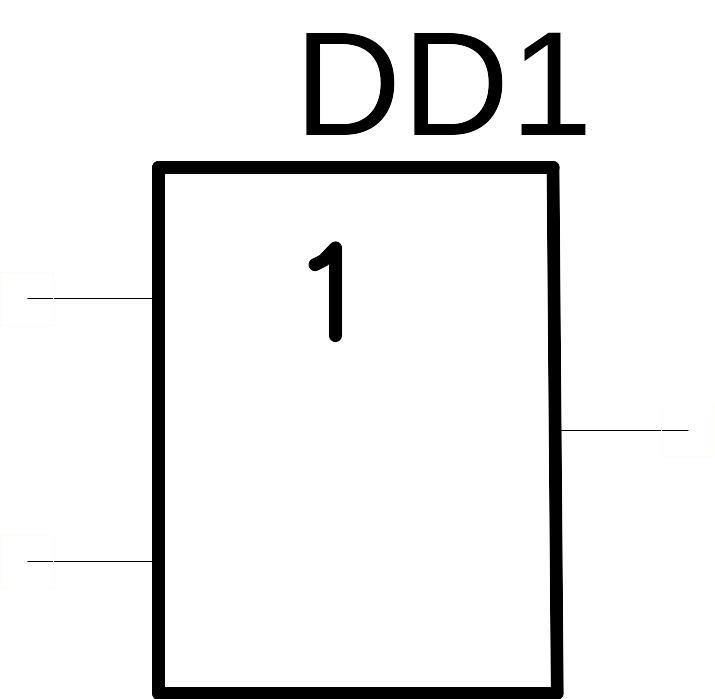

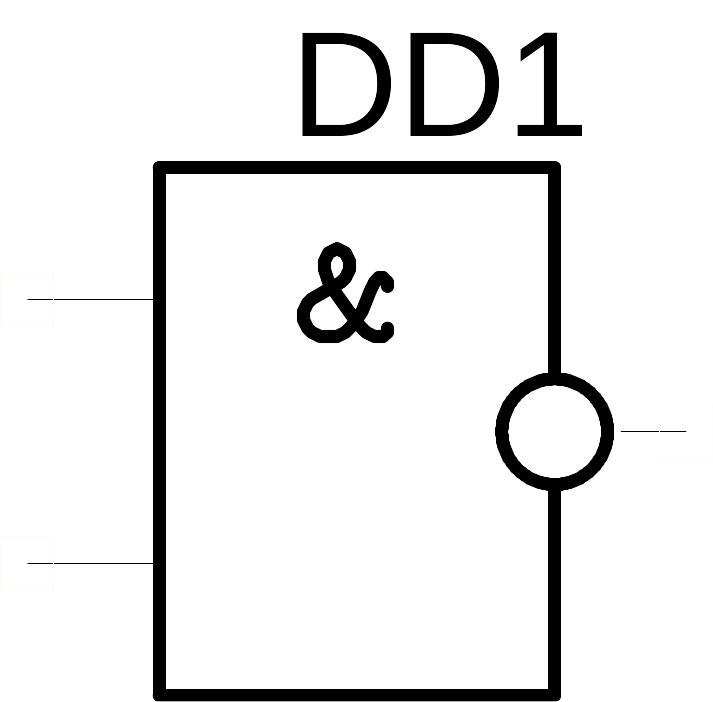

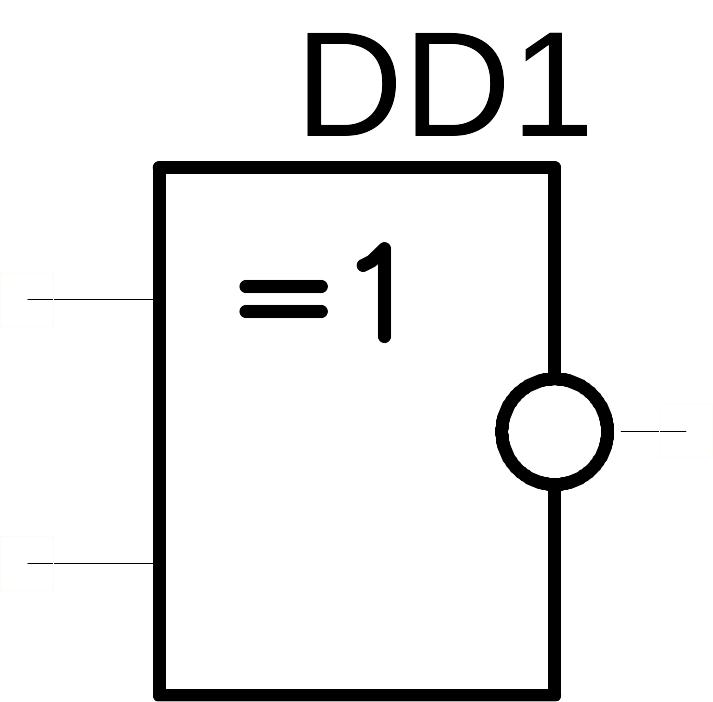

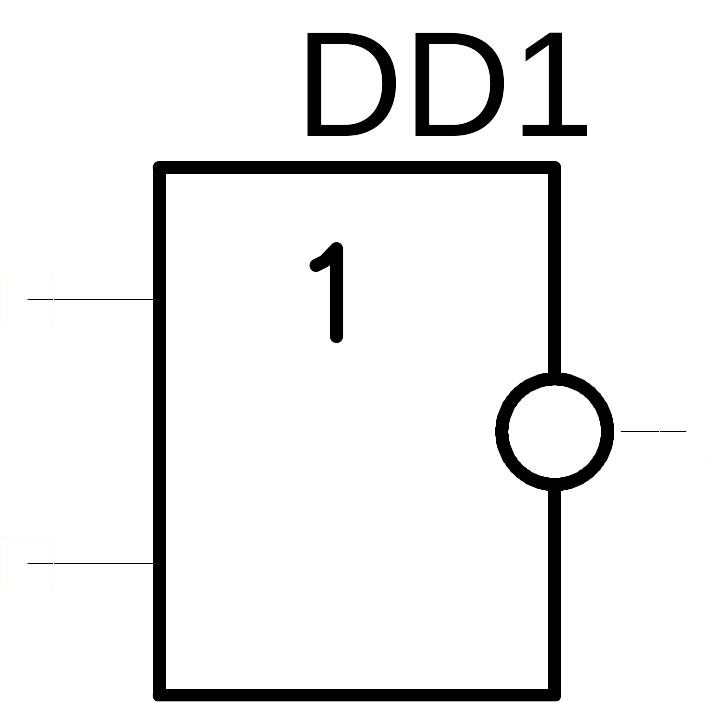

- •2.1. У заданного условным графическим обозначением логического элемента подписать выводы, заполнить его таблицу истинности, привести логическое выражение выполняемой им операции.

- •Задание 3. Комбинационные устройства

- •Задание 4. Триггеры.

- •Задание 5. Устройства накапливающего типа

Задание

для подготовки к экзамену по дисциплине «Схемотехника ЭВМ»

Структура задания приведена в Приложении № 1.

В заданиях указаны устройства и необходимые для работы исходные данные.

Всего пять заданий.

Критерии оценки:

- пять правильно, полно, аккуратно выполненных заданий – отлично;

- четыре … - хорошо;

- три … - удовлетворительно;

- менее трех – неудовлетворительно.

Задание считается выполненным, если оно выполнено более, чем на две трети (2/3)!

При возникновении вопросов - задавать персонально в институте.

Групповая консультация будет проведена согласно графика сдачи сессии.

Успехов в подготовке и сдаче.

С уважением, Л.В.Стулов

Приложение № 1. Структура экзаменационной работы

Экзамен

по дисциплине «Схемотехника ЭВМ»

Студент __________________ учебная группа___________ дата _____________

Вариант № Х

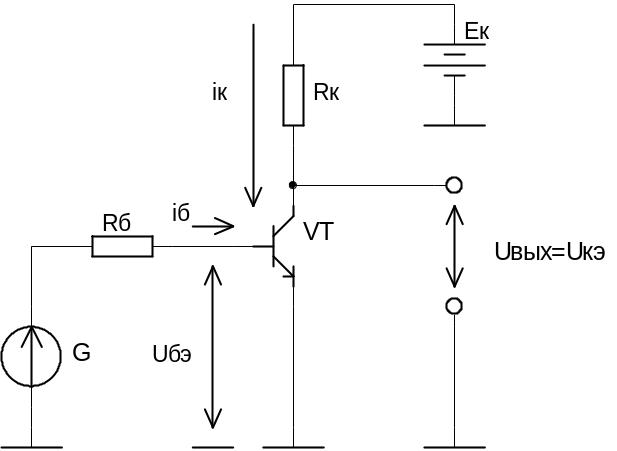

Задание 1. Транзисторный ключ с общим эмиттером

Заполнить временные диаграммы функционирования транзисторного ключа с общим эмиттером. Показать и подписать этапы переключения (tпвкл, tвкл, tпвыкл, tвыкл). обозначить значения, отмеченные «?».

|

|

Рассчитать значения (Iбн, Iкк, Iкн, S, Uкэ0, Uкэ1, Umвых – заданы два параметра) в состоянии (насыщения, выключения), длительность этапов переключения (tп.вкл., tвкл., tп.вкл., tвкл – заданы два параметра) если известны значения:

UmG, В |

Rб, кОм |

Uбэо, В |

Uбэн, В |

|

Uкэн, В |

Iкб0, мкА |

Rк, кОм |

Ек, В |

п, мкс |

к, мкс |

р, мкс |

|

|

|

|

|

|

|

|

|

|

|

|

Расчеты длительности этапов переключения пояснить временными диаграммами

Название этапа:____________________ |

Название этапа:___________________ |

|

|

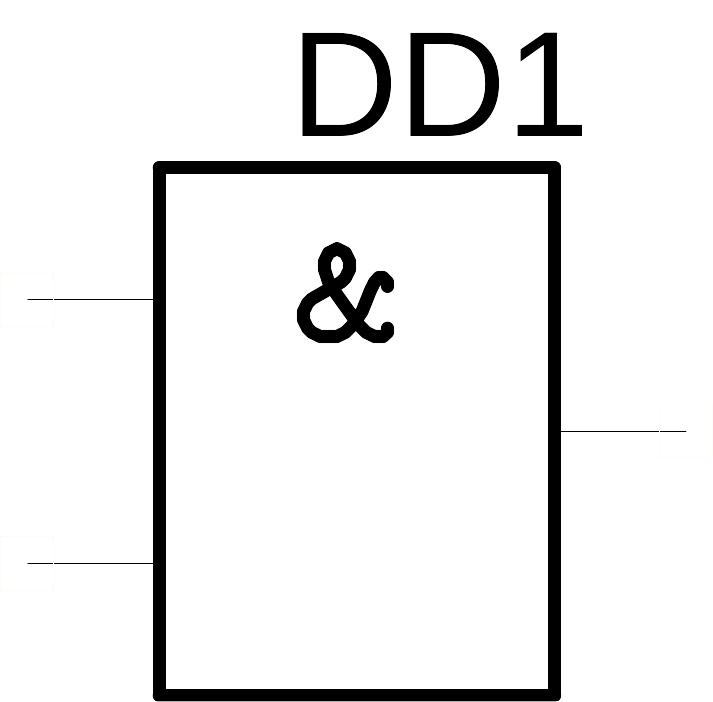

Задание 2. Логические элементы

2.1. У заданного условным графическим обозначением логического элемента подписать выводы, заполнить его таблицу истинности, привести логическое выражение выполняемой им операции.

Могут быть заданы элементы

|

|

|

|

|

|

|

|

У =

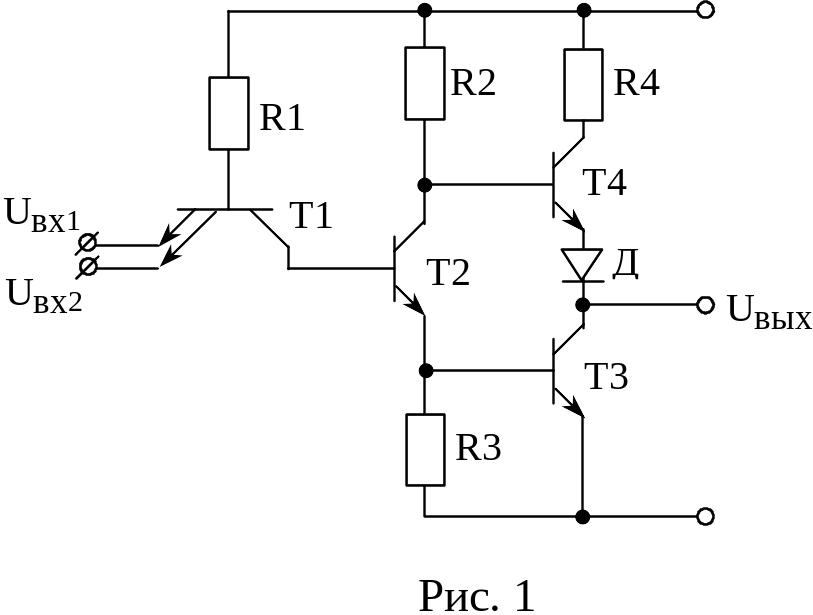

2.2. Для логического элемента 2И-НЕ заполнить временные диаграммы. В заданный (пунктирной линией) момент времени определить состояния транзисторов; на схеме логического элемента отобразить пути протекания токов, направление протекания выходного тока и уровень выходного напряжения.

|

Временные диаграммы

|

T1- ; T2- ;Т3- ;Т4-

(

открыт

(О), закрыт (З), активный (АР), активный

инверсный (АИР) режим)

открыт

(О), закрыт (З), активный (АР), активный

инверсный (АИР) режим)

Iout - (Вытек., Втек);

Uout – (U1, U0, значение в В)

По заданным исходным данным рассчитать (Uвх1, Uвх0; UК, UЭ, UБ, Iк, Iб, Iэ транзисторов VT1, VT2, VT3, VT4) (задано 2 параметра) при (Uвых0, Uвых1). Еип = 5 В. При расчетах состояния входов считать одинаковыми.

Исходные данные для расчетов:

Uвх1, В |

Uвх0, В |

Uбэн, В |

Uкэн, В |

b |

bi |

R1, кОм |

R2, кОм |

R3, кОм |

R4, кОм |

Iвых1, мА |

|

|

|

|

|

|

|

|

|

|

|