- •Глава 9 : Функциональная верификация

- •9.1 Введение

- •V диаграмма разработки, верификации, и интеграции.

- •9.2.1 Верификация ступени проектирования. Designer-level verification

- •9.2.2 Unit-level verification верификация уровня элементов

- •9.2.3 Core-level verification. Верификация уровня ядра.

- •9.2.4 Chip-level verification Верификация уровня ядра

- •9.2.5 System-/board-level verification верификация уровня системы/платы.

V диаграмма разработки, верификации, и интеграции.

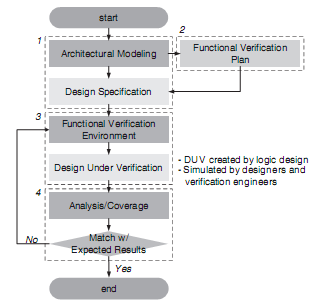

Рисунок 9.3

Generic design verification flow.

flow starting from the system/board level, through the chip and core/unit levels, to the designer level.Общий поток верификации [Palnitkar 2003a] для каждого уровня состоит из нескольких шагов, как показано на рисунке 9.3. A generic verification flow for each level consists of several steps, as shown in Figure 9.3. На шаге 1, архитекторы должны подготовить техническое задание модели, для лучшей архитектуры, на основе анализа результата моделирования.In Step 1, architects need to prepare a design specification for the best architecture on the basis of analysis of simulation result.На шаге 2 план функциональной верификации создан для определения основных параметров, используемых в среде функциональной верификации, в дальнейшем. In Step 2, a functional verification plan is created to define the basic parameters that are used later in the functional verification environment.Тестовые вектора и стенды либо сгенерированны вручную, либо автоматически инструментами во время шага 3. Test vectors and testbenches are either generated manually or automatically by tools during Step 3.Эмулятор программного обеспечения применяет эти вектора и тестовые стенды на проект под контроль(DUV) и собирает связанную информацию после моделирования.A software simulator applies these test vectors and testbenches to the design under verification (DUV) and collects the related information after simulation.На шаге 4, выходящие данные анализируются и проверяются и сопоставляются с ожидаемыми данными для расчёта покрытия верификации. In Step 4, the output data are analyzed and checked against the expected results to calculate verification coverage. Если цель желаемого покрытия не достигнута, шаг 3 повторяется для генерации большего числа тестовых векторов, чтобы улучшить покрытие. If the desired coverage goal is not achieved, Step 3 is repeated to generate more test vectors to improve the coverage.После того, как цель покрытия достигнута, дополнительные шаги моделирования устройств, эмуляции и основанной на проверке верификации могут быть применены для дальнейшего совершенствования проверки качества и снижения риска нужды в будущей разработке с нуля. After the coverage goal is met, optional steps of hardware-accelerated simulation, emulation, and assertion-based verification could be applied to further improve verification quality and to reduce the risk of needing a future re-spin.

9.2.1 Верификация ступени проектирования. Designer-level verification

При внедрении сверху вниз показанном на рисунке 9.2, уровень проектирования - низший уровень, который определяет наименьшие из RTL модулей, такие как арбитер или первым пришел - первым обслужен (FIFO), за что проектировщик несёт ответственность в проекте.In the top-down implementation flow shown in Figure 9.2, the designer level is the lowest level that defines the smallest of the RTL modules such as an arbiter or a first-in first-out (FIFO) that one designer can be in charge of in a project.Блоки уровня проектирования часто проверяются индивидуально, для подстраховки , что базовая функциональность блоков, взятая из системной спецификации, понята дизайнером и корректно внедрена. Designer-level blocks are usually verified individually to ensure that the basic functionalities of the blocks understood by the designer from the system specification are correctly implemented. Если задания вовлечены в верификацию, блок уровня проектирования не требует взаимодействия с другими блоками, дизайнеру даётся полный контроль над блоком , и таким образом ожидается высокий стандарт верификации на этом уровне. As the tasks involved in verifying a designer-level block do not require interaction with other blocks, the designer is given full control of the block, and thus a high standard of verification is expected at this level. В ранней стадии разработки проекта, функциональность блока не будет полностью исправлена и, вероятно, будет часто изменяться. During the early phase of a design project, the functionality of a block would not be completely fixed and likely will be modified frequently. Для примера, часть функциональности блока может перемещаться поперёк интерфейса к другим блокам, для лучшей оптимизации элементов/ядра/чипа. For example, part of a block’s functionality may need to move across the interface to other blocks for better unit/core/chip optimization.Следовательно,это не редкость - повторять процесс верификации уровня проектирования несколько раз.It is, therefore, not uncommon to repeat the designer-level verification process multiple times.Разнообразные техники верификации доступны на этом уровне. A variety of verification techniques are available at this level. Разработка испытательного стенда относительно легка , потому что входы и выходы блока

рассматриваются в качестве основных входов и выходов на данном этапе.Testbench development is relatively easy because the block inputs and outputs are treated as primary inputs and outputs at this stage. Проектировщики часто исследуют большую или даже всю область входных значений целевого блока , благодаря моделированию.The designers often explore most of or even the entire input space of the target block by simulation.Формальные методы, такие как проверка имущества также могут быть применены относительно легко на данном уровне, из-за малого размера проекта. Formal methods such as property checking can also be applied relatively easily at this level because of the small design size.Очень важно отметить, что для верификации уровня проектирования, главная проблема не в верификации блока как отдельной модели, а верифицировать блок в контексте окружающей среды, в которую он будет помещён. It is important to note that, for designer-level verification, the main challenge is not in verifying the block itself as an independent design, but in verifying the block in the context of the environment in which it will be placed. Для примера, имущества не могут быть точно проверены, если блок работает независимо.For example, a property may not be verified as always true if the block operates independently. Однако, при определенных ограничениях, накладываемых окружающей средой вокруг блока, имущество может стать точным всегда. However, under specific constraints imposed by the environment surrounding the block, the property could become always true.

Установление должного ограничения среды для верификации уровня проектирования, тем не менее важная(и зачастую, не тривиальная) задача.Establishing proper environmental constraints for designer-level verification is, therefore, an important (and usually not trivial) task.