Lektsii_mikroprotsessory

.pdf21

Аналоговые процессоры – это процессоры предназначенные для работы с данными, представленными в аналоговой форме. Для преобразования в цифровую форму входных данных такие процессоры имеют в своем составе аналогоцифровые преобразователи (АЦП). А для преобразования в аналоговую форму выходных данных такие процессоры имеют в своем составе цифроаналоговые преобразователи (ЦАП). В остальном аналоговые процессоры аналогичны цифровым.

Классификация микропроцессоров по характеру временной организации

Различают синхронные и асинхронные процессоры.

Синхронные процессоры – это процессоры, работающие в режиме синхронного обмена с устройствами шины, когда начало и завершение операций обмена процессора с устройствами шины никак не связаны с ответными сигналами готовности этих устройств, а определяется лишь синхроимпульсами вырабатываемыми процессором. Предполагается, что интервал времени, задаваемый синхроимпульсами является достаточным для восстановления готовности устройств шины.

Асинхронные процессоры – это процессоры, работающие в режиме асинхронного обмена с устройствами шины. Процессор в таком случае стробирует начало обмена своим сигналом и переключается на ожидание ответного сигнала готовности от устройства шины, к которому процессор обратился для обмена. Только когда процессор примет сигнал готовности, только тогда он продолжит обмен. Таким образом время операции обмена по шине зависит от быстродействия устройства, с которым процессор обменивается данными.

Классификация микропроцессоров по количеству выполняемых программ

По количеству выполняемых программ различают одно- и многопрограммные микропроцессоры.

Воднопрограммных микропроцессорах выполняется только одна про-

грамма. Переход к выполнению другой программы происходит после завершения текущей программы.

Вмного- или мультипрограммных микропроцессорах одновременно выполняется несколько (обычно несколько десятков) программ. Организация мультипрограммной работы микропроцессорных управляющих систем позволяет осуществить контроль за состоянием и управлением большим числом источников или приемников информации.

Библиографический список к теме 3

1.Угрюмов Е. П. Цифровая схемотехника: Учеб. пособие для вузов. – СПб.: БВХ-Петербург, 2005. – 800 с.

2.Основы микропроцессорной техники / Новиков Ю.В., Скоробогатов П.К. / М.: ИНТУИТ. РУ, 2003 – 440 с.

3.Схемотехника электронных систем. Микропроцессоры и микроконтроллеры./ В. И. Бойко, А. Н. Гуржий, В. Я. Жуйков и др. – СПб.: БВХ-

Петербург, 2004. – 464 с.

22

4.Пухальский Г. И. Проектирование микропроцессорных устройств: Учебное пособие для вузов. – Санкт-Петербург, 2001 – 544с

5.Хилбурн Дж., Джулич П. Микропроцессоры и микро-ЭВМ. / пер. с

англ. – М.: Мир, 1979. – 464 с.

6.Гилмор Ч. Введение в микропроцессорную технику. / пер. с англ. М.:

Мир, 1984 – 334 с.

Тема 4. Микропроцессор 8080

Архитектурные особенности

Микропроцессор 8080, произведѐнный фирмой Intel в начале 70-х годов прошлого века, представляет собой микропроцессор, классифицируемый как

универсальный, однокристальный, асинхронный, 8-разрядный,

с фиксированной системой команд.

Он является типичным представителем фон-неймановской архитектуры, предполагающей только логическое разделение адресных пространств памяти программ и памяти данных (при физическом их совмещении).

Другой архитектурной особенностью процессора 8080 является схемо-

техническая и программная разделѐнность пространства памяти данных от пространства регистров интерфейсов внешних устройств (портов). Это выражается в следующих моментах:

стробирование операций обмена производится разными сигналами; для обращения к ячейкам памяти данных предназначены одни коман-

ды, а для доступа к портам – другие; разная разрядность адресов: адрес ячейки памяти – 16-разрядный, а ад-

рес порта – 8-разрядный.

Структура

Все основные части процессора 8080 размещаются в кристалле микросхемы 8080 (микросхема 8080). Но для получения полноценного процессора требуется дополнительной внешней логикой реализовать ещѐ два функциональных элемента: синхрогенератор и системный контроллер.

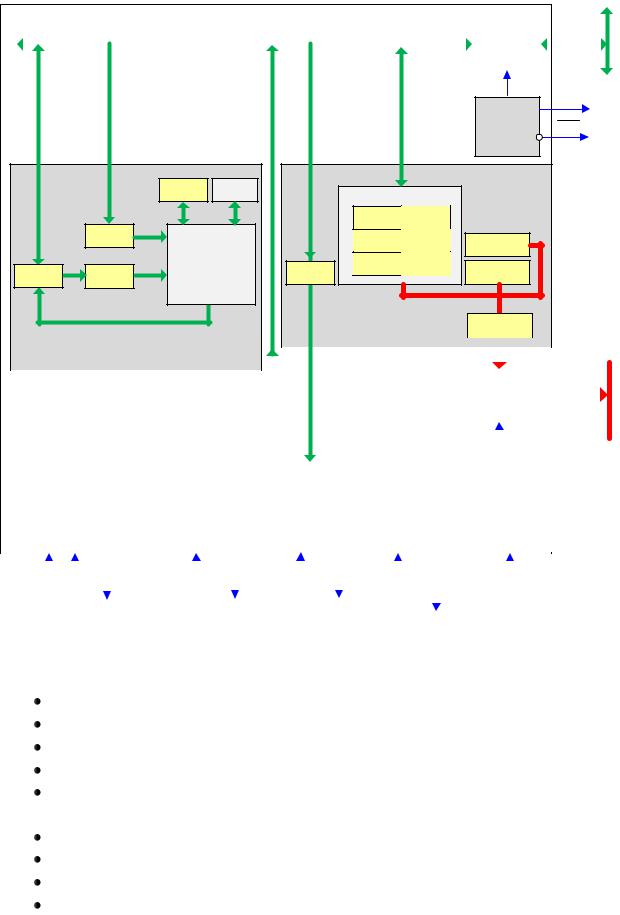

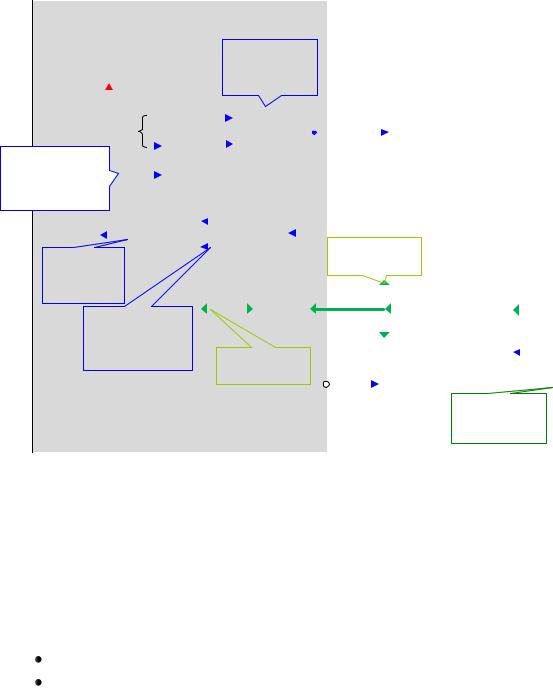

Структурная схема микросхемы 8080 представлена на рис. 2.6. Еѐ элементы можно условно разделить между тремя блоками:

блок арифметическо-логических операций; блок регистров; блок управления и синхронизации.

23

|

Микросхема процессора 8080 |

(8) |

|

|

D0..7 |

|

Внутренняя шина данных |

Буфер |

|

||

(8) |

(8) |

|

данных |

(8) |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

DBIN |

|

|

|

|

|

(8) |

(8) |

|

(8) |

BDU |

WR |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Блок регистров |

|

|

|

|

FR (8) |

DAA |

|

|

Рабочие регистры |

|

||

|

|

|

|

|

|

|

|

|||

|

|

(8) |

|

|

|

|

B (8) |

C (8) |

|

|

|

Ra (8) |

Арифме- |

|

|

D (8) |

E (8) |

|

|

||

|

|

|

|

SP (16) |

|

|||||

|

|

|

|

|

|

|||||

|

|

|

тическо- |

|

|

|

|

|

||

|

|

(8) |

|

|

H (8) |

L (8) |

|

|

||

A (8) |

Rb (8) |

логическое |

IR (8) |

PC (16) |

|

|||||

|

|

|

||||||||

|

|

|

|

|||||||

|

устройство |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

(8) |

|

|

|

|

|

|

(16) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADR (16) |

|

|

|

|

Блок арифметическо-логических |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

операций |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(16) |

|

A0..15 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

адреса |

|

(16) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(8) |

|

|

|

|

|

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок управления и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

синхронизации |

Формирование |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

Дешифратор |

|

|

|

|

|

|

BAU |

|

|

||||||||||||||||||||||

|

|

PSW (слова |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

команд |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

Синхронизация |

|

состояния) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

и тактирование |

|

|

Управление |

|

|

Управление |

|

|

Анализ |

|

Управление |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

прерываниями |

|

захватом |

|

готовности |

|

сбросом |

|

||||||||||||||

|

|

|

CLK1 |

|

CLK2 |

|

SYNC |

|

|

|

INT |

|

INTE |

|

|

|

|

HOLD |

|

HLDA |

|

|

READY |

|

WAIT |

|

|

RESET |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.6. Структурная схема микросхемы 8080.

Блок арифметическо-логических операций состоит из следующих узлов:

арифметическо-логическое устройство, аккумулятор A (8),

входные буферные регистры АЛУ Ra (8) и Rb (8), регистр признаков FR (8),

схема десятичной коррекции (DAA).

Блок регистров включает в себя:

6 программно-доступных рабочих регистров; регистр команд IR (8);

регистр указателя стека SP (16);

регистр счѐтчика команд PC (16);

24

регистр адреса ADR (16).

Блок синхронизации и управления включает следующие узлы:

управление буфером данных BDU;

управление буфером адреса BAU; дешифратор команд;

формирование слова состояния PSW; синхронизации и тактирования; управление прерываниями; управление захватом; анализ готовности;

управление сбросом в исходное состояние.

Блоки процессора обмениваются между собой данными по линиям внутренней 8-разрядной шины данных. Управление обменом по внутренней шине данных, а также инициация других совместных действий выполняется сигналами блока управления и синхронизации.

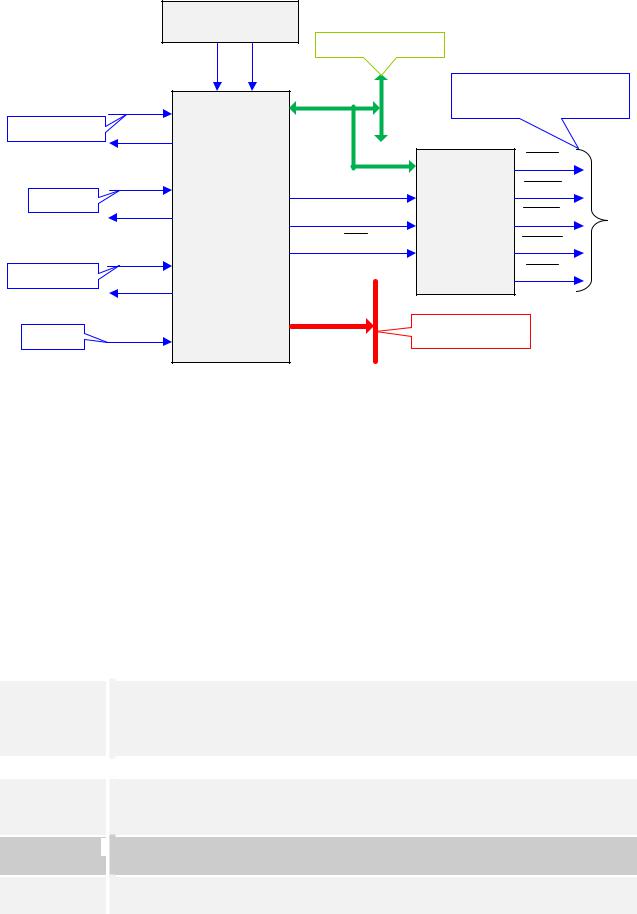

Структурная схема микропроцессора 8080 представлена на рис. 2.7. В дополнение к микросхеме 8080 на ней синхрогенератор и системный контроллер. Синхрогенератор поставляет импульсы CLK1и CLK2, тактирующие действия процессора. Системный контроллер достраивает логику управления системной шиной, обеспечивая формирование сигналов стробирования в обменных операциях с устройствами шины.

Блок арифметическо-логических операций

Блок арифметическо-логических операций выполняет арифметические и логические операции над операндами, помещѐнными в его буферные регистры Ra и Rb. В этих операциях может также участвовать бит переноса из регистра признаков FR. Причем, содержимое Rb всегда загружается перед началом операции из аккумулятора, а содержимое Ra берѐтся в зависимости от способа адресации применѐнного в выполняемой команде:

из рабочего регистра; из второго байта выполняемой команды;

из ячейки памяти, адрес которой содержится в регистровой паре HL (ячейка памяти M).

|

|

|

|

25 |

|

|

|

|

Синхрогенератор |

|

|

|

|

|

|

CLK1 |

CLK2 |

Шина данных |

|

|

|

|

|

Линии управления: |

|||

|

|

|

|

(8) |

||

|

INT |

|

|

стробы чтения/записи |

||

|

|

|

|

|||

Прерывание |

INTE |

|

|

D0..7 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

MRD |

|

HOLD |

|

|

SYNC |

|

MWR |

|

|

|

|

|

||

Захват |

|

|

|

|

|

|

HLDA |

|

|

DBIN |

Системный |

|

|

|

Микросхема |

IORD |

||||

|

|

|||||

|

|

|

8080 |

WR |

контроллер |

|

|

|

|

|

IOWR |

||

|

READY |

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

Готовность |

WAIT |

|

|

|

|

INTA |

|

|

|

|

|

|

|

|

|

|

|

(16) |

|

|

Сброс |

RESET |

|

|

A0..15 |

Шина адреса |

|

|

|

|

|

|

||

|

Рис. 2.7. Структурная схема микропроцессора 8080. |

|

||||

Числовое значение результата операции сохраняется в аккумуляторе, а признаки этого результата устанавливаются в битах регистра признаков FR. Формат регистра признаков представлен на табл. 2.1, а значения отдельных битов объясняет табл. 2.2.

Таблица 2.1

Формат регистра признаков

|

|

|

Биты |

|

D7 |

|

D6 |

|

D5 |

|

D4 |

|

D3 |

|

D2 |

|

D1 |

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

Обозн |

|

S |

|

Z |

|

0 |

|

AC |

|

0 |

|

P |

|

1 |

|

CY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2.2 |

|

|

|

|

|

|

Значения битов признаков |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Слово |

|

|

|

|

|

|

|

|

|

Назначение |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sign Знак результата: "1"– минус; "0"– плюс. Знаком двоичного числа принято считать (как в схемотехнике цифроаналогового преобразования) значение старшего бита этого числа. Поэтому в бит S просто копируется старший бит результата операции, выполняемой процессором.

|

Zero |

|

|

|

Нулевой результат: да–"1"; нет–"0". |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

CarrY В этот бит помещается перенос из старшего разряда аккумулятора при сложении или из него берѐтся заѐм в старший разряд аккумулятора при вычитании: "1"– есть перенос или заѐм.: "1"–нет.

Add Carry  Дополнительный перенос – то же что и Carry, но для границы полубайтов

Дополнительный перенос – то же что и Carry, но для границы полубайтов

результата операции (биты D3 и D4).

Parity Паритет (чѐтность) для числа, показывающего количество битов равных "1" в составе байта результата: чѐтное (Even) –"1"; нечѐтное (Odd) – 0.

26

Блок регистров

Блок регистров рассчитан на временное хранение операндов и адресов, необходимых процессору при выполнении команд.

Часть из регистров блока являются рабочими регистрами или регистрами общего назначения (РОН): B, C, D, E, H, L. К ним можно адресоваться командами программы для чтения или записи (они программно доступны).

Регистр SP – указатель стека, поэтому всегда содержит адрес вершины стека. При этом сам стек организуется в основной памяти.

Регистр PC – счѐтчик команд. Он всегда содержит адрес ячейки памяти, из которой будет извлечена очередная команда программы. Та команда, которая последует за текущей выполняемой командой. Его новое содержимое формируется автоматически, в зависимости от текущей принятой команды сразу после приѐма этой команды. Если она не является командой ветвления, то PC увеличивается на число, равное количеству байт, содержащихся в текущей команде. Если же текущая команда является командой ветвления, тогда PC загружается вторым и третьим байтами принятой команды.

Регистр адреса ADR предназначен для хранения адреса ячейки памяти или регистра внешнего устройства при обращении к ним. В этом случае буфер адреса коммутирует содержимое регистра ADR на линии адреса шины

A0-15.

Адрес формируемый процессором (текущее содержимое ADR) зависит от стадии интерпретации и от интерпретируемой команды.

Блок синхронизации и управления

Микропроцессорный блок синхронизации и управления является управляющим центром как самого процессора, так и всей микро-ЭВМ. Он тактирует и инициирует все управляющие действия: как при работе своих внутренних узлов и блоков, так и при операциях на системной шине.

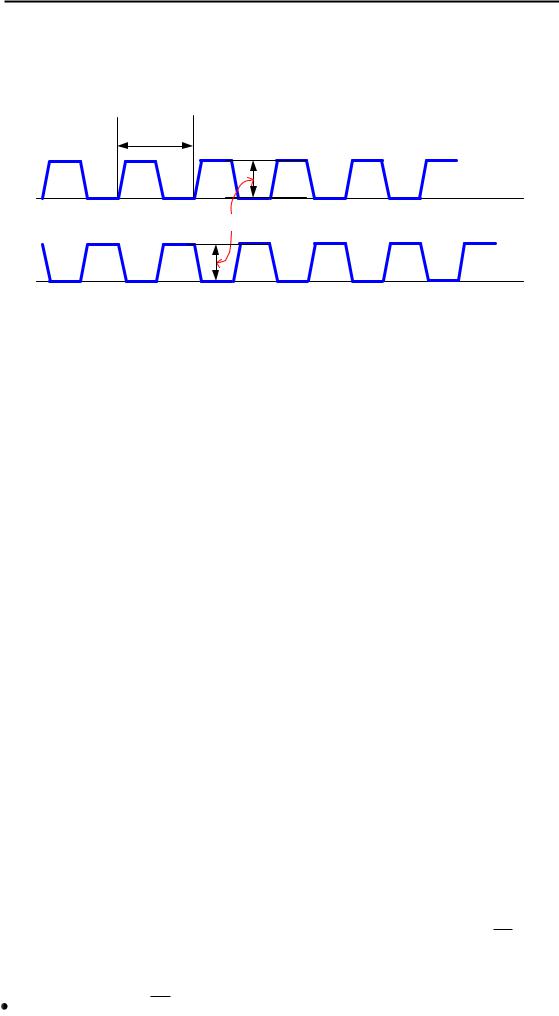

Синхронизация и тактирование

Схема синхронизации и тактирования рассчитана на работу совместно с синхрогенератором, который должен быть реализован внешней схемой. Эта внешняя схема должна обеспечить две тактовых неперекрывающихся последовательности импульсов CLK1 и CLK2: с амплитудой 12 В, с частотой 2,5

мГц ( рис. 2.9).

27

≥0,4 мкс

CLK1

CLK2 |

12 В |

|

Рис. 2.9. Импульсы тактирования процессора 8080

Наиболее удачным вариантом генератора для процессора 8080 является микросхема 8224 (аналог – КР580ГФ24). Кроме главной функции микросхема 8224 также обеспечивает синхронизацию внешних асинхронных сигналов поступающих в процессор и генерацию импульсов уровней ТТЛ для потребностей других устройств микро-ЭВМ.

Схема синхронизации и тактирования, получив импульсы CLK, обеспечивает формирование внутренних импульсов для тактирования элементарных операций процессора с частотой импульсов CLK. Эти операции называются

машинными тактами. Время машинного такта фиксировано – оно равно периоду тактовых импульсов CLK.

Кроме внутренних операций процессор периодически должен обращаться к системной шине для выполнения обменных операций с другими устройствами микро-ЭВМ. Действия процессора в рамках одного его обращения к системной шине называются машинным циклом. Иначе говоря, ма-

шинный цикл – элементарный процесс обмена с шиной. Длительность ма-

шинного цикла определяется характером обменной операции и может быть различной (от 3 до 5 машинных тактов). Начало каждого машинного цикла схема синхронизации и тактирования сопровождает формированием сигнала

SYNC.

При выполнении одной команды необходимы от 1 до 5 машинных цик-

лов. Отработка процессором всех машинных циклов одной команды называется командным циклом.

Управление системной шиной

Связь с линиями адреса и данных системной шины осуществляется че-

рез буферы адреса и данных.

Схема управления буфером данных (BDU) предназначена для управления выбором направления потока данных через BD и выдачи соответствующих этому направлению внешних сигналов DBIN (прием) и WR (запись). Когда процессор выполняет операцию записи, схемой BDU формируется два сигнала:

внешний сигнал WR ;

28

внутренний сигнал управления буфером данных, соответствующий выбранному направлению потока данных от процессора на системную шину.

При приѐме процессором данных BDU формирует альтернативные сигналы:

внешний сигнал DBIN;

внутренний сигнал для управления буфером данных обеспечивающий направление потока данных от системной шины в процессор.

Сигналов управления шиной, формируемых блоком синхронизации и управления микросхемы 8080, недостаточно для управления обменами по шине. Часть схемы управления процессором, называемая системным контроллером, поэтому строится из дополнительных элементов вне микросхемы 8080 (рис. 2.10). Она вместе со схемой формирования слова состояния PSW решает проблему недостающих сигналов управления обменом по шине.

(8) |

Буфер |

D0..7 |

|

Буфер |

|

|

(8) |

|

данных |

(8) |

|

данных |

|

|

|

|

|

|

|

|

|

|

|

(8) |

|

|

|

|

|

|

|

Формирование |

|

|

|

|

|

|

Шина данных |

PSW (слова |

|

|

|

|

|

|

|

|

|

|

RG |

|

|

микро-ЭВМ |

|

состояния) |

|

|

(8) |

|

|

||

|

|

|

|

|

|

||

|

|

|

DO |

|

|

|

|

|

|

|

DI |

|

Дешифратор |

|

|

|

|

|

|

|

|

|

|

Синхронизация |

|

SYNC |

|

|

|

DC |

MRD |

|

WE |

|

|

|

|||

и тактирование |

|

|

(8) |

|

MWR |

||

|

|

|

|

DI |

|||

|

|

|

Регистр |

|

|

||

|

|

|

|

|

IORD |

||

|

|

|

|

|

|

|

|

|

|

DBIN |

|

|

|

|

IOWR |

|

|

|

>=1 |

|

|

|

|

|

|

|

|

|

|

INTA |

|

|

BDU |

|

|

|

|

OE |

|

|

WR |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Линии |

Микросхема 8080 |

|

|

Системный контроллер |

управления: |

|||

|

|

|

|

|

|

|

стробы |

|

|

|

|

|

|

|

чтения/записи |

Рис. 2.10. Логика формирования сигналов управления обменами по шине.

Наилучшим образом системный контроллер процессора 8080 реализуется на основе микросхемы 8228 (аналог КР580ВК28). Кроме основной функции она выполняет функцию буфера линии данных системной шины. Для этой цели в ее составе есть двунаправленный буфер данных.

Перед началом каждого машинного цикла логика процессора формирует байт слова состояния PSW. Этот байт содержит биты, характеризующие предстоящий машинный цикл.

В первом такте машинного цикла PSW выставляется на линии данных шины и одновременно, сопровождая начало машинного цикла, формируется строб SYNC для системного контроллера (SC). По пришедшему в SC сигналу

29

SYNC в регистре RG фиксируются биты информации о характере текущего машинного цикла.

Следующим тактом линии данных уже свободны для использования по прямому назначению. С выхода RG биты слова состояния поступают на дешифратор сигналов управления DC. Сигналом к началу дешифрации является приход одного из процессорных сигналов DBIN или WR . По его приходу дешифратором вырабатывается один из выходных сигналов, стробирующих обмен для текущего машинного цикла:

MRD – чтение памяти;

MWR – запись в память;

IORD – чтение регистра интерфейса внешнего устройства;

IOWR – запись в регистр интерфейса внешнего устройства; INTA – чтение команды из инициатора прерывания.

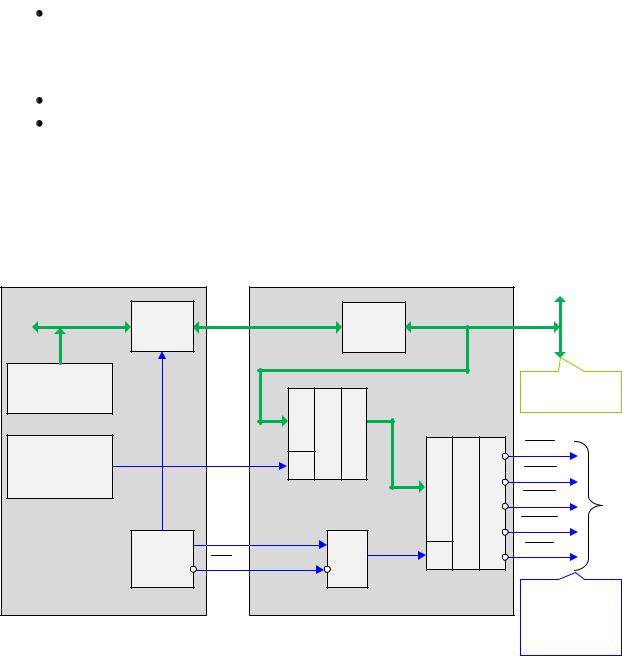

Управление прерываниями

Логика управления прерываниями (рис. 2.11) обеспечивает микропроцессор возможностью программно реагировать на внешние события в моменты их происхождения. Момент происхождения события во внешнем устройстве сопровождается появлением сигнала запрос прерывания INT, формируемым интерфейсом этого устройства на вход процессору.

На основе логики управления прерываниями реализован механизм прерываний процессора. Эта логика имеет в своем составе два триггера: триггер разрешения прерывания и триггер запроса прерывания.

Триггер разрешения прерывания обеспечивает возможность управлять разрешением на обслуживание процессором запросов. Выход этого триггера подключѐн на вывод INTE. Будучи установлен он разрешит установку триггера запроса прерывания и реакцию процессора на прерывание, а будучи сброшен – заблокирует прерывания. Управление установкой/сбросом триггера разрешения возможно как программным путѐм так и аппаратно. В системе команд процессора есть специальные команды: DI (запретить прерывания) – для сброса триггера и EI (разрешить прерывания) – для установки триггера. Кроме того, сброс триггера разрешения будет осуществляться автоматически (аппаратно) в первом такте машинного цикла прерывания (сигнал R_Inte). Поэтому после отработки очередного прерывания, для возможности нового прерывания, необходимо снова программно устанавливать триггер разрешения, применяя команду EI.

30

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команда |

S |

R |

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

EI |

|

|

1 |

|

|

0 |

1 |

|

|

|

|

Триггер |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

разрешения |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

DI |

|

|

0 |

|

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

прерываний |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Устанавливаются |

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

S |

T |

|

|

|

|

|

|

|

|

INTE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

командами |

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

программы |

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

>=1 |

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

Автоматически |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

R_Inte |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Инициатор прерывания |

|

|

|||||||||||||||||||

появляется в 1-м |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(интерфейс внешнего |

|

|

|||||||||||||||||||||

такте МЦ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

устройства) |

|

|

|

|

|

|||||||||||

прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

T |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

T_Int |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT |

|

|

|

|

|

Логика |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

формирования |

|

|

RSTn |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Шина данных |

|

|

|

запроса |

|

|

|

|

|

|

||||||||||

|

Триггер |

|

|

|

|

|

|

|

|

|

R_Int |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

7 |

|

|

|||||||||||||||||||

|

запроса |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

микро-ЭВМ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

6 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RG |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

(8) |

|

|

|

|

|

|

|

|

|

|

(8) |

(8) |

|

|

|

|

|

|

|

N |

|

5 |

н |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер |

|

|

|

|

|

|

|

(8) |

|

|

о |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DO |

|

DI |

|

|

|

|

|

||||||||||||||||||

|

|

Автоматически |

|

|

|

|

|

данных |

|

|

|

|

|

D0..7 |

|

|

|

|

|

|

|

|

|

|

N |

|

4 |

м |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

появляется в 2-м |

|

|

|

|

|

|

|

|

|

|

|

|

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

3 |

|

||||||||||||||||||

|

|

|

|

такте МЦ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE |

|

|

|

|

|

|

р |

|

||||||||||

|

|

|

|

|

|

|

|

Внутренняя |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

|

|||||||||||||||||||

|

|

прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шина данных |

|

|

|

|

|

|

|

|

Регистр |

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTA |

|

|

|

|

|

1 |

|

1 |

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Код команды |

1 |

|

0 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RSTn – вызов |

|

|

|

|

|

|||||||

|

|

|

|

|

Микропроцессор 8080 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

подпрограммы |

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.11. Средства механизма прерываний процессора 8080.

Триггер запроса прерывания предназначен для указания процессору на необходимость приступить к обслуживанию прерывания с началом нового командного цикла.

Программное переключение процессора на отработку прерывания по сигналу INT связано со следующей особенностей отработки процессором

8080 командных циклов. Непосредственно перед завершением каждой команды процессор проверяет состояние:

своего запросного входа INT; триггера разрешения прерывания.

При отсутствии установки хотя бы одного из них процессор переходит

ккомандному циклу той команды, на которую укажет ему счѐтчик команд.

Вдругом случае, когда триггер разрешения прерываний и сигнал INT установлены, процессор установит триггер запросов и следующим тактом начнѐт новый командный цикл с выполнения машинного цикла прерывания (будет детально рассмотрен далее). Этот момент будет моментом начала обслуживания прерывания. В первом такте машинного цикла прерывания сигналом R_Inte сбрасывается триггер разрешения, а со следующим вторым тактом сигналом R_Int сбрасывается и триггер запросов. Машинный цикл прерывания – есть обмен с инициатором прерывания, посвящѐнный выборке кода команды вызова подпрограммы. Адрес определѐнный данной командой