- •Универсальные элементы памяти. Принцип организации специальных элементов на базе универсальных.

- •Лабораторная работа №2.4.

- •Синтез устройств и узлов для бортовой вычислительной техники. Синтез управляющих схем для многофункциональных регистров.

- •Формирование прямого и обратного парафазных кодов на параллельном регистре.

- •Поразрядная обработка машинных слов с использованием параллельных регистров.

- •Лабороторная работа № 3.1

- •Маскирование машинных слов для выделения составляющих их кодов.

- •Выполнение на параллельных регистрах операции сравнивания кодов.

- •Синтез последовательных регистров на различной элементной базе.

- •Использование последовательных регистров парафазного кода.

- •Реализация сдвига с использованием регистра на т-триггерах.

- •Лабороторная работа № 3.2

- •Двухступенчитый регистр сдвига, использующий парофазный код.

- •Лабороторная работа № 3.3

- •Регистры сдвига с перекрёстными связями на rs-триггерах.

- •Лабороторная работа № 3.4

- •Регистры сдвига на синхронных элементах памяти

- •Использование универсальных запоминающих элементов для построения последовательных регистров

- •Реверсивный регистр сдвига на jk-триггерах

- •Ц иклический регистр сдвига

- •Синтез дешифраторов на базе клс

- •Помехоустойчивость линейных дешифраторов

- •Пирамидальные дешифраторы

Синтез дешифраторов на базе клс

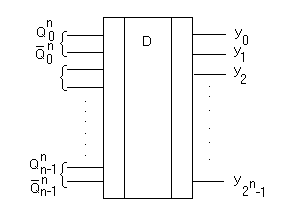

Дешифратор – это преобразователь n-разрядного двоичного кода в управляющий сигнал на одном из 2n выходов.

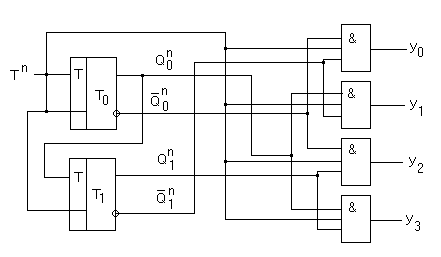

Уравнения линейного дешифратора выглядят следующим образом:

(1)

(1)

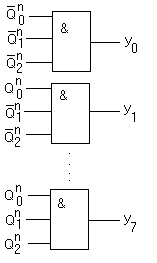

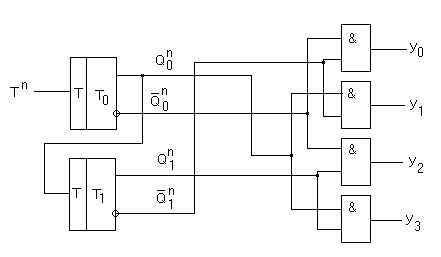

При синтезе линейного дешифратора могут непосредственно использоваться уравнения системы (1) или эти уравнения преобразуются с использованием ассоциативных законов. Простой линейный дешифратор представляет собой КЛС, элемент которой И имеет n входов и отображает на выходе единственный для данного входного слова выходной сигнал дешифратора:

Количественной характеристикой линейного дешифратора являются аппаратные затраты, включающие суммарное число схем И ( М ) и суммарное число входов этих схем ( m ):

,

где

,

где

n – число разрядов водного слова.

Быстродействие дешифратора оценивается как:

,

где

,

где

k – число ступеней дешифратора;

и – задержка в элементе И.

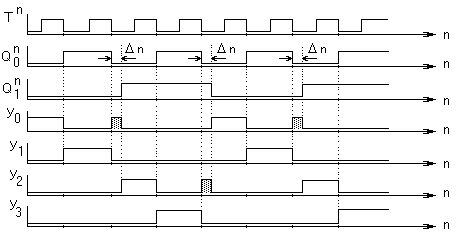

Для характеристики работы дешифратора, построим временную диаграмму линейного дешифратора, использующегося для оценки состояния двоичного счётчика:

Учтём в виде постоянного запаздывания n эффект неодновременного переключения триггеров в счётной схеме. Используя уравнения системы (1), графически представим сигналы y0…y3.

Помехоустойчивость линейных дешифраторов

Учёт

реального запаздывания переключения

последовательностных элементов как

источников формирования входных слов

дешифратора, является причиной

появления на его выходах ложных

сигналов ( на диаграмме они заштрихованы

). Так как сигналы

выполняют роль управляющих сигналов

в цифровых схемах, то это приводит

к нарушению нормальной работы всего

устройства. Одним из способов

устранения ложных срабатываний

дешифратора является синхронизация

работы всех элементов схемы.

выполняют роль управляющих сигналов

в цифровых схемах, то это приводит

к нарушению нормальной работы всего

устройства. Одним из способов

устранения ложных срабатываний

дешифратора является синхронизация

работы всех элементов схемы.

При использовании пассивных элементов в схеме линейного дешифратора и увеличении разрядности входного слова возможно появление ложных сигналов как реакции на неравномерное распределение нагрузки на входах элементов И дешифратора. Проблема помехоустойчивости в подобных случаях решается использованием в дешифраторах элементов И с минимальным числом входов.

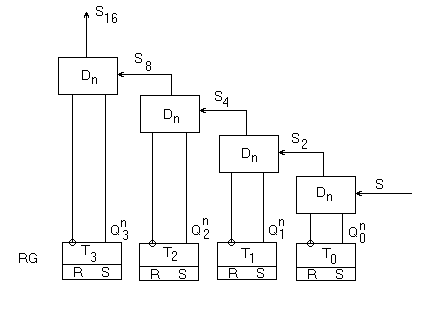

Пирамидальные дешифраторы

Источником

входной информации для пирамидальных

дешифраторов являются параллельные

и последовательные регистры, в

последнем случае циклические,

формирующие, как правило, входные

слова в виде параллельного кода,

отображаемого потенциальными сигналами.

Управляющая информация, представленная

здесь символами S,

является импульсной и, начиная с

выходов S2,

преобразуется в выходную информацию

дешифратора. Оценим аппаратные затраты

пирамидального дешифратора: количество

схем И, входящих в Dn

, можно описать как

,

где n

– разрядность входного слова. Суммарное

число входов в элементах Dn

оценивается как

,

где n

– разрядность входного слова. Суммарное

число входов в элементах Dn

оценивается как

.

.

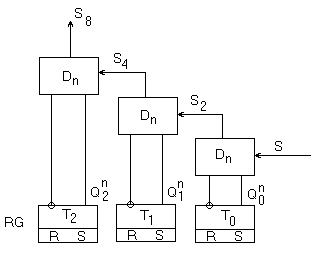

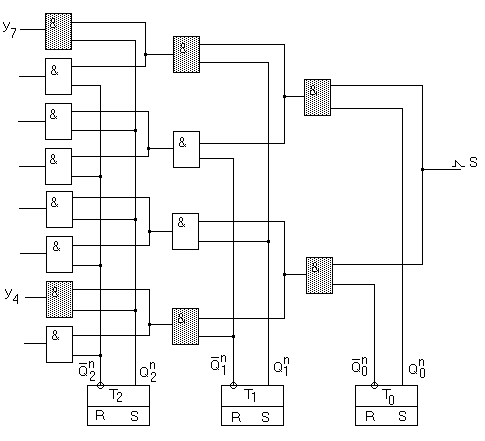

Спроектируем пирамидальный дешифратор для n=3:

Пусть

слово:

тогда получим сигнал на выходе y4.

тогда получим сигнал на выходе y4.

Пусть

слово:

тогда получим сигнал на выходе y7.

тогда получим сигнал на выходе y7.

Схемы дешифраторов выполняют двойную роль в цифровых системах: с одной стороны они используются для преобразования параллельных кодов в управляющие сигналы, которые осуществляют адресную выборку информации; с другой стороны они могут выполнять роль мультиплексора, распределяющего входную информацию по выбранным каналам.