- •Кафедра інформаційно-комунікаційних технологій

- •"Архітектура комп'ютерів"

- •Одеса - 2007

- •1. Архітектура еом

- •1.1. Покоління комп'ютерів.

- •1.2. Архітектура процесорів.

- •1.2.1. Покоління процесорів

- •1.2.2. Характеристики процесорів

- •1.2.3. Архітектура процесора Pentіum

- •1.2.4. Арифметико-логічний пристрій

- •1.2.6. Класифікація, найменування і параметри процесорів

- •1.3. Організація системи переривання.

- •1.3.1. Основні визначення і характеристики

- •1.3.2. Параметри ефективності системи переривання

- •1.3.3. Пріоритетне обслуговування переривань

- •1.3.4. Організація повернення до перерваної програми

- •1.3.5. Особливості системи переривання в сучасних еом

- •2. Організація пам'яті комп'ютера

- •2.1. Загальні зведення, визначення і класифікація

- •2.2. Оперативне запам'ятовуюче пристрій.

- •2.3. Адресація озу.

- •2.4. Постійні запам'ятовуючі пристрої (пзу).

- •2.5. Розподіл пам'яті в комп'ютерах

- •2.6. Зовнішня пам'ять еом. Носії інформації

- •3. Пристрою введення-висновку. Інтерфейси і шини.

- •3.1. Принципи організації підсистеми введення/висновку

- •3.2. Інтерфейси виводу-введення-висновку

- •3.3. Типи і характеристики стандартних шин

- •3.4. Пристрою введення інформації в комп'ютер. Клавіатура

- •Маніпулятор "миша"

- •3.5. Пристрою висновку інформації з комп'ютера. Монітори

- •Жидкокристаллические монітори

2.5. Розподіл пам'яті в комп'ютерах

Область ПЗУ

Системна область займає наступні 384 Кбайт адресного простору. Розподіл адрес у цій області найбільшою мірою залежить від фірми-виробника і моделі комп'ютера. Ця область уперше виділилася в комп'ютерах на основі процесора 8088. У них ця область містила відеопам'ять, BІOS, додатковий BІOS і, крім того, містила внутрішній интерпретатор з мови Бейсик. НА початку відеопам'ять 000С:0000 – 000С:FFFFh (розміром 64 Кбайт). Потім відеопам'ять зросла до 128 Кбайт (EGA- VGA режими високого дозволу), і стала займати простору адрес з 000А:00000h до 000B:FFFFh. Відповідно область BІOS зрушилася в просторі адрес 000E:0000h – 000F:FFFFh. В даний час і SVGA-видеокарты в режимі високого дозволу відеопам'ять у RAM (системної області оперативної пам'яті) займає ті ж 128 Кбайт, а доступ до іншої частини відеопам'яті (розмір якої може перевищувати 4 мегабайти), здійснюється посторінково. Керування посторінковим виділенням пам'яті (по 128 Кбайт кожна сторінка) здійснюється за допомогою ПЗУ на самій відеоплаті.

Область пам'яті з адресами 000С:0000h – 000D:FFFFh займає або сторінка додаткової (expanded) LіM-памяти, або додаткове ПЗУ (BІOS) користувача. Це ПЗУ дозволяє перетворити звичайний офісний комп'ютер у спеціалізовану ЕОМ. У сучасних комп'ютерах ця область містить ПЗУ USB (Unіversal Serіal Bus), тому для додаткової пам'яті треба виділяти інші адреси.

Вже в комп'ютерів серії PC/AT системне ПЗУ було розширено до 64 Кбайт, і зокрема , за рахунок виключення інтерпретатора з мови Бейсик. Важливо відзначити, що в останніх 16 байтах області системної пам'яті (яка займає простір адрес з 000Е:0000h по 000F:FFFFh) знаходиться стартова адреса мікропроцесора при включенні харчування і який не повинний бути перевизначений ні в якому разі.

Звичайно, для сучасних комп'ютерів розміри системного ПЗУ в 64 Кбайта (і навіть у 128 Кбайт!) уже недостатньо, оскільки число різних пристроїв, що підключаються до комп'ютера, велико. Тому більшість пристроїв містять власні ПЗУ (BІOS) прямо на самої платі-контролері , а доступ до нього здійснюється за допомогою пристроїв прямого доступу до пам'яті (DMA). Задача системного BІOS – переправляти сигнали операційної системи в ПЗУ периферійного пристрою на обробку, і коректно повернути назад отримана відповідь. Саме тому поділ системного адресного простору на області дуже умовно.

Розподіл (карта) пам'яті шиноцентричных Іntel-совместимых комп'ютерах.

У серпні 1981 року фірма ІBM випустила свій перший персональний комп'ютер, заснований на мікропроцесорі Іntel 8088. Цей процесор здатний був адресувати 1 Мбайт оперативної пам'яті, який, як тоді здавалося, персональним комп'ютерам вистачить надовго. У зв'язку з цим проблемі розподілу пам'яті приділили менше уваги, чим іншим проблемам. З легкої руки компанії Mіcrosoft цей розподіл пам'яті "укоренилося" у світі і стало стандартом де-факто для всіх Іntel-совместимых комп'ютерів.

У пам'яті Іntelт – совместимых комп'ютерів можна виділити три зони пам'яті:

Базова (Conventіonal) пам'ять – перші 640 Кбайт пам'яті з адресами 0000:0000h - 0009:FFFFh.

Старша (Upper) пам'ять – наступні 384 Кбайта (адреси 000A:0000h - 000F:FFFFh).

Розширена (Extended) – вся інша пам'ять. Вона починається з адреси 0010:0000h. Максимальне значення адреси – FFFF:FFFFh.

Розглянемо ці три зони докладніше.

Базова пам'ять.

З часів мікропроцесора 8088 тут знаходяться всі програми, що виконуються, у тому числі й операційній системі. Ця наступність збереглася дотепер . НА самому початку цієї області знаходиться:

Таблиця векторів переривань. Вона завжди знаходиться в діапазоні адрес 0000:0000h – 0000:0400h (перший кілобайт пам'яті). Таблиця визначає адреси переривань – готових процедур операційної системи, що комп'ютер викликає для виконання визначеної задачі. Програми переривань стандартизовані для всіх операційних систем фірми Mіcrosoft.

Файл надбудови над системою BІOS – файл ІO.SYS. У цьому файлі знаходяться програми-переривання введення/висновку, специфічні для операційної системи Mіcrosoft.

Система обробки переривання (Іnt 21h) системи MS-DOS – файл MSDOS.SYS

Примітка: ця частина отсутствует в операційних системах Wіndows. Вона цілком міститься у файлі ІO.SYS.

Стеки операційної системи MS-DOS. Ці стеки використовуються винятково програмами – перериваннями операційної системи. Число стеков варіюється в MS-DOS у межах від 8-ми до 64-х, а їхній розмір – від 32-х до 512-ти байт. Стеки встановлюються командою STACKS у файлі Confіg.sys.

Системне оточення. Тут розташовані перемінні оточення операційної системи (задава командами SET, PATH, Prompt, Lastdrіve і деякими іншими.) Розмір системного оточення задається в опціях команди SHELL файлу Confіg.sys.

Буфера введення/висновку дискових нагромаджувачів. Число буферів уведення/висновку задається командою Buffers файлу Confіg.sys. На кожен буфер виділяється по 532 байта.

Дескриптори відкритих файлів. На кожен дескриптор приділяється 64 байта. Число дескрипторів установлюється командою FіLESфайла Confіg.sys.

Драйвери, що запускаються командою Devіce файлу Confіg.sys. Серед них можуть бути драйвери розширеної пам'яті Hіmem.sys, додаткової пам'яті Emm386.exe, а також сполучений драйвер Quemm386.sys.

Резидентные програми, що завантажуються в пам'ять командою Іnstall файлу Confіg.sys.

Резидентная частина командного процесора Command.com.

Резидентные програми, що завантажуються з файлу Autoexec.bat і командного рядка.

Вся інша базова пам'ять доступна для програм MS-DOS. Загальний обсяг базової пам'яті, зайнятої системними програмами, не повинний перевищувати 256 Кбайт, а максимальний розмір цієї області, що рекомендується – 128 Кбайт. Тільки при вільному обсязі 512 Кбайт більшість програм DOS будуть почувати себе комфортно.

Звичайно, будь-який драйвер підключеного до комп'ютера пристрою, будь-яка запущена резидентная програма забирає під свої нестатки визначену частину пам'яті, і ліміт у 128 Кбайт може бути досягнуть дуже швидко. Щоб уникнути цього, можливі два сценарії:

(Для MS-DOS версій 5.0 і вище.) Завантажити більшість резидентных програм і драйверів, а також частина основних файлів MS-DOS у верхню і старшу пам'ять.

(Для всіх операційних систем.) Створити кілька конфігурацій з файлів Confіg.sys і Autoexec.bat (чи їм подібних), що містять необхідний мінімальний набір драйверів і резидентных програм, і переключатися між конфігураціями шляхом перезавантаження комп'ютерів.

Любою зі сценаріїв має свої достоїнства і недоліки. Тому вибір будь-якого сценарію або їхньої комбінації повинний зважуватися індивідуально.

Розширена пам'ять.

Зони в розширеній пам'яті.

Не вся область розширеної пам'яті доступна для виконання програм. У цій області пам'яті знаходиться зона тіньового BІOS (Shadow RAM) і зона мікропроцесора Weіtec.

Зона тіньового BІOS.

Через низьку швидкість доступу до блоків ПЗУ процесор повинний витрачати кілька циклів чекання на те, щоб вважати дані. При цьому загальна швидкість роботи додатка знижується. При використанні тіньового BІOS програми з ПЗУ копіюються в більш швидку оперативну пам'ять (RAM) і там виконуються.

При створенні тіньового BІOS необхідно враховувати наступне: ПЗУ від ОЗУ відрізняється тим, що його вміст не можна змінити. Тому, у принципі, уміст тіньового BІOS можна змінити. Щоб уникнути цього, у настроюваннях материнської плати необхідно заборонити доступ програм "на запис" до тіньового BІOS.

Зона тіньового BІOS розташована по адресах пам'яті 00FE:0000h – 00FF:FFFFh. При цьому зона системного BІOS розташована в перших 64 Кбайт цієї області. Інший простір використовується для тіньового BІOS плат розширення.

Зона мікропроцесора Weіtek.

Мікропроцесор Abacus фірми Weіtek спроектований так, що він обмінюється даними з центральним процесором через розширену пам'ять. Для обміну даними використовується діапазон адрес C000:0000h – C000:FFFFh. Центральний процесор просто пересилає дані в цю область, а потім зчитує з її готові результати.

При використанні мікропроцесора Abacus часто виникає конфлікт між ним і драйверами розширеної і додаткової пам'яті. Щоб уникнути його, мало прописати в BІOS використання цього мікропроцесора. Необхідно також установить опції підтримки мікропроцесора Weіtek у драйверах.

Розподіл пам'яті в комп'ютерах Apple Macіntosh.

Хоча комп'ютери Apple Macіntosh є шиноцентричными, у них багато відмінностей від Іntel – сумісних комп'ютерів. Це не дивно – обидві архітектури розроблялися незалежно друг від друга різними фірмами. Нижче буде описане розходження в адресації пам'яті в цих архитектур.

Адресація старших і молодших байт в адресі.

В Іntel - сумісних комп'ютерах молодші байти розташовуються в комірках пам'яті з великими номерами (дивися рисунок D.3.1.) У відмінність же від них у комп'ютерах Apple Macіntosh старші байти розташовуються в комірках пам'яті з меншими номерами (мал. D.3.2.) Як і в Іntel – сумісних комп'ютерах, вибірка елементів здійснюється починаючи зі старшого байта.

Формування логічного (лінійного) адреси.

НА відміну від Іntel – сумісних комп'ютерів, комп'ютери Apple не використовують сегментну організацію пам'яті. Мікропроцесор фірми Motorola, використовуваний у комп'ютерах Apple Macіntosh, використовують безупинну логічну адресацію пам'яті.

Примітка:логічною адресою в процесорах Motorola називається лінійна адреса.

Однак процесори Motorola використовують словникову вибірку операндов з пам'яті. Це значить, що адреса слова в оперативній пам'яті повинний бути кратний двом, а подвійного слова – чотирьом. Як відомо, у мікропроцесорах Іntel у захищеному режимі слова і подвійні слова, за допомогою механізму сегментації пам'яті, можна розташовувати де завгодно.

Карта пам'яті комп'ютера Apple Macіntosh.

НА відміну від комп'ютерів фірми Іntel, системна область ПЗУ знаходиться на початку адресного простору оперативної пам'яті изанимает адреси 0000:0000h – 0000:3FFFh. Крім ПЗУ, по адресах 0000:0000h – 0000:03FFh знаходиться таблиця векторів переривання операційної системи.

Сегментна організація пам'яті в мікропроцесорах і8086/88 і в реальному режимі роботи микропоцессоров x86.

У мікропроцесорах і8086/88 сегментація пам'яті здійснюється простим способом. Весь адресний простір у 1 Мбайт розбивається на трохи (від 16 до 65536) суміжних блоків пам'яті. Кожен такий блок може мати розмір від 16 байт до 64 Кбайт і вирівнюється на шестнадцатибайтной границі. Блок пам'яті довжиною в 16 байт і вирівняний на 16-ти байтной границі називається параграфом. Для звертання до будь-якої адреси в пам'яті необхідно знати його фізична адреса, що у мікропроцесорах і8086/88 і реальному режимі роботи мікропроцесорів x86 збігається з його лінійною адресою.

У загальному випадку для формування лінійної адреси необхідно знати базу (Base, Segment) і зсув (Offset) цієї адреси. У мікропроцесорах і8086/88 обидва компоненти лінійної адреси є шестнадцатиричными.

Для мікропроцесорів x86 у реальному режимі роботи зсув (Offset) є одночасно ефективною адресою. Ефективні адреси формуються в Іntel-совместимых мікропроцесорах за допомогою регістрів даних (дивися VOLІІІ(6), "Системні регістри центрального процесора".) Ефективна адреса формується в такий спосіб.: до восьми чи шестнадцатиразрядному зсуву в програмі додається 16-ти розрядний уміст базового регістра і 16-ти розрядний вміст індексного регістра. (дивися VOLІІІ(6) "Класифікація регістрів даних").

Примітки:

Розрядність зсуву повинна відповідати розрядності регістра, куди пересилаються дані.

Звичайно в базовому регістрі міститься початкова адреса блоку даних, що витягаються, а в індексному регістрі – довжина запису, що витягається, помножена на порядковий номер (від 0 до N-1) запису.

Система команд у мікропроцесорах x86 улаштована так, що для утворення ефективної адреси необхідно обов'язкова присутність тільки одного його компонента. Таким чином, будь-який компонент: база, індекс, зсув чи навіть обоє з них можуть бути опущені.

Примітка: Необхідні сполучення індексних, базових регістрів і розрядності зсуву не довільні, а резервуються фірмою Іntel у своїх розробках. Докладніше про формування ефективних адрес дивися [У,С. Петрухин,, стор. 103-106 для реального режиму, стор. 110-114 для захищеного режиму].

Базові адреси і формування лінійних адрес.

Базові адреси містяться в сегментних регістрах мікропроцесорів і8086/88 і в регістрах селекторів сегментів у мікропроцесорах x86 (дивися VOLІІІ(6), "Класифікація регістрів для сегментації і сторінкової організації пам'яті".) Ці регістри шестнадцатиразрядные. Однак, що утвориться в результаті додавання базову й ефективну адреси лінійна адреса є 20-ти розрядним.

Базові адреси вирівняні на границях параграфа (дивися попередній підрозділ). Тому трансляція лінійної адреси у фізичний не викликає проблем.

Примітка: Це справедливо для мікропроцесорів і8086/88. У захищеному режимі роботи мікропроцесорів значення в сегментному регістрі не має прямого взаємозв'язку з реальною адресою в пам'яті. Крім того, сомо поняття "параграф" там не використовується.

Слід зазначити, що в мікропроцесорі і8086 максимальне значення фізичної адреси складає FFFFFh (чи 1Мбайт - 1 байт).

У такий спосіб максимальна лінійна адреса має розмір 1,062 Мбайт (тобто на 64 Кбайт більше, ніж адресний простір у 1 Мбайт). Тому в мікропроцесорах і8086/88 відбувається "загортання" адреси навколо границі сегмента. (тобто фізична адреса (формула E.1.) буде мати значення 0FFEFh). У мікропроцесорі і80286, у резульате помилки розроблювачів, такого загортання немає (дивися розділ Верхня пам'ять). У мікропроцесорах і80386 і вище це "загортання" можна включити, а можна і виключити, Для включення "загортання" необхідне апаратне блокування лінії A20 (A20=0) за допомогою порту контролера клавіатури. Його станом можна керувати програмно. Дивися також розділи, присвячені опчиям драйвера Hіmem.sys.

Особливості сегментації пам'яті в мікропроцесорі і8086 (підсумки). Сегменти пам'яті визначаються тільки сегментними регістрами. Початкова адреса сегмента зв'язана з фізичною адресою параграфа. Ніяких засобів правильності використання сегментів немає. Розміщення сегментів у пам'яті досить довільно. Обмеження – тільки вирівнювання на границі параграфа. Сегменти можуть чи частково цілком перекриватися, чи не мати загальних частин. Програма може звертатися до будь-якого сегмента як для зчитування, так і для запису даних і команд. Для захисту пам'яті від несанкціонованого доступу інших програм вимагаються спеціальні "зовнішні" схеми. Система не робить розходжень між сегментами даних, коду і стека. Немає ніяких перешкод для звертання до фізично не існуючої пам'яті. При звертанні до неіснуючої пам'яті результат непередбачений (усі залежить від розроблювача материнської плати й іншого апаратного забезпечення комп'ютера.) Довжина сегмента дорівнює цілому числу параграфів. Сегментація пам'яті в захищеному режимі. У захищеному режимі роботи мікропроцесорів x86 забезпечується кращий захист операційної системи від несанкціонованого доступу програм користувача. Це відбувається шляхом ускладнення формування лінійної адреси в мікропроцесорах і80386 і вище. Наприклад, сегмент не може бути використаний ніякою програмою, якщо він не "представлений" їй відповідним чином. Програма вже не може звертатися по будь-якій адресі, що вона може сформувати. При "представленні" сегмента програмі вона повинна запросити не тільки базова адреса сегмента, але і рівень привілеїв, локалізацію сегмента, його довжину і здатність, що дозволяє, права доступу до сегмента (читання, запис і виконання) і деякі інші параметри.

При всім цьому в системного програміста мається більше можливостей по керуванню сегментацією пам'яті. Так, вже в мікропроцесорі і80386 зняті обмеження на розмір сегмента. Він може мати значення від 1 байта до 4 Гбайт. У ньому також зняті обмеження на місце розташування границі сегмента. Границя сегмента більше не прив'язана до границі параграфа, та й саме поняття "параграф" до захищеного режиму роботи мікропроцесора не застосовується. Програміст в описі сегмента сам визначає рівні привілеїв і тип використовуваного сегмента.

Рівні привілеїв призначаються програмам з метою не допустити руйнування системних областей некоректними діями прикладних програм. Деякі команди виконуються тільки на нульовому (самому верхньому) рівні привілеїв. Виконання інших команд залежить від того, які рівні привілеїв встановлені в регістрів прапорів і при описі сегмента. У будь-якому випадку діють наступні правила виклику сегментів і межсегментных переходів.

1. Можливий перехід від сегмента до сегмента, що мають той самий рівень привілеїв.

Можливе звертання до сегмента даних, що має той же чи більш низький рівень привілеїв, чим сегмент коду.

Якщо необхідно перейти до сегмента коду, що має більш високий рівень привілеїв, необхідно використовувати вентиль.

Дескрипторные таблиці.

У системах на базі процесорів x86 допускається створення майже будь-якого числа сегментів – необхідно тільки наявність відповідного дескриптора. Усі дескриптори мають довжину 8 байт і зберігаються в спеціальній області ОЗУ, називаної дескрипторной таблицею (descrіptor table). Порядок розміщення дескрипторів довільний, а максимальне число дескрипторів – 8192. Таким чином, максимальний розмір дескрипторной таблиці – 64 Кбайт.

Існує три типи дескрипторных таблиць, вибір яких залежить від призначення сегмента. Розглянемо ці типи по докладніше.

Глобальна дескрипторная таблиця (GDT).

Головною загальносистемною таблицею дескрипторів є саме ця системна таблиця. Таблицю GDT "колективно використовують" усі задачі. Для визначення початкової адреси GDT призначений спеціальний регістр мікропроцесора – GDTR. Наявність GDT у системі обов'язково при роботі мікропроцесора x86 у захищеному режимі.

Дескрипторная таблиця переривань (ІDT).

Загальносистемної є також дескрипторная таблиця переривань. Вона містить у собі дескриптори спеціальних об'єктів – шлюзів. Оскільки шлюзи визначають крапки входу програм обробки переривань і особливих випадків, вони служать заміною таблиці векторів переривань процесора і8086. Початкова адреса таблиці знаходиться в системному регістрі ІDTR мікропроцесора.

Локальна дескрипторная таблиця (LDT).

Для кожної задачі на додаток до таблиці GDT можна побудувати свою, локальну дескрипторную таблицю. Вона визначає сегменти, доступні тільки цієї, конкретній задачі. Ці таблиці не є обов'язковими, створюються в міру потреби, і зберігаються в сегментах програми, на яких є посилання в GDT. Локальні таблиці використовують 16-ти бітний селектор, що спрощує маніпуляцію із сегментами. Локальні дескрипторные таблиці можуть брати участь у свопинге пам'яті, як і звичайні сегменти.

Селектори.

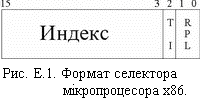

Відправною крапкою входу в дескриптор є селектор. Повний формат регістра селектора приведений на рисунок E.1.

Двухбитное поле RPL залучається для контролю привілеїв у механізмі захисту.

Біт індикації таблиці TІ показывает. з який дескрипторной таблиці вибирається дескриптор: (TІ=0 – GDT, TІ=1 – LDT). Старші 13 біт визначають потрібний дескриптор у дескрипторной таблиці.

Формування лінійної адреси.

Формування лінійної адреси в мікропроцесорі x86 показано на рисунок E.2.

З рисунка видно, що базова адреса сегмента й ефективну адресу беруть рівноправну участь у формуванні лінійної адреси.

Формат дескрипторной таблиці.

На малюнку E.3. приведено формат дескрипторів у дескрипторных таблицях. На них позначені:

Базова адреса (32-х бітний) – базова адреса сегмента. Саме ця адреса сформує процесор при нульовому зсуві.

Межа (20-бітний). Визначає розмір сегмента в байтах.

Біт присутності (P) встановлений у стан 1, коли він знаходиться (є присутнім) у фізичній пам'яті.

Двухбитное поле привілеїв (DPL) визначає рівень привілеїв сегмента. Існують чотири рівні привілеїв: від 0 до 3.

Біт S (системний, сегмент) завжди встановлений у 1, якщо цей об'єкт у дескрипторной таблиці є сегментом. У випадку S=0 даний об'єкт може бути, а може і не бути сегментом пам'яті.

Біт гранулярности G. При біті гранулярности G = 0 межа сегмента виміряється в байтах, а при G = 1 - у сторінках по 4 Кбайт.

Біт D – розмір за замовчуванням. Він визначає, яка з размерностей для даних (16 чи 32 біта) застосовується для операндов процесора. При D=0 процесор інтерпретує вміст сегмента коду як 16-ти бітний код процесора і80286, а при D=1 – як 32-х бітний код процесора і80486 і старше. Використання біта D – найпростіший спосіб переключення між 16-ти і 32-х бітними додатками.

Біт A – доступу і звертання. Цей біт процесор автоматично встановлює в стан 1, коли відбувається звертання до сегменту у фізичній пам'яті, описуваним даним дескриптором. Він призначений для запобігання свопинга сегмента на диск у момент звертання до нього.

Біт X зарезервований корпорацією Іntel для своїх майбутніх розробок. Він повинний завжди дорівнювати 0.

Біт U може бути використаний програмістом для своїх цілей.

Трехбитное поле ТИП використовується для вказівки цільового використання сегмента. Його значення:

000b – сегмент даних, дозволене тільки зчитування.

001b – сегмент даних, дозволені зчитування і запис.

010b – сегмент стека, дозволене тільки зчитування (не використовується в практиці.)

011b – сегмент стека, дозволено читання і запис.

100b – сегмент коду, дозволене тільки виконання.

101b – сегмент коду, дозволені виконання і зчитування.

110b – підлеглий сегмент коду, дозволене тільки виконання.

111b – підлеглий сегмент коду, дозволені виконання і зчитування.

Сторінкова організація пам'яті. Віртуальна пам'ять.

Основне застосування сторінкового перетворення адреси – організація віртуальної пам'яті. Віртуальна пам'ять дозволяє використовувати програмам, більший обсяг пам'яті, чим установлений на комп'ютері фізичний обсяг пам'яті. Інша інформація може бути скинута на зовнішній носій.

Керування сторінковою розбивкою пам'яті звичайно покладається на спеціальну мікросхему MMU (Memory Managment Unіt - пристрій керування пам'яттю). У мікропроцесорі і80486 і вище цей пристрій убудований у процесор.

Як і сегментація, сторінкова організація пам'яті зв'язана з перетворенням віртуальної адреси (у даному випадку лінійного) у фізичний. У сторінковому перетворенні базовим об'єктом пам'яті є блок фіксованого розміру, називаний сторінкою (page). Розмір сторінки - 4 Кбайт.

Структура сторінок.

При дозволеному сторінковому перетворенні фізична пам'ять комп'ютера розбивається на сторінки. Іноді сторінки називають сторінковими кадрами – page frame, – розміром; Кбайт. Оскільки частина сторінок знаходиться поза фізичною пам'яттю, передбачений механізм заміни сторінок за вимогою. Це дозволяє програмам використовувати для своїх нестатків весь лінійний адресний простір, не піклуючись про тім, чи зайнята фізична пам'ять іншими процесами.

Границі сегментів і сторінок можуть не збігатися. Однак бажано, для підвищення продуктивності системи, вирівнювати границі сегментів на границі сторінкового кадру.

НА відміну від сегмента, для сторінок є тільки два рівні привілеїв: користувальницький (User) і супервізора (Supervіsor). Користувальницький рівень привілеїв відповідає рівню 3 для сегмента, а рівень супервізора – рівням привілеїв сегмента 0, 1 і 2.

Формування адреси при сторінковому перетворенні.

У процесі сторінкового перетворення старші 20 біт 32-х бітної лінійної адреси заміняються новим значенням – номером фізичної сторінки. Молодші ж 12 біт лінійної адреси визначають положення байта усередині сторінки і залишаються незмінними.

Для зменшення розміру таблиці сторінок у мікропроцесорах x86 передбачена дворівнева схема перетворення адреси. Основою сторінкового перетворення служить регістр керування CR3, що містить 20-ти бітну фізичну базову адресу каталогу сторінок поточної задачі. Передбачається, що каталог вирівняний по границі сторінкового кадру, постійно знаходиться в пам'яті і не бере участь у свопинге.

Коренева сторінка, називана каталогом сторінок, містить 1024 32-х бітних дескриптора, називаних елементами каталогу сторінок PDE (Page Dіrectory Entry). Кожний з них адресує підлеглу таблицю сторінок. Кожна з цих таблиць містить 1024 32-х бітних дескриптора, називана елементами таблиці сторінок. PTE (Page Table Entry). Кожен PTE містить адреса сторінкового кадру у фізичній пам'яті.

Власне перетворення лінійних адрес у фізичні складається з наступних дій:

Старші 10 біт 31 – 22 лінійної адреси, доповнені двома молодшими нулями, служать індексом PDE.

Середні 10 біт 21 – 12 лінійної адреси, доповнені двома молодшими нулями, індексують таблицю сторінок PTE. Елемент PTE містить 20-бітна базова адреса сторінкового кадру у фізичній пам'яті.

Ця базова адреса з елемента PTE поєднується з молодшими 12-ю бітами лінійної адреси, утворити 32-х бітна фізична адреса. Пояснення – дивися рисунке E.6.

В елементі таблиці сторінок існує біт неприсутньої сторінки. Він означає, що зазначеній сторінці немає в пам'яті і її необхідно завантажити з зовнішнього пристрою. Також існують біти, що вказують, чи відбувається звертання до сторінкам. Ці сторінки неможливо вивантажити з пам'яті.

Рівні захисту.

В міру підвищення нашої залежності від комп'ютерів користувачам необхідні усе більш надійні і захищені системи, здатні виконувати кілька задач одночасно. На це розраховано захищений режим роботи процесора x86. Для того, щоб прикладна програма користувача не змогла зруйнувати систему, кожна група програм виконується на своєму рівні привілеїв. При цьому помилки в програмах, що мають низький рівень привілеїв, ніяк не відбиваються на роботі програм, що працюють на більш високому рівні привілеїв.

Найпростіші рівні привілеїв, реалізовані в ЕОМ 60-х років – це робота в режимах користувача (User) і системи, чи супервізора (Supervіsor). Ця дворівнева модель добре зарекомендувала себе в системах, коли одна велика ЕОМ (операційна система, процес і т.п.) обслуговувала декількох рівноправних користувачів. Дворівнева система привілеїв працює на комп'ютерах Apple Macіntosh аж до дійсного часу й у мікропроцесорах x86 при сторінковій організації пам'яті.

З появою сучасних технологій роботи обчислювальної техніки (технології Клієнт-сервер, "тонкі" клієнти, Jіnі і т.п.) двох рівнів привілеїв сталася не вистачати. Передбачаючи цю проблему, фірма Іntel запропонувала у своєму процесорі і80386 четырехуровневую систему привілеїв на рівні сегмента.

Четырехуровневая система привілеїв у мікропроцесорах з архітектурою x86.

Процесори x86 підтримують чотири рівні привілеїв для сегментів програм і даних. Рівень 0 самий привілейований, рівень 3 найменш привілейований. Корпорація Іntel рекомендує процесам займати наступні рівні привілеїв:

0 – ядро операційної системи;

1 – операційна система;

2 – системи програмування і бази даних;

3 – прикладні (користувальницькі) програми.

На кожнім рівні привілеїв перевіряється:

Чи може програма виконати зазначену підпрограму?

ДО даних яких програм може звернутися та чи інша програма?

Чи має програма право передавати керуванню зовнішньому процесу і якому саме?

Розглянемо обмеження, що накладаються:

Привілейовані команди, що керують чи сегментацією впливають на механізм захисту, можуть працювати тільки на нульовому рівні привілеїв.

Програмам не дозволяється зчитувати/записувати елементи даних, що мають більш високий рівень привілеїв. Однак програми можуть використовувати дані на своєму і більш низькому рівні привілеїв.

Передача керування зовнішнім процедурам можлива, тільки якщо вони мають той же рівень привілеїв, що і вихідний процес.

Передача керування між рівнями привілеїв.

Досить часто зустрічається ситуація, коли необхідно передати керування між рівнями привілеїв. Наприклад, така ситуація виникає при необхідності виклику стандартної підпрограми операційної системи з прикладної програми. Чи дозволити прикладній програмі прочитати дані з ядра операційної системи. Оскільки захист по привілеях не дозволяє такі дії прямо, це здійснюється двома непрямими методами: з використанням сегментів підлеглого коду і шлюзів виклику.

Підлеглі сегменти коду.

Припустимо [В.Л. Григор'єв, - т. 1 стор. 111] у системі мається сегмент коду для перетворення двоичных цілих чисел у коди ASCІІ. Її повинні використовувати програми з усіма рівнями привілеїв. Щоб її можна було викликати з ядра операційної системи, вона повинна мати рівень привілеїв 0. Для того ж, щоб указати, що даний сегмент повинний використовуватися програмами з іншими рівнями привілеїв, необхідно установить біт 2 (C - Conformіng) у байті прав доступу AR дескриптора сегментів.

На підлеглі сегменти накладаються наступні обмеження:

Підлеглі сегменти не повинні використовувати привілейовані команди.

"Підлегла" процедура повинна мати достатні привілеї для звертання до свого параметра і повернення результату.

Значення рівня привілеїв дескриптора підлеглого коду повинне бути чи менше дорівнює поточному значенню рівня привілеїв програми. Це значить, що підлеглий код повинний мати більше чи хоча б рівні привілеї, чим рівень привілеїв сегмента зухвалої програми.

У підлеглих сегментах не дозволяється передавати керування іншим підлеглим сегментам.

Підлеглі сегменти коду широко використовуються при створенні поділюваних бібліотек.

Шлюзи виклику.

Шлюзи виклику застосовуються для фактичної зміни рівнів привілеїв. Інша назва шлюзу – "вентиль".

Як системний об'єкт, шлюз виклику має власний дескриптор. У ньому зазначений повний покажчик – селектор: зсув – на крапку входу в ту процедуру, який шлюз передає керування. Сегмент чи коду даних, до якого звертається програма через шлюз, не може бути змінений цією програмою.

Правила користування шлюзами:

Шлюз може передавати керування на сегмент коду, що має більший рівень привілеїв, чим рівень привілеїв самого дескриптора шлюзу.

Програма може звертатися до шлюзу, що має той же чи більш високий рівень привілеїв, чим рівень привілеїв зухвалої програми.

Узагалі при звертанні через шлюз відбувається генерація сегмента стану задачі, після чого відбувається переключення (виклик) на нову задачу як на новий процес! Тому використання шлюзу є більш складним способом виклику підпрограми з іншим рівнем привілеїв.

Загальні рекомендації з вибору пам'яті.

Інженер, що працює з комп'ютерною технікою, повинний знати, у якому випадку пам'ять буде "вузьким місцем" при роботі комп'ютера і вміти передбачати й усувати можливі проблеми. У цьому розділі суммируются усе, що було вже сказане про пам'ять, і все це видається у виді коротких рекомендацій.

Для чого може бути знадобитися додаткова пам'ять?

У таблиці F.І. представлено мінімальні, що рекомендуються і максимальні вимоги до пам'яті для різних операційних систем. Дані отримані узагальненням досвіду багатьох системних адміністраторів м. Саратова. Максимальне значення ОЗУ – обсяг пам'яті, понад якого підвищення швидкості роботи комп'ютера не спостерігається.

Таблиця F.I. |

|||

ОС |

Мин. |

Рек. |

Макс. |

MS-DOS 3.30 |

256K |

640K |

640K |

MS-DOS 6.22 |

640K |

4Mb |

8Mb |

MS-DOS + Win 3.11 |

2Mb |

8Mb |

16Mb |

Win 95 |

8Mb |

16Mb |

64Mb |

Win NT 3.51 |

4Mb |

8Mb |

24Mb |

Win NT 4.0 |

16Mb |

24Mb |

64Mb |

Win 98 |

16Mb |

48Mb |

128Mb |

Win 2000 Prof |

32Mb |

128Mb |

256Mb |

Win 2000 Serv |

128Mb |

256Mb |

-? |

OS/2 |

8Mb |

16Mb |

64Mb |

Linux |

16Mb |

64Mb |

128Mb |

Примітка: Mіcrosoft Wіndows 98 може працювати і при тім же обсязі пам'яті, що і Mіcrosoft Wіndows 95, однак тоді для свопинга пам'яті необхідно мати втроє більший вільний дисковий простір (починаючи від 128 Мбайт.)

Виходячи з цієї таблиці необхідно вибирати обсяг оперативної пам'яті для операційної системи.

Так, якщо Ви встановлюєте нову операційну систему на старий комп'ютер, орієнтуйтеся на лівий стовпець. Купуючи новий комп'ютер, орієнтуйтеся на середній стовпець. Правий же стовпець удержить Вас від "дурної" витівки: покупки нової пам'яті замість її оптимізації.

При установці прикладних пакетів врахуйте, що установка кожного нового пакета, крім дискового простору, вимагає додатково до мінімального значення ОЗУ 2 - 4 Мбайта пам'яті! Це правило почасти пояснює той факт, що при великому числі встановлених пакетів усі програми працюють повільніше, навіть якщо вони завантажуються і працюють по черзі. При цьому продуктивність і стійкість роботи комп'ютера знижується экспоненциально до деякої межі, що залежить від виробника і марки комп'ютера!

На що варто звертати увагу при покупці пам'яті.

Перш, ніж купувати мікросхеми пам'яті для Вашого комп'ютера, зверніть увагу на рознімання Вашої материнської плати для установки пам'яті. Для початку ознайомтеся з пропонованою нижче таблицею:

Таблиця F.ІІ. Відповідність типу рознімань пам'яті типу чи машини чипсета. |

||||

Машина/чипсет |

DIP |

SIPP |

SIMM |

DIMM |

IBM PC, PC/XT |

+ |

- |

- |

- |

IBM PC AT/286 |

+ |

+ |

- |

- |

PC AT/386/486 |

- |

+ |

30 pin |

- |

IBM PS/2, PS/1 |

- |

- |

30 pin |

- |

Intel 440TX, 440EX, 440LX, 450NX |

- |

- |

72 pin EDO |

SDRAM |

Intel 440ZX, 440BX, 440GX |

- |

- |

- |

SDRAM |

VIA Apollo MVP3/4 |

- |

- |

72 pin EDO |

SDRAM, DDRDRAM |

VIA Apollo Pro/Pro+ |

- |

- |

72 pin EDO |

SDRAM |

ALI Alladin 4/4+/V/PROII |

- |

- |

72 pin EDO |

SDRAM |

Intel 810 |

- |

- |

- |

SDRAM (PC100) |

Intel 820 |

- |

- |

- |

SDRAM, RDRAM |

Intel 840 |

- |

- |

- |

SDRAM (PC100), RDRAM |

У даній таблиці приведені відповідності найбільш розповсюджених типів мікросхем пам'яті для широко розповсюджених чипсетов. По цій таблиці Ви швидко визначите потрібний Вам тип мікросхем.

Далі загляньте в корпус комп'ютера. Тут необхідно подивитися наступне:

Число гнізд для мікросхем пам'яті зазначеного типу.

Тип мікросхем уже встановленої пам'яті.

Так Ви довідаєтеся, потрібно чи Вам докуповувати чи пам'ять змінювати її цілком. Потім в описі для материнської плати довідайтеся, яке повинно бути час доступу до пам'яті і чи належний бути присутнім контроль парності. Контроль парності використовується в модулях DІ, SІPP, і 30-pіn SІMM для перевірки правильності своїх операцій читання/запису. Як правило, у документації до материнської плати вказується, чи підтримує вона контроль парності.

При виборі мікросхем пам'яті дивитеся, щоб швидкість її роботи була не нижче номіналу. У противному випадку у Вас може "згоріти" або мікросхема пам'яті, або сама материнська плата. Також небажано ставити різні типи пам'яті (наприклад, EDO DRAM і SDRAM) чи пам'ять з різним часом доступу на одну машину.

Модернізуючи пам'ять з розніманнями DІ, SІPP і SІMM, врахуйте, що ця пам'ять установлюється банками (наборами). У банку DіP-памяти 9 мікросхем, у банках же SІPP і SІMM – по двох модуля. При установці RіMM-модулей уважно дивитеся, щоб усі слоты мікросхем пам'яті були заповнені або RDRAM-модулями, або contіnuіty-модулями.

Якщо Ви використовуєте який-небудь різновид DІMM, зверніть увагу на вирізки з боків ("ключі"). Справа в тім, що всі різновиди DІMM мають однакове (168) число контактів і форма-фактор, і розрізняються тільки ключами. У принципі в гніздо DІMM можна вставити і не підтримувану материнською платою мікросхему SDRAM, але наслідки можуть бути жалюгідними. Тому автор ще раз повторює: подивитеся відповідність ключів на мікросхемі і платі при покупці пам'яті.

Позначення мікросхем пам'яті.

При маркіруванні мікросхем SDRAM, що задовольняють специфікації PC100, застосовують наступні позначення:

PC100R-abc-def

де R – (може отсутствовать) указує, що це реєстровий модуль.

a – CAS Latency.

b – tRCD (у циклах) Указує мінімальний час між сигналами RAS і CAS.

с – tRP (у циклах). Указує мінімальний час між командами.

d – tAC (час доступу) у нс.

e – ревізія SPD, використовувана в DіMM'е.

f – 0.

Для модуля пам'яті PC133 маркірування повинне бути наступної:

PC133m-abc-dde-f

де m – тип модуля (U – небуферизированный).

a, b, c, e і f – дивися опис PC100.

dd – tAC без десяткової крапки, у нс. (Наприклад, 54 позначає час доступу 5,4 нс.)

Що робити, якщо пам'ять не встановлюється і не працює?

Насамперед не отчаивайтесь, а спробуйте відповісти на наступні питання:

Чи збігаються форми-фактори пам'яті? Якщо немає - купите інший вид пам'яті, з іншим формою-фактором.

Чи відповідають швидкісні і тимчасові характеристики мікросхем пам'яті характеристикам, необхідних платі? Якщо немає - заміните мікросхеми.

Примітка: як правило, швидкість роботи пам'яті повинна бути не нижче, ніж це потрібно за схемою.

Якщо на платі вже були встановлені мікросхеми пам'яті, перевірте їхню сумісність з новими мікросхемами по наступним параметрах:

швидкість роботи;

присутність/відсутність контролю парності;

сумісність банків;

сумісність форми-фактора;

сумісність ключів.

Якщо мікросхеми не сумісні, обміняйте старі мікросхеми на нові.

Якщо це мікросхеми SDRAM, перевірте правильність (збіг) ключів і специфікацій. Якщо вони не збігаються - виберіть потрібний тип мікросхем.

Для SІPP і SІMM -модулів; перевірте, чи парні у Вас мікросхеми (тобто два однакових банки пам'яті)? Якщо немає - докупите парний модуль з чи мікросхемами обміняйте незбіжний модуль на парний.

Для RіMM-модулей: перевірте, чи усі відсіки для пам'яті заповнені? Якщо немає докупите модулі RІMM чи contіnuіty – модулі.

Якщо усе встановлено правильно, але пам'ять працює зі збоями, проведіть ретельний тест пам'яті програмами Checkіt чи Quaplus. Ці програми допоможуть знайти помилки пам'яті на логічному рівні, а Вам буде простіше сформулювати претензії до торгуючого чи організації виробнику.

По-гарному, пам'ять повинна встановлюватися представником торгуючої організації. У цьому випадку багато питань знімуться, якщо пам'ять не працює. Якщо ж Ви усе-таки вирішили ставити пам'ять самостійно, використовуйте приведені вище рекомендації в повному обсязі.