- •1. Общие принципы организации системы ввода-вывода.

- •1.3.1 Организация свв универсальных эвм

- •1.3.2 Организация свв управляющих эвм

- •1.3.2.1 Порты ввода-вывода

- •1.3.2.2 Дискретные порты ввода-вывода

- •1.3.2.3 Однонаправленные порты

- •1.3.2.4 Двунаправленные порты и порты с альтернативной функцией

- •1.3.2.5 Аналого-цифровой преобразователь

- •1.3.2.6 Цифро-аналоговый преобразователь

- •1.3.2.7 Устройства сопряжения с объектом (усо) управляющих эвм

- •3 Аппаратные интерфейсы вычислительных систем

- •3.1 Характеристики аппаратных интерфейсов

- •3.2 Функции аппаратных интерфейсов

- •3.3 Классификация аппаратных интерфейсов

- •1.2.1 Процессор и память

- •1.2.2 Контроллер ввода-вывода

- •1.2.3 Процессор ввода-вывода

- •3.6 Внутрисистемный интерфейс amba

- •3.6.1 Внутрисистемный интерфейс amba ahb

- •3.6.2 Системный интерфейс amba asb

- •3.6.3 Периферийный интерфейс amba apb

- •3.3 Классификация аппаратных интерфейсов

- •3.7 Системные интерфейсы

- •3.7.1 Интерфейс pci

- •3.7.2 Интерфейс pci Express

- •3.9 Малые периферийные интерфейсы

- •3.9.1 Интерфейс rs-232

- •3.9.1.1 Сигнальные линии последовательного интерфейса

- •3.9.1.2 Управление потоком

- •3.9.1.3 Разъемы и кабели

- •3.9.1.4 Формат последовательной передачи данных

- •3.9.1.5 Работа с последовательным каналом

- •3.9.2 Интерфейс spi

- •3.9.2.1 Типы подключения к шине spi

- •3.9.2.2 Режимы работы шины spi

- •3.9.2.3 Достоинства шины spi

- •3.9.2.4 Недостатки шины spi

- •3.9.3 Интерфейс Centronics

- •3.9.4 Интерфейс sata

- •3.9.4.1 Физический интерфейс Serial ata

- •3.5.7 Приемопередатчик последовательного интерфейса

- •3.5.8 Особенности параллельных интерфейсов

- •1.3.2.7 Устройства сопряжения с объектом (усо) управляющих эвм

- •1.3.2.1 Порты ввода-вывода

- •1.3.2.2 Дискретные порты ввода-вывода

- •1.3.2.3 Однонаправленные порты

- •1.3.2.4 Двунаправленные порты и порты с альтернативной функцией

- •3.10.3.6 Синхронизация

- •3.9.2 Интерфейс spi

- •3.9.2.1 Типы подключения к шине spi

- •3.9.2.2 Режимы работы шины spi

- •3.9.2.3 Достоинства шины spi

- •3.9.2.4 Недостатки шины spi

- •3.10.3Интерфейс i2c

- •3.10.3.1 Концепция шины i2c

- •3.10.3.2 Реализация монтажного и и монтажного или

- •3.10.3.3 Принцип работы шины i2c

- •3.10.3.4 Сигналы старт и стоп

- •3.10.3.5 Подтверждение

- •3.10.3.6 Синхронизация

- •3.10.3.7 Форматы обмена данными по шине i2c (7-битный адрес)

- •3.10.3.8 Арбитраж

- •3.10.3.9 Достоинства шины i2c

- •3.10.4Интерфейс usb

- •3.10.4.1 Модель передачи данных

- •3.10.4.2 Протокол

- •1.3.2.5 Аналого-цифровой преобразователь

- •1.3.2.6 Цифро-аналоговый преобразователь

- •3.5.10Устройства гальванической изоляции в аппаратных интерфейсах

- •3.5.10.1 Dc/dc преобразователи

- •3.5.10.2 Реализация гальванической изоляции дискретного выхода модуля ввода-вывода sdx-09

- •3.5.10.3 Реализация гальванической изоляции дискретного входа модуля ввода-вывода sdx-09

- •3.5.10.4 Реализация гальванической изоляции rs-232 в контроллере

- •3.5.10.5 Технология iCoupler фирмы Analog Devices

3.10.3.6 Синхронизация

При передаче посылок по шине I²C каждый ведущий генерирует свой синхросигнал на линии SCL. Данные действительны только во время ВЫСОКОГО состояния синхроимпульса [13, 81].

Синхронизация выполняется с использованием подключения к линии SCL по правилу монтажного И. Это означает, что ведущий не имеет монопольного права на управление переходом линии SCL из НИЗКОГО состояния в ВЫСОКОЕ. В том случае, когда ведомому необходимо дополнительное время на обработку принятого бита, он имеет возможность удерживать линию SCL в НИЗКОМ состоянии до момента готовности к приему следующего бита. Таким образом, линия SCL будет находиться в НИЗКОМ состоянии на протяжении самого длинного НИЗКОГО периода синхросигналов.

Устройства с более коротким НИЗКИМ периодом будут входить в состояние ожидания на время, пока не кончится длинный период. Когда у всех задействованных устройств кончится НИЗКИЙ период синхросигнала, линия SCL перейдет в ВЫСОКОЕ состояние. Все устройства начнут проходить ВЫСОКИЙ период своих синхросигналов. Первое устройство, у которого кончится этот период, снова установит линию SCL в НИЗКОЕ состояние. Таким образом, НИЗКИЙ период синхролинии SCL определяется наидлиннейшим периодом синхронизации из всех задействованных устройств, а ВЫСОКИЙ период определяется самым коротким периодом синхронизации устройств.

Механизм синхронизации может быть использован приемниками как средство управления пересылкой данных на байтовом и битовом уровнях.

На уровне байта, если устройство может принимать байты данных с большой скоростью, но требует определенного времени для сохранения принятого байта или подготовки к приему следующего, то оно может удерживать линию SCL в НИЗКОМ состоянии после приема и подтверждения байта, переводя таким образом передатчик в состояние ожидания.

На уровне битов устройство, такое как микроконтроллер без встроенных аппаратных цепей I²C или с ограниченными цепями, может замедлить частоту синхроимпульсов путем продления их НИЗКОГО периода. Таким образом скорость передачи любого ведущего адаптируется к скорости медленного устройства.

189

3.10.3.7 Форматы обмена данными по шине i2c (7-битный адрес)

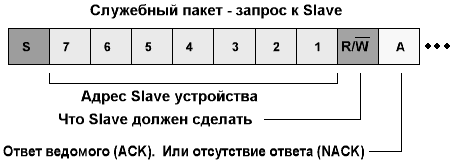

После сигнала СТАРТ посылается адрес ведомого. После 7 бит адреса следует бит направления данных (R/W), «0» означает передачу (запись), а «1» – прием (чтение). Пересылка данных всегда заканчивается сигналом СТОП, генерируемым ведущим [13, 46, 81]. Однако, если ведущий желает оставаться на шине дальше, он должен выдать повторный сигнал СТАРТ и затем адрес следующего устройства. При таком формате посылки возможны различные комбинации чтения/записи.

Рис. 111. Первый байт после СТАРТ-состояния (адресный байт).

Возможные форматы:

1. Ведущий-передатчик передает данные ведомому-приѐмнику.

Направление пересылки данных не изменяется (запись W = 0) [1346].

Рис. 112. Запись данных.

2. Ведущий читает ведомого немедленно после пересылки первого байта.

В момент первого подтверждения ведущий-передатчик становится ведущим-приѐмником, и ведомый-приѐмник становится ведомым- передатчиком. Подтверждение тем не менее генерируется ведущим. Сигнал СТОП генерируется ведущим. В таком формате посылки есть тонкость: при приеме последнего байта надо дать ведомому понять, что больше ведущий читать не будет и отослать NACK на последнем байте. Если же отослать ACK, то после СТОП-сигнала ведущий не отпустит линию (объясняется работой автомата в контроллере I2C). Так что прием двух байтов будет выглядеть так (чтение R = 1):

190

Рис. 113. Чтение данных.

3. Комбинированный формат. При изменении направления пересылки данных повторяется сигнал СТАРТ и адрес ведомого, но бит направления данных инвертируется. Если ведущий-приѐмник посылает повторный сигнал СТАРТ, он обязан предварительно послать сигнал неподтверждения [13, 46, 81].

Рис. 114. Чтение данных с указанного адреса.

Такой формат пересылки используется, например, когда необходимо прочитать данные из памяти (EEPROM), часов реального времени и др. по определенному адресу. Таким образом, сначала в ведомое устройство записывается адрес чтения данных (на рисунке выше это адрес ячейки 0x05), т.е. выполняется инициализация счетчика адреса ведомого устройства; затем

191

делается повторный старт (RS), после чего читаются данные по заданному ранее адресу.