- •1. Общие принципы организации системы ввода-вывода.

- •1.3.1 Организация свв универсальных эвм

- •1.3.2 Организация свв управляющих эвм

- •1.3.2.1 Порты ввода-вывода

- •1.3.2.2 Дискретные порты ввода-вывода

- •1.3.2.3 Однонаправленные порты

- •1.3.2.4 Двунаправленные порты и порты с альтернативной функцией

- •1.3.2.5 Аналого-цифровой преобразователь

- •1.3.2.6 Цифро-аналоговый преобразователь

- •1.3.2.7 Устройства сопряжения с объектом (усо) управляющих эвм

- •3 Аппаратные интерфейсы вычислительных систем

- •3.1 Характеристики аппаратных интерфейсов

- •3.2 Функции аппаратных интерфейсов

- •3.3 Классификация аппаратных интерфейсов

- •1.2.1 Процессор и память

- •1.2.2 Контроллер ввода-вывода

- •1.2.3 Процессор ввода-вывода

- •3.6 Внутрисистемный интерфейс amba

- •3.6.1 Внутрисистемный интерфейс amba ahb

- •3.6.2 Системный интерфейс amba asb

- •3.6.3 Периферийный интерфейс amba apb

- •3.3 Классификация аппаратных интерфейсов

- •3.7 Системные интерфейсы

- •3.7.1 Интерфейс pci

- •3.7.2 Интерфейс pci Express

- •3.9 Малые периферийные интерфейсы

- •3.9.1 Интерфейс rs-232

- •3.9.1.1 Сигнальные линии последовательного интерфейса

- •3.9.1.2 Управление потоком

- •3.9.1.3 Разъемы и кабели

- •3.9.1.4 Формат последовательной передачи данных

- •3.9.1.5 Работа с последовательным каналом

- •3.9.2 Интерфейс spi

- •3.9.2.1 Типы подключения к шине spi

- •3.9.2.2 Режимы работы шины spi

- •3.9.2.3 Достоинства шины spi

- •3.9.2.4 Недостатки шины spi

- •3.9.3 Интерфейс Centronics

- •3.9.4 Интерфейс sata

- •3.9.4.1 Физический интерфейс Serial ata

- •3.5.7 Приемопередатчик последовательного интерфейса

- •3.5.8 Особенности параллельных интерфейсов

- •1.3.2.7 Устройства сопряжения с объектом (усо) управляющих эвм

- •1.3.2.1 Порты ввода-вывода

- •1.3.2.2 Дискретные порты ввода-вывода

- •1.3.2.3 Однонаправленные порты

- •1.3.2.4 Двунаправленные порты и порты с альтернативной функцией

- •3.10.3.6 Синхронизация

- •3.9.2 Интерфейс spi

- •3.9.2.1 Типы подключения к шине spi

- •3.9.2.2 Режимы работы шины spi

- •3.9.2.3 Достоинства шины spi

- •3.9.2.4 Недостатки шины spi

- •3.10.3Интерфейс i2c

- •3.10.3.1 Концепция шины i2c

- •3.10.3.2 Реализация монтажного и и монтажного или

- •3.10.3.3 Принцип работы шины i2c

- •3.10.3.4 Сигналы старт и стоп

- •3.10.3.5 Подтверждение

- •3.10.3.6 Синхронизация

- •3.10.3.7 Форматы обмена данными по шине i2c (7-битный адрес)

- •3.10.3.8 Арбитраж

- •3.10.3.9 Достоинства шины i2c

- •3.10.4Интерфейс usb

- •3.10.4.1 Модель передачи данных

- •3.10.4.2 Протокол

- •1.3.2.5 Аналого-цифровой преобразователь

- •1.3.2.6 Цифро-аналоговый преобразователь

- •3.5.10Устройства гальванической изоляции в аппаратных интерфейсах

- •3.5.10.1 Dc/dc преобразователи

- •3.5.10.2 Реализация гальванической изоляции дискретного выхода модуля ввода-вывода sdx-09

- •3.5.10.3 Реализация гальванической изоляции дискретного входа модуля ввода-вывода sdx-09

- •3.5.10.4 Реализация гальванической изоляции rs-232 в контроллере

- •3.5.10.5 Технология iCoupler фирмы Analog Devices

3.6.1 Внутрисистемный интерфейс amba ahb

Внутрисистемный интерфейс AHB (Advanced High-performance Bus – расширенная высокопроизводительная шина) предназначен для объединения быстродействующих, высокопроизводительных модулей, работающих на высоких тактовых частотах.

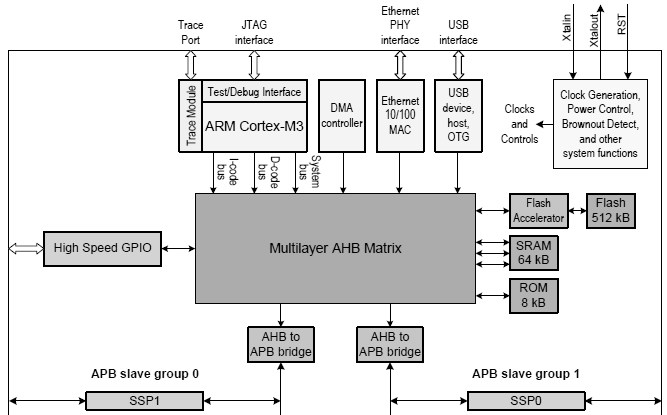

Рис. 63. Схема типичного микроконтроллера на базе шины AMBA-AHB.

Рис. 64. Пример использования шины AMBA AHB в микроконтроллере NXP LPC1768 на базе Cortex-M3.

AHB позволяет соединить ядро микропроцессора с внутренними и внешними модулями памяти, контроллерами ПДП, быстродействующими сетевыми контроллерами Fast Ethernet, контроллерами USB-2.0 и т.д.

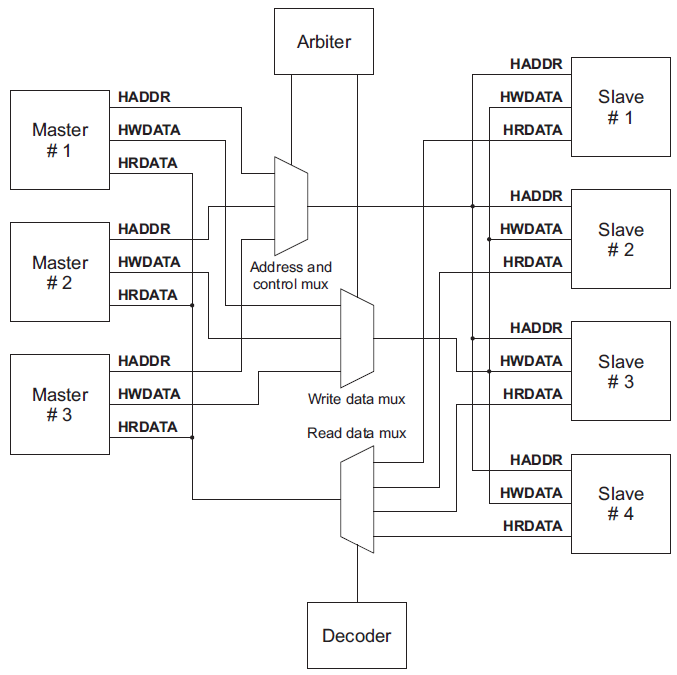

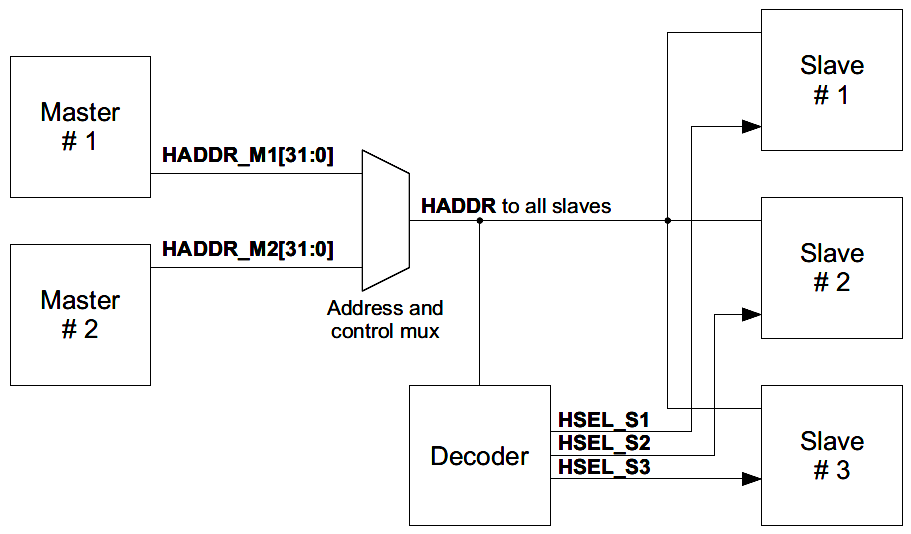

Рис. 65. Схема взаимодействия главных и подчиненных устройств, подключенных к шине AMBA AHB.

На рисунке показан фрагмент структуры микроконтроллера NXP LPC1768, выполненного на базе ядра ARM Cortex-M3. На схеме видно, что шиной AHB объединены вместе практически все элементы микроконтроллера, требующие большой скорости обмена данными. Через два моста, к шине AHB подключены две независимые шины APB, к которым подключаются сравнительно медленные периферийные устройства (UART, I2C, таймеры и так далее).

На рисунке шина AHB названа Matrix (матрица). Такое название справедливо, так как на самом деле шина является коммутатором, матрицей, связывающей несколько устройств попарно друг с другом в различные моменты времени. На рисунке ниже можно посмотреть реализацию шины AHB.

Мы видим, что арбитр шины управляет мультиплексорами, к которым подключены шины адреса и шины записи данных из главных устройств (Master) в подчиненные (Slave). Декодер управляет мультиплексором, через который считываются данные с подчиненных устройств. Хорошо видно, что для записи и чтения существуют раздельные шины.

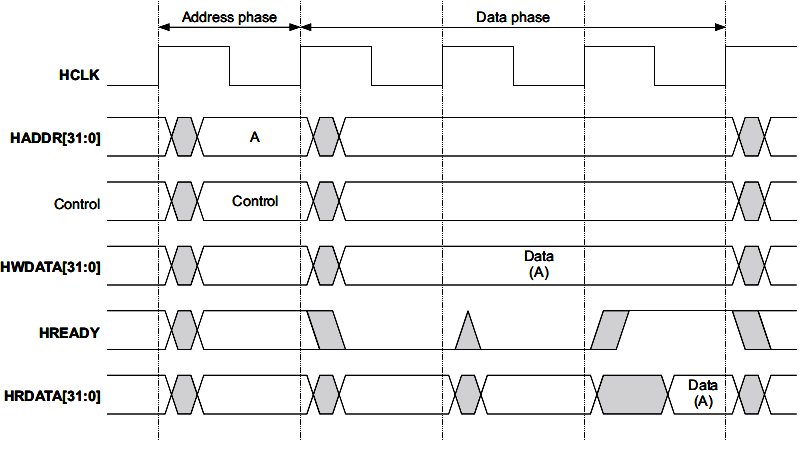

Рис. 66. Простой обмен данными на шине AMBA AHB.

Опишем простой вариант обмена данными на шине AMBA AHB:

1. Главное устройство выставляет адрес и управляющие сигналы по фронту сигнала HCLK.

2. Подчиненное устройство считывает значения с шины адресы (HADDR)

и шины управления (Control) на следующем фронте HCLK.

3. После считывания адреса и данных подчиненное устройство может выдать ответ на шину в этом же цикле (сигнал HREADY активен).

4. Главное устройство считывает данные, выставленные подчиненным устройством в третьем цикле шины.

Подчиненное устройство может вставлять такты неготовности, используя сигнал HREADY (см. рисунок выше). Такт неготовности – это такой такт, во время которого обмен по шине не производится вследствие отсутствия готовых данных у одного из устройств.

119

Рис. 67. Передача данных с тактами неготовности.

В отличие от предыдущего рисунка здесь хорошо видно, что во втором и третьем тактах шины сигнал HREADY равен нулю. Такты неготовности используются для того, чтобы синхронизировать быстрое главное устройство и более медленное подчиненное.

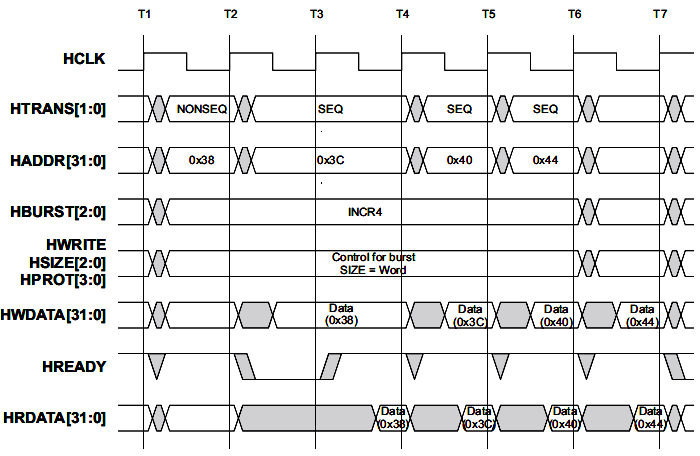

Рис. 68. Пример различных типов обмена на шине.

В зависимости от состояния сигнала HTRANS[1:0] может быть выделено четыре типа передач на шине:

1. IDLE. Передача данных не требуется.

2. BUSY. Позволяет вставлять IDLE циклы в середину пакетной передачи.

3. NONSEQ. Индицирует начало одиночной или пакетной передачи. Адрес установленный в предыдущем цикле шины игнорируется.

120

4. SEQ. Показывает, что адрес в новом цикле шины инкрементируется на

1, а сигналы на шине управления такие же.

Тип пакетной передачи определяется сигналом HBURST[2:0]. Существует

8 вариантов пакетной передачи:

1. SINGLE (000) – одиночная передача.

2. INCR (001) – инкрементная передача с неизвестной длиной.

3. WRAP4 (010) – циклическое окно на 4 адреса.

4. INCR4 (011) – инкрементная передача на 4 адреса.

5. WRAP8 (100) – циклическое окно на 8 адресов.

6. INCR8 (101) – инкрементная передача на 8 адресов.

7. WRAP16 (110) – циклическое окно на 16 адресов.

8. INCR16 (111) – инкрементная передача на 16 адресов.

Режим WRAP (циклическое окно) позволяет работать циклически, по кругу, в заданном окне адресов. Режим INCR предполагает простой инкремент (прибавление на единицу) адреса в каждом цикле шины.

Рис. 69. Пример использования режима WRAP4.

121

Рис. 70. Пример использования режима INCR4.

При передаче данных сигнал HWRITE становится активным (переводится в логическую «1»). В зависимости от состояния линий HSIZE[2:0] передаваться за один раз может 8, 16, 32, 64, 128, 256, 512 или 1024 бита данных. Эти биты (HSIZE) работают совместно с сигналами HBURST.

Рис. 71. Выбор подчиненного устройства с помощью сигналов HSEL.

Сигнал HPROT[3:0] определяют уровень защиты передаваемой информации: код операции, доступ к данным, пользовательский доступ, привилегированный доступ и так далее.

Выбор подчиненного устройство происходит с помощью декодера адреса, формирующего сигналы HSEL.

122

Сигнал HREADY используется для информирования главного устройства о завершении или продолжении передачи данных. Если уровень этого сигнала активный, то передача данных завершена.

Рис. 72. Пример использования сигнала HRESP.

Сигнал HRESP[1:0] используется для подтверждения транзакции. Его значениями могут быть: OKAY – транзакция завершена успешно, ERROR – ошибка, RETRY – повторить попытку, SPLIT – данные переданы не полностью.

Сигналы HWDATA[31:0] используются для передачи данных от главного устройства к подчиненным.

Сигналы HRDATA[31:0] используются для передачи данных от подчиненных устройств к главным.

Арбитраж используется для того, чтобы только один мастер имел доступ к шине в один момент времени. Рассмотрим основные сигналы:

HBUSREQx – запрос шины у арбитра шины.

HLOCKx – сигнал, выставляемый мастером и означающий захват шины.

HGRANTx – сигнал, выставляемый арбитром и обозначающий, что мастер получил доступ к шине.

HMASTER[3:0] – сигнал показывающий номер мастера, захватившего шину.

123

Рис. 73. Пример арбитража.

На рисунке видно, что в первом такте шины главное устройство выставляет сигнал запроса шины HBUSREQx. В третьем такте арбитр подтверждает захват шины сигналом HGRANTx. На четвертом такте арбитр выставляет сигнал HMASTER с номером главного устройства, захватившего шину.