- •8.4. Средства и методы разработки программного обеспечения

- •8.4.2. Программные средства поддержки проектирования/

- •8.5.1. Программные системы моделирования

- •8.5.2. Прототипные платы

- •8.5.3. Эмуляторы пзу

- •8.5.4. Внутрисхемные эмуляторы

- •8.5.5. Интегрированные среды разработки (оболочки)

- •8.6.1. Программаторы

- •8.6.2. Логические анализаторы

- •8.6.3. Встроенные в мп средства отладки

- •8.7. Операционные системы реального времени

- •8.8. Jtag-интерфейс и системные функции на его основе

- •8.9. Процедура проектирования и сведения

- •8.9.2. Последовательность проектирования для бис пл

- •8.10. Базовые сведения о языке vhdl

- •8.10.1. Исторический обзор и проблемная ориентация языка

- •8.10.2. Базовые понятия языка и архитектура программ

- •8.10.3. Синтаксическая организация проекта

- •8.10.4. Общеалгоритмическая составляющая языка

- •8.10.5. Проблемно составляющая языка

- •8.10.6. Структурное описание

- •8.10.7. Описание поведения

- •8.11. Описание проектов на языке vhdl примеры, иллюстрирующие основные конструкции vhdl

- •8.11.1. Структурное описание

- •8.11.2. Поведенческое описание

- •8.11.3. Сравнение структурного и поведенческого способов

- •8.11.4. Описание типовых фрагментов вычислительной техники

- •8.12. Пример автоматизированного проектирования

- •Описания аппаратуры

- •8.12.1. Варианты реализации и выбор элементной базы

- •8.12.2. Проектирование бис пл

- •8.12.3.Разработка микропроцессорной системы

- •8.12.4. Особенности процедуры проектирования

- •Этап 1. Этап конфпгурпрованпя аппаратных ресурсов кристалла

- •Этап 3. Разработка программной части проекта

- •Этап 4. Кодовая симуляция и отладка

- •Этап 5. Компиляция и создание объектного кода

- •Этап 7. Загрузка проекта

- •Этап 8. Натурная отладка проекта

- •9.1. Архитектуры с разделяемой общей памятью

- •9.2. Архитектуры с распределенной областью памяти

- •9.3. Матричные системы

- •9.4. Машины, управляемые потоком данных

- •9.5. Систолические системы

- •9.6. Обобщенная архитектура параллельных систем

- •Глава 1. Основы микропроцессорной техники

- •Глава 2. Процессоры общего назначения и системы на их основе

- •Глава 4. 8-разрядные микроконтроллеры

- •Глава 5. Коммуникационные микроконтроллеры и системы на их основе

- •Глава 7.Программируемая логика и ее применение в микропроцессорных системах

- •Глава 8. Проектирование мпс

- •8.4. Средства и методы разработки программного обеспечения

- •8.4.1. Средства индивидуальных и интегрированных пакетов

- •Глава 9. Архитектуры параллельных вычислительных систем

8.12. Пример автоматизированного проектирования

ЦИФРОВОГО УСТРОЙСТВА С ИСПОЛЬЗОВАНИЕМ ЯЗЫКОВ

Описания аппаратуры

Современные методы и средства проектирования рассмотрим на примере разработки микропроцессорной системы, являющейся модернизацией более ранней разработки уст- ройства на базе микроконтроллера МСS-51 (с целью сокращения объёма примера описание будет упрощено относительно реальных условий). Переход на новую элементную базу в данном проекте прежде всего ограничивается естественным желанием проектировщика максимальным образом использовать ранее разработанные и проверенные решения, в основном это касается фрагментов программного обеспечения. В состав системы должен входить двухканальный 10-разрядный аналого-цифровой преобразователь, записывающий по запросу параллельный код в буферное ОЗУ емкостью 256 десятиразрядных слов, 8 входов и 28 выходов для дискретных сигналов. Использование схем класса СИС и МИС должно быть в модернизированном варианте минимизировано за счет использования схем программируемой логики. для определенности, кроме специально оговоренных случаев, будем ориентироваться на микросхемы программируемой логики фирмы "Altera", а вследствие этого и на САПР этой же фирмы МАХ + PLUSII.

8.12.1. Варианты реализации и выбор элементной базы

Реализация проекта возможна в различных альтернативных вариантах. Сохранение задела по программному обеспечению заставляет обратиться к вариантам, имеющим в качестве МП-ядра тот или иной вариант контроллера МСS-51.

К основным вариантам можно отнести следующие:

1) с использованием БИС класса SОРС депегiс фирмы "Altera" и мегафункции (на пример, CAST) для реализации МП-ядра;

2) с использованием БИС класса SОРС фирмы "Triscend" семейства ТЕ5, содержащей в качестве МП-ядра встроенный микроконтроллер 8052 и конфигурируемую логику типа FPGA;

3) с использованием микроконтроллера, совместимого по системе команд с МСS-51 со встроенными средствами аналого-цифровой обработки (например, БИС АDuС812 фирмы "Analog Devices" и с реализацией недостающих дискретных элементов в БИС ПЛ фирмы "Altera".

4) с использованием обычного контроллера семейства МСS-51 автономных средств аналого-цифровой обработки и размещением всей дискретной части проекта в БИС ПЛ фирмы "Altera".

Рассмотрим эти варианты более подробно.

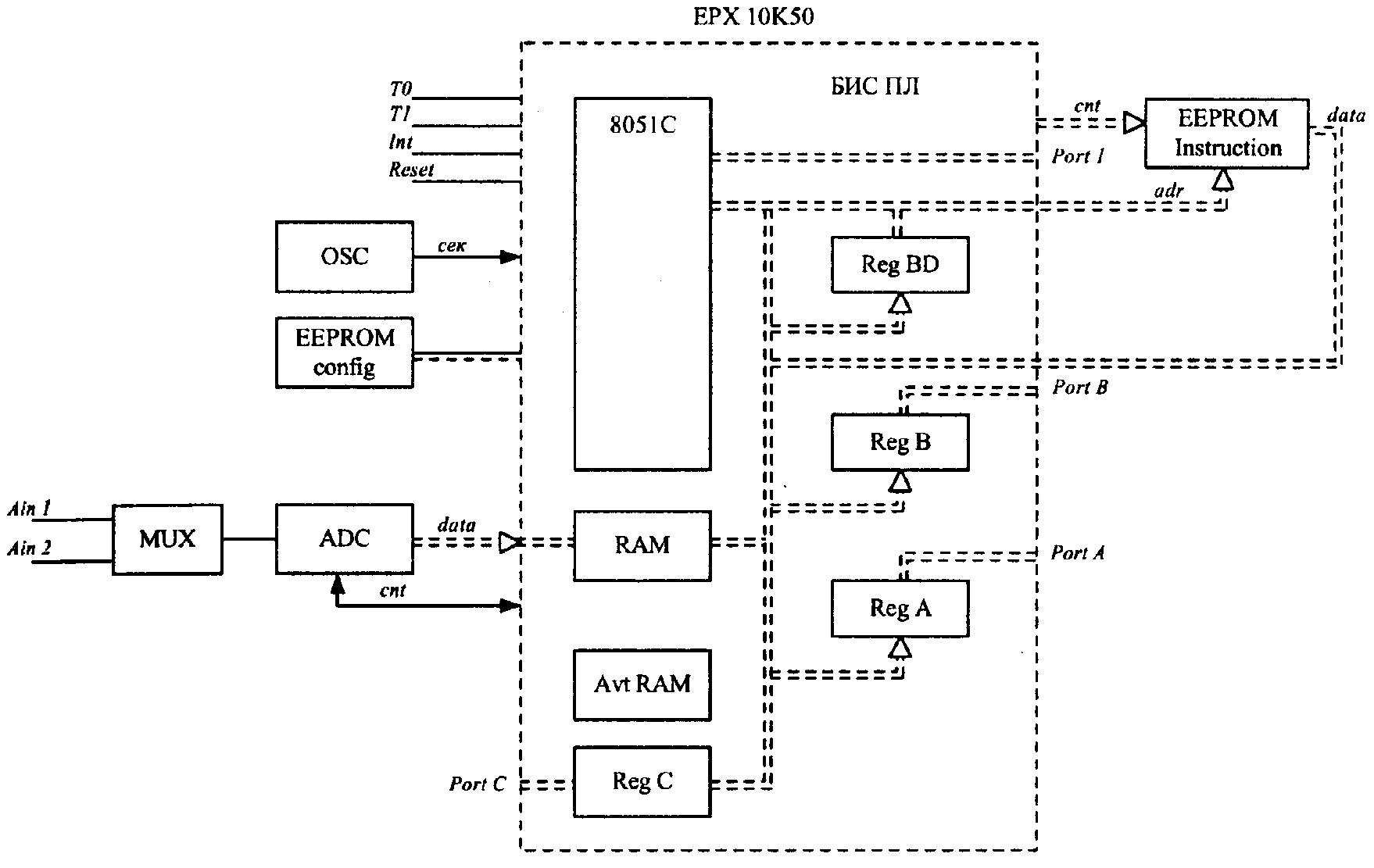

1-й вариант реализации имеет укрупненную функциональную схему, соответствующую приведенной на рис. 8.12. Основу проекта составляет БИС класса SОРС generic, конфигура- ция которой включает МП-ядро (на базе стандартной мегафункции) и требуемую дополни- тельную логику: регистры выходные (Reg_A,Reg_B,Reg_BD), входной регистр (Reg_С), буферное ОЗУ (RAM) и автомат, управляющий работой ОЗУ (АvtRАМ). Помимо БИС ПЛ схема содержит дополнительные элементы: ИС время задающего генератора (OSC), ИС ПЗУ конфигурации (EEPROM Config), ИС ПЗУ команд (EEPROM Instuction), ИС аналогового коммутатора (MUX) и ИС АЦ преобразователя (ADC). Поскольку мегафункция микроконтроллера в этом варианте реализации требует (в зависимости от скоростных требований) от 2400 до 2860 логических ячеек, то проект потребует для своей реализации БИС ПЛ класса не ниже 10К50. Стоимость таких БИС превышает 80 дол. США, поэтому вариант вряд ли экономически оправдан даже для выпуска ОПЫТНОЙ партии устройств.

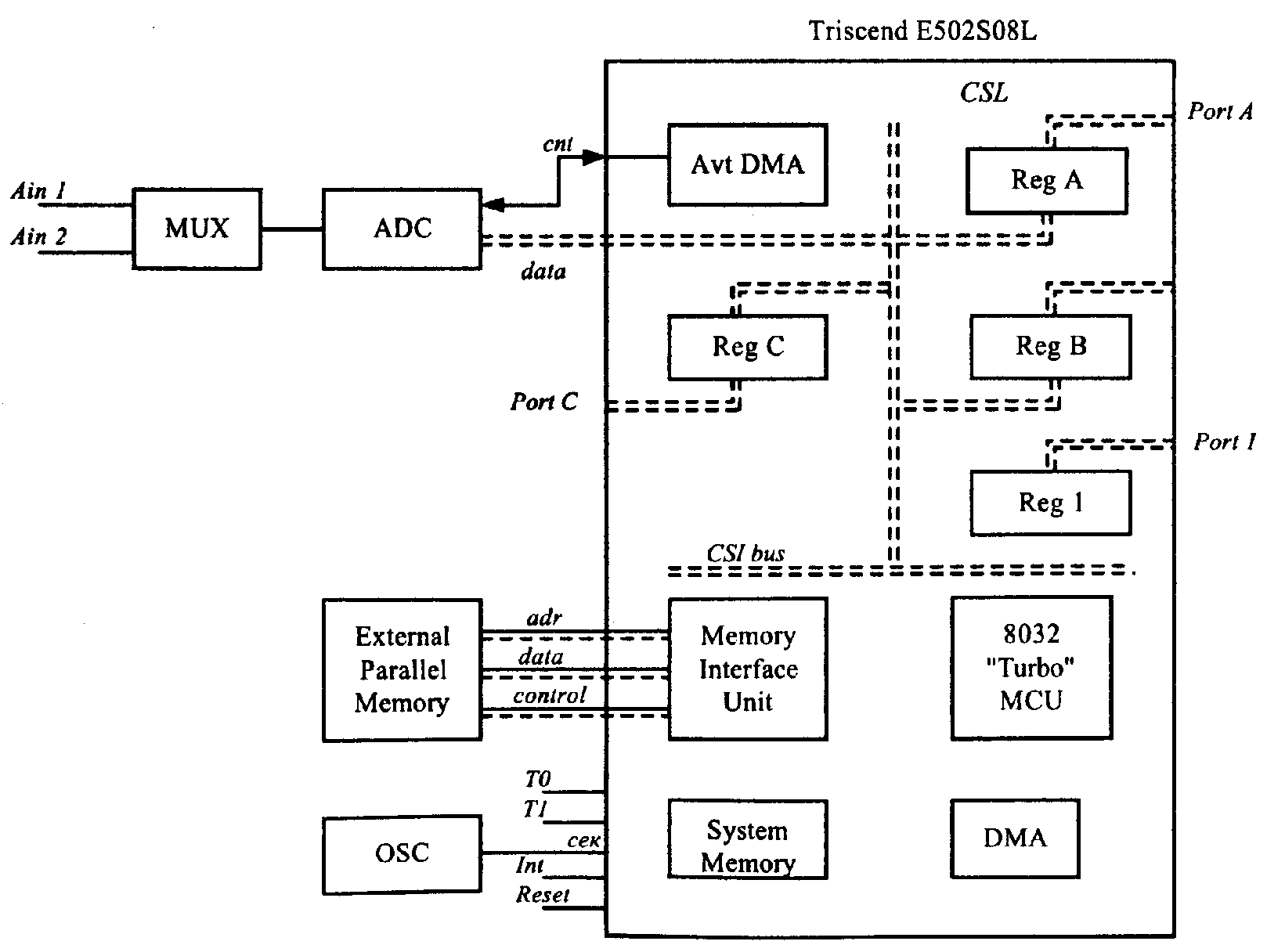

2-й вариант (рис. 8.13), опирающийся на продукцию фирмы "Triscend", потребует для своей реализации помимо БИС семейства ТЕ5 четырех схем СИС (Организация БИС семейства ТЕ5 позволяет объединить в одной БИС ПЗУ Память команд МК и память конфигурации БИС ПЛ — EEPROM). В силу специфики организации БИС семейства ТЕ5 буферизацию данных от АЦ-преобразователя необходимо ВЫПОЛНЯТЬ непосредственно в памяти данных МК и ориентироваться при этом на встроенный контроллер прямого доступа к па- мяти. Эта специфика приводит к необходимости модернизации Программного обеспечения процессорного ядра. Блоки, реализуемые конфигурируемой системной ЛОГИКИ (С31.) кристалла ТЕ5, функционально совпадают с блоками, размещенными в ВИС ПЛ предыду- щего Варианта. С экономической точки зрения, основные затраты, по-видимому, будудут касаться не столько стоимости кристаллов (стоимость БИС семейства в зависимости от тактовой частоты и числа конфигурируемых ячеек системной логики может колебаться от 18 до 100 дол. США), сколько стоимости покупки лицензии на САПР и загрузочного обору- дования, которое может достигать суммы порядка 650 дол. США (минимальные затраты около 170 дол. США).

3-й вариант реализации (рис. 8.14) является самым экономичным по числу требуемых для реализации числа микросхем. Основу схемы образуют две БИС (БИС АduC812 фирмы "Anolog Devices"и БИС ПЛ ЕРХ10K10 фирмы "Altera". БИС АduC812 фирмы "Anolog Devices" разработчики отнесли к классу микропреобразователей,поскольку БИС содержит на одном кристалле микроконтроллер, память, АЦП и ЦАП.Для реализации устройства дополнительно потребуется одна БИС конфигурационного ПЗУ (EPROM) и одна ИС времязадающего генератора (ОSС). Структура устройства, конфигурируемого в БИС ПЛ, сохраняет элементы предыдущих вариантов. Как и для предыдущего варианта реализации, использование прямого доступа к памяти потребует модернизации программного обеспечения МК. Стоимость БИС AduC812 фирмы"Anolog Devices" не превышает 12 дол.

США, но и стоимость БИС ЕРХ10K10 фирмы "Altera" близка к 20 дол. США. Приобретение

средств, сопровождающих разработку, может потребовать затрат, не превышающих

100 дол. США. Вариант имеет предопределенные характеристики по скорости работы АЦП

и экономически проигрывает следующему варианту.

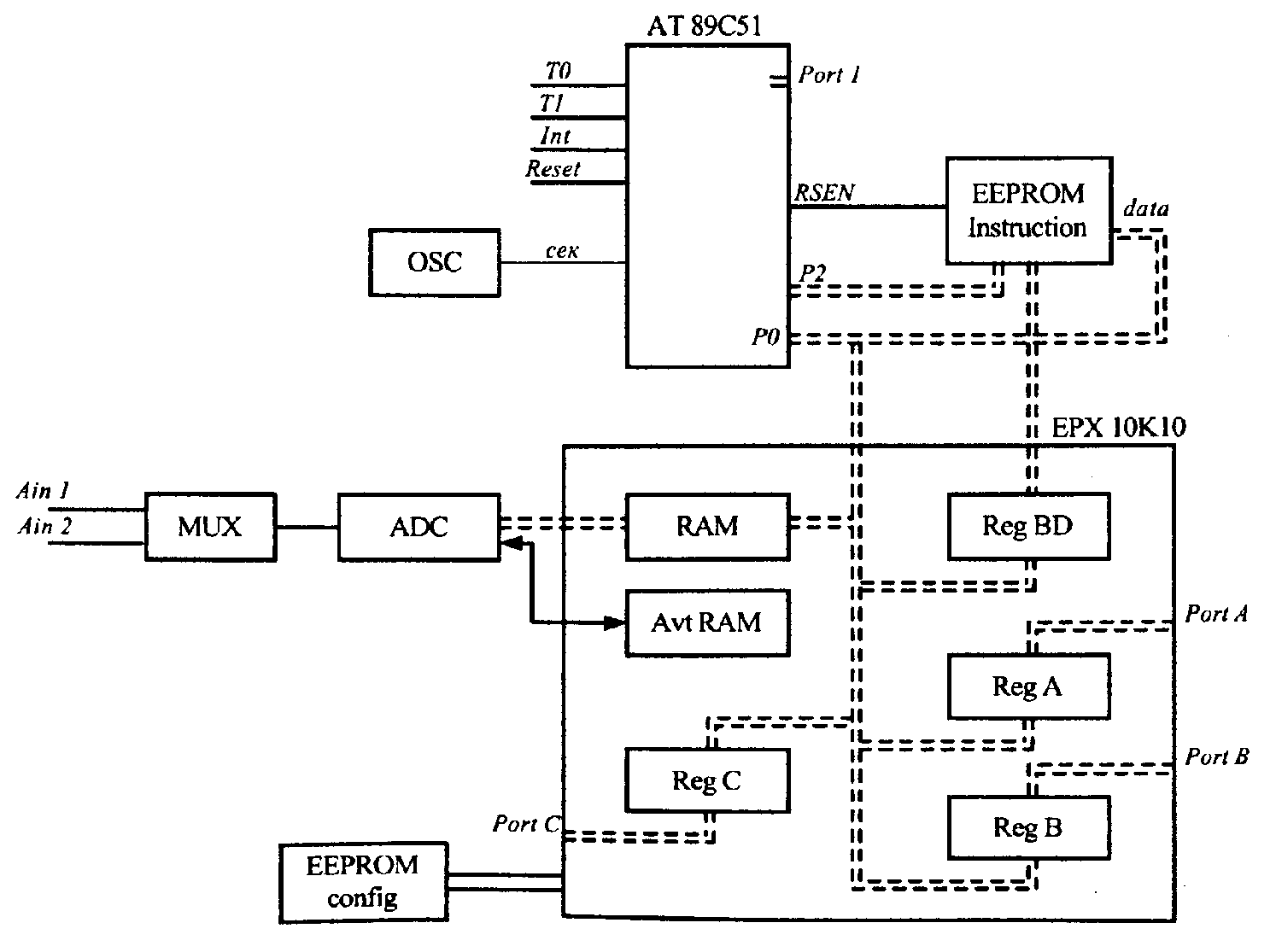

4-й вариант реализации (рис. 8.15) предполагает использование в качестве МП-ядра классической микросхемы МCS-51 (в примере БИС АТ89С51 фирмы "Atmel" и применения БИС ПЛ ЕРХ10K10 для реализации недостающих дискретных компонентов. Основным достоинством варианта является возможность без каких-либо переделок использовать старое программное обеспечение. Именно это и позволяет остановиться для дальнейшей работы на этом варианте. Выбор для реализации 2-го или 3-го вариантов целесообразен только в том случае, если разработчик готов потратить время и деньги на модернизацию программного обеспечения. В связи с наличИем целого ряда особенностей при проектировании устройства на базе БИС класса SОРС после подробного рассмотрения процедуры проектирования для выбранного варианта реализации приведем наиболее существенные отличия в проектной последовательности для реализации проекта на базе БИС фирмы "Triscend".

После выбора варианта реализации устройства в целом можно переходить к детализации технического задания на проектирование БИС ПЛ.

Рис. 8.12. Вариант реализации проекта на БИС ПЛ класса SОРС generic

Рис.8.13. Вариант реализации проекта на БИС ПЛ класса SОРС ТЕ5

Рис.8.14. Вариант реализации проекта на БИС АDuC812 и БИС ПЛ ЕРХ10K10

Рис.8.15. Вариант реализаци. и проекта на БИС АТ89С51 и БИС ПЛ ЕРX10K10