Электроника 2.1 / Лабы / триггеры

.docxМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное автономное образовательное учреждение высшего образования

«НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

ИШЭ

13.03.02 «Электроэнергетика и электротехника»

Отчёт по лабораторной работе

«Исследование триггеров на интегральных микросхемах»

Выполнил: студент группы 5А6Б __________________ Кошкин Д.Р.

(подпись) ____________

(Дата)________

Проверил: доцент ОЭЭ __________________Чернышев И. А.

(подпись) ____________

(Дата)________

Томск – 2018

Цель работы: экспериментальное исследование работы триггеров, выполненных на интегральных микросхемах, и закрепление знаний по последовательности логике.

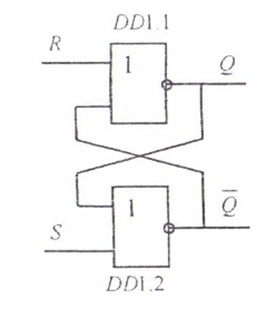

RS – триггер на элементах ИЛИ-НЕ.

Рисунок

1 - RS-триггер

на элементах ИЛИ-НЕ.

Рисунок

1 - RS-триггер

на элементах ИЛИ-НЕ.

Таблица 1. Состояние RS-триггера на элементах ИЛИ-НЕ

|

Режим работы |

Теория |

Эксперимент |

|||||||

|

|

|

|

|

|

|

|

|

||

|

Запрещенное состояние |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

|

|

Установка 1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

Установка 0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

Хранение |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

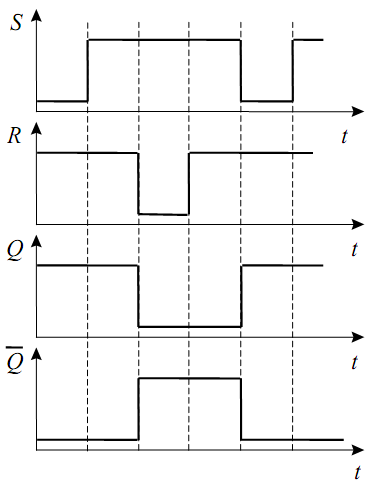

Рисунок

2 - Временные диаграммы для RS-триггера

на элементах ИЛИ-НЕ.

Рисунок

2 - Временные диаграммы для RS-триггера

на элементах ИЛИ-НЕ.

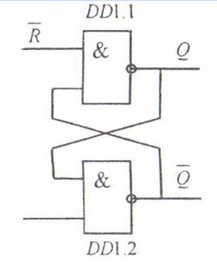

RS – триггер на элементах И-НЕ.

Рисунок

3 - RS

триггер на элементах И-НЕ.

Рисунок

3 - RS

триггер на элементах И-НЕ.

Таблица 2. Состояния для RS-триггера на элементах И-НЕ

|

Режим Работы |

Теория |

Эксперимент |

|||||||

|

|

|

Q |

|

|

|

Q |

|

||

|

Запрещенное состояние |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

Установка 1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

Установка 0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

|

Хранение |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

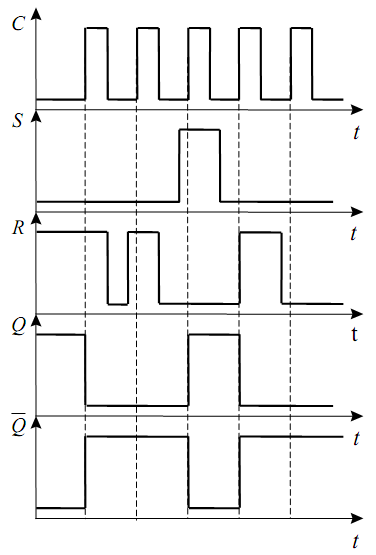

Рисунок

4 - Временные диаграммы для RS-триггера

на элементах И-НЕ.

Рисунок

4 - Временные диаграммы для RS-триггера

на элементах И-НЕ.

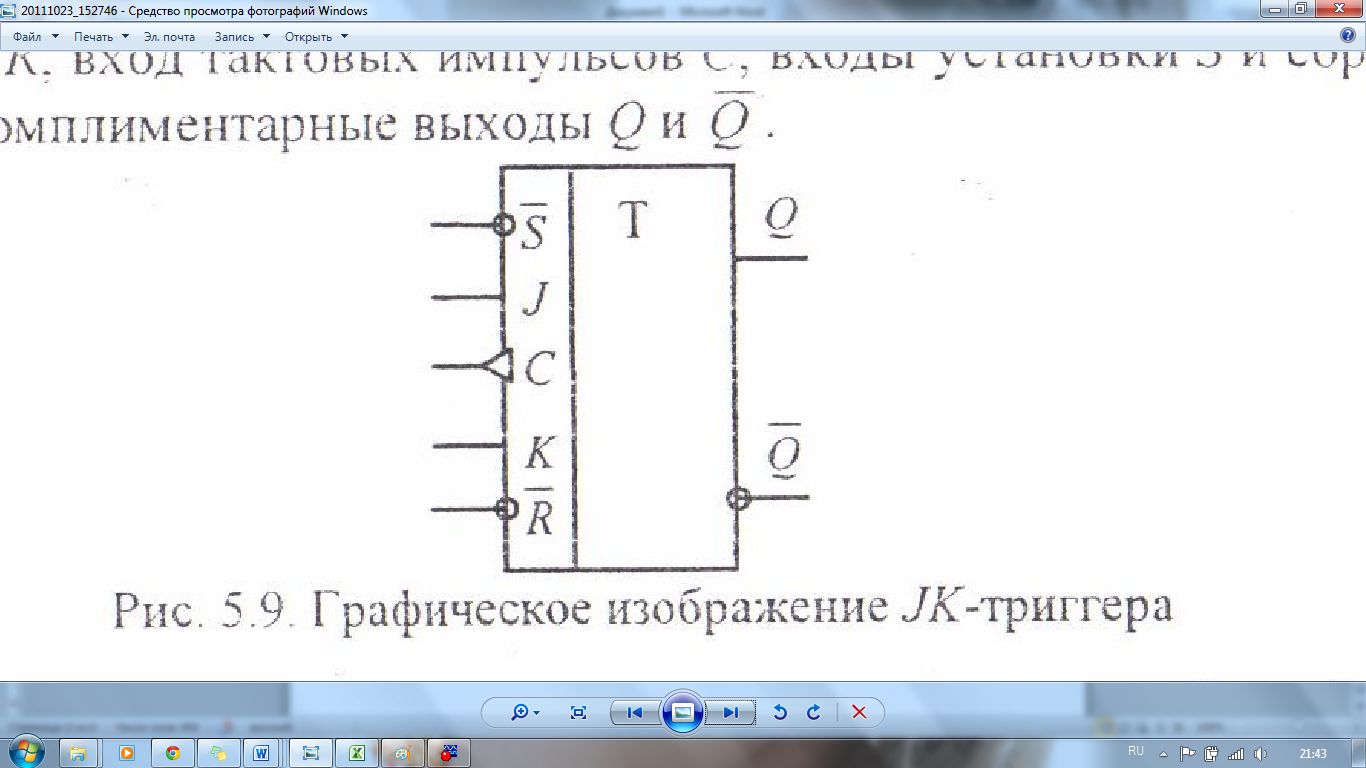

JK– триггер

Рисунок

5 - Условное графическое изображение

JK-триггера.

Рисунок

5 - Условное графическое изображение

JK-триггера.

Таблица 3. Состояния для JK-триггера

|

Режим Работы |

Теория |

Эксперимент |

||||||||||

|

J |

K |

C |

Q |

|

J |

K |

C |

Q |

|

|||

|

Запись 1 в JK-триггер |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

0 |

||

|

Запись 0 в JK-триггер |

0 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

||

|

Триггер не меняет состояния |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

||

|

Триггер меняет состояние на инверсное |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

0 |

||

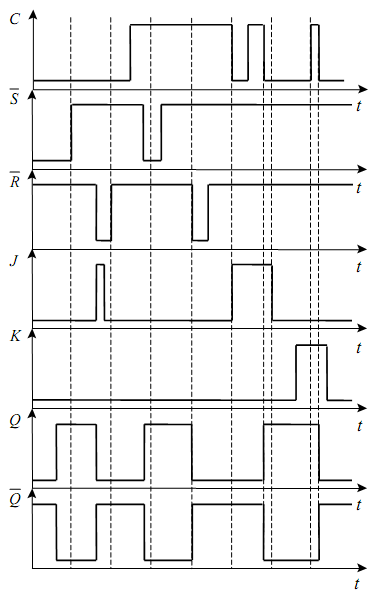

Рисунок

6 - Временные диаграммы для JK-триггера.

Рисунок

6 - Временные диаграммы для JK-триггера.

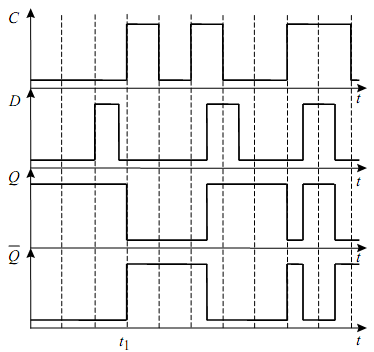

D-триггер.

Рисунок

7 - Условное графическое изображение

D-триггера.

Рисунок

7 - Условное графическое изображение

D-триггера.

Таблица 4. Состояния для D-триггера

|

Режим работы |

Вход |

Выход(теория) |

Выход(эксперимент) |

|||||||

|

|

|

C |

D |

Q |

|

Q |

|

|||

|

Асинхронная установка |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

||

|

Асинхронный сброс |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

||

|

Неопределенность |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

||

|

Установка 1 |

1 |

1 |

|

1

|

1 |

0 |

1 |

1 |

||

|

Установка 0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

||

Рисунок

8 - Временные диаграммы для D-триггера

Рисунок

8 - Временные диаграммы для D-триггера

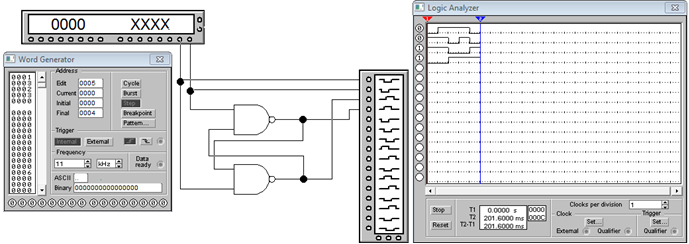

Выполнение работы в Electronic Workbench

RS-триггер на элементах И-НЕ в программе Electronic Workbench

Рисунок 13 - Схема тестирования RS – триггера на логических элементах И НЕ впрограмме Electronic Workbench

Вывод: Экспериментальные данные совпадают с теоретическими, триггер работает нормально. Как следует из графического изображения триггера и временных диаграмм его работы, входы S и R с активным низким уровнем. Когда на один из этих входов подан сигнал низкого уровня информация со входов C, J и K восприниматься не будет, т. е. входы S и R имеют приоритет над остальными входами. Информация со входов J и K записывается в триггер в два приема фронтом и срезом положительного тактового импульса по входу С. Входы S и R являют приоритетными. Нулевой сигнал на входе S устанавливает выход Q в единичное состояние в независимости от уровней сигналов на J, K и С входах. При S=R=1 разрешается синхронное управление по J и K – входам. Вход J устанавливает на выходе Q сигнал, равный 1, а вход К равный нулю. Отличие JK – триггера от синхронного RS – триггера состоит в том, что отсутствуют запрещенные входные комбинации. При подаче на оба входа J и К сигнала равного 1, триггер изменяет свое состояние на противоположное по срезу сигнала на входе С.