- •1. Триггеры. Виды триггеров. Функциональные схемы. Переключательные функции. Временные диаграммы.

- •3. Мультиплексоры. Виды мультиплексоров. Функциональная схема матричного мультиплексора. Вывод переключательной функции.

- •4. Демультиплексоры. Виды демультиплексоров. Функциональная схема матричного демультиплексора. Вывод переключательной функции.

- •5. Суммирующий счетчик. Основные особенности построения счетчика. Функциональная схема трехразрядного суммирующего счетчика. Таблица соответствия.

- •6. Вычитающий счетчик. Основные особенности построения счетчика. Функциональная схема трехразрядного вычитающего счетчика. Таблица соответствия.

- •7. Реверсивный счетчик. Основные особенности построения. Функциональная схема трехразрядного реверсивного счетчика.

- •8. Запоминающие устройства эвм. Основные характеристики. Зу с ассоциативной адресацией.

- •9. Запоминающие устройства эвм. Основные характеристики. Зу с непосредственной адресацией.

1. Триггеры. Виды триггеров. Функциональные схемы. Переключательные функции. Временные диаграммы.

Триггер – это элементарная ячейка памяти которая может хранить только два состояния 0-ль либо 1-а, причем переход из одного состояния в другое происходит скачком, и состояние триггера определяет уровень сигна-ла на прямом выходе.

Триггеры бывают:

- RS – триггер;

- Т – триггер (счетный);

- D – триггер (с задержкой времени);

- JK – триггер (универсальный);

Обозначение входов триггеров: вход R – производит установку RS – триггера в нулевое состояние; S – производит установку RS – триггера в единичное состояние; T – счетный вход Т – триггера; D – вход задержки D – триггера, информационный вход; J – вход синхронной установки JK – триггера в нулевое состояние; K – вход синхронной установки JK – триггера в единичное состояние; C – вход синхронизации, если «С» отсутствует, или не задействован, то триггер является асинхронным; V – управляющий вход триггера;

Построение RS – триггера

Карта Карно

Карта Карно

![]()

![]()

Счетные Т-триггеры:

Данный вид триггеров реализует функцию сложения по модулю 2-а, а также на каждые 2-а входных сигнала на счетном входе «T» получаем один выходной сигнал.

Схема асинхронного, двухтактного T – триггера:

D – триггер (триггер с задержкой по времени):

Асинхронные

D –триггеры

Асинхронные

D –триггеры

являются повторительными, поэтому для практической реализации функции с задержкой времени используются однотактные и двухтактные D –триггеры.

Управление ведется

по переднему фронту единичного сигнала

входа синхронизации. Максимальная

задержка сигнала однотактного D –

триггера на выходе

![]() сигнала на входе. Двухтактный синхронный

D – триггер отличается от однотактного

тем, что задержка по времени на Т.

сигнала на входе. Двухтактный синхронный

D – триггер отличается от однотактного

тем, что задержка по времени на Т.

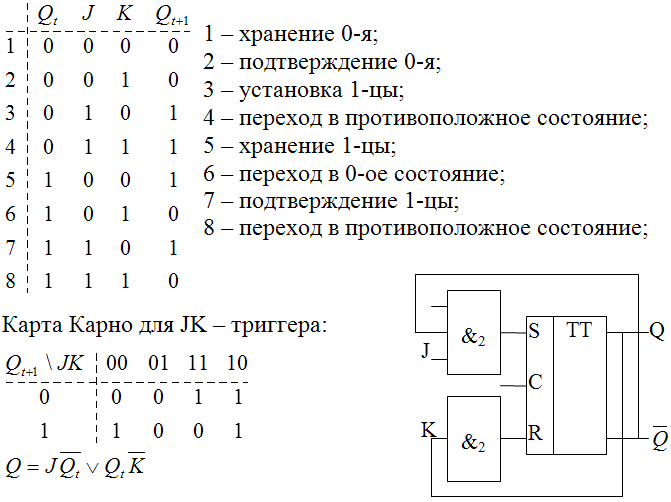

JK – триггер (универсальный)

Может реализовывать все функции предыдущих триггеров. Главное отличие JK – триггера: не имеет запрещенных состояний.

Сигнал на выходе триггера в последующий момент времени изменяется на противоположный, если J=1, или равен предыдущему если K=0, если J=K=1, то триггер работает в режиме счетного триггера, если размыкается обратная связь, то триггер работает в режиме синхронного RS – триггера, если на J и K одновременно подавать противоположные сигналы, то триггер работает в режиме D – триггера.

Незадействованные входы элементов & являются свободными для наращивания схемы.

2. Дешифраторы. Виды дешифраторов. Функциональная схема пирамидального дешифратора на элементах И. переключательные функции для каждого выхода.

Шифраторы – преобразуют сигнал на одном из своих кодов (унитарный код) в n-разрядный 2-ичный код на выходе, соответствующий 10-ичному номеру активного входа.

Число информационных

входов шифратора равно числу символов

преобразуемого кода и должно соответствовать

условию

![]() ,

где n – число информационных выходов.

,

где n – число информационных выходов.

При n=3, структурную схему шифратора можно изобразить следующим образом:

Дешифратор – представляет собой комбинационное устройство, позволяющее распознавать числа, представленные позиционно n-разрядным кодом.

Если на вход дешифратора подать n-размерный 2ый код, то на выходе устройства появляется код «1 из N» в кодовой комбинации которого только одна позиция будет представлена единицей, а остальные – нулем. Такой код называется унитарным.

Т.к. макс. возможное

количество чисел, закодированные

N-разрядным 2чным кодом = количеству

наборов из N аргументов (![]() ),

то д., имеющий n входов, может иметь

выходов:

),

то д., имеющий n входов, может иметь

выходов:

![]() .

.

![]() - полный д.

- полный д.

![]() - неполный д.

- неполный д.

Для n=3 структурная схема д. в базисе элементов и-не имеет вид: